Allegro PCB Design Planning Option

与总线相关的高速约束、高密度设计需要花费大量时间进行规划和布线。与当今器件的高密度问题结合,产生了新信号等级和特殊的拓扑需求,毫无疑问,传统CDA工具和技术已不能满足设计的需求。全局布线环境(GRE)提供了新的技术和解决方案,同时满足了设计意图。通过互连流程设计体系和全局布线引擎,用户将试验和设计意图放入一个工具中,此工具可以按照设计者意图进行工作。

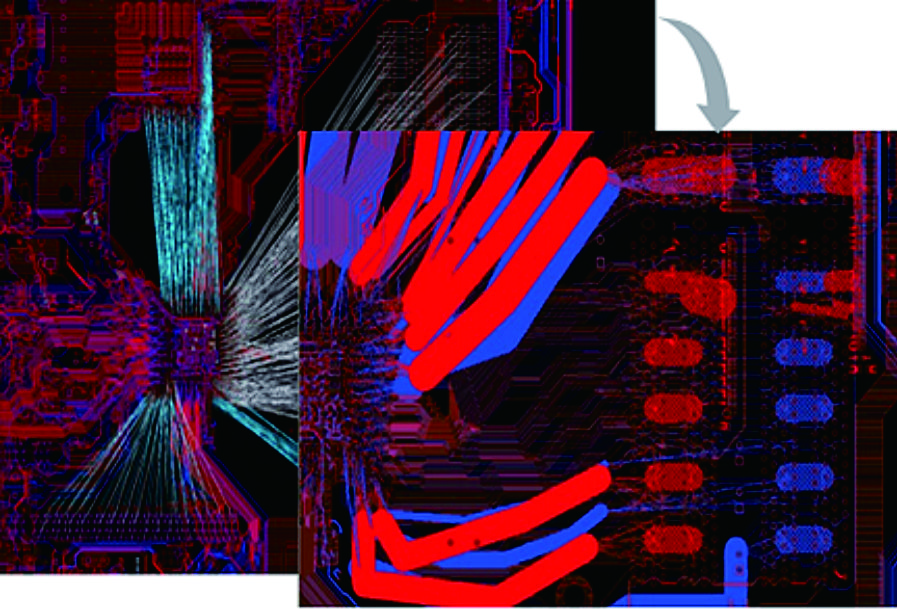

用户创建抽象的互连数据(通过互连流程设计体系创建),通过全局布线引擎能够快速找到解决方法并进行验证。互连体系减少了系统需要处理的数据量-从上万数据降到几百数据-明显的减少了人工工作量。应用抽象数据,通过提供与数据和设计意图相关的可视的/立体的图s表,设计和布线进程被加速,布线引擎将自动处理布线过程中的细节问题,同时满足特殊设计意图,而不需要设计人员同时查看和解决布线中的问题。

这一重要的将设计简单化的工具意味着用户找到了一个成功的快速且简便的解决方法,提高了设计效率和生产率,缩短了设计周期。(图2)

图2:Allegro interconnect Flow Planner技术允许用户使用通过设计规划,减少层数,缩短设计周期

AiBT

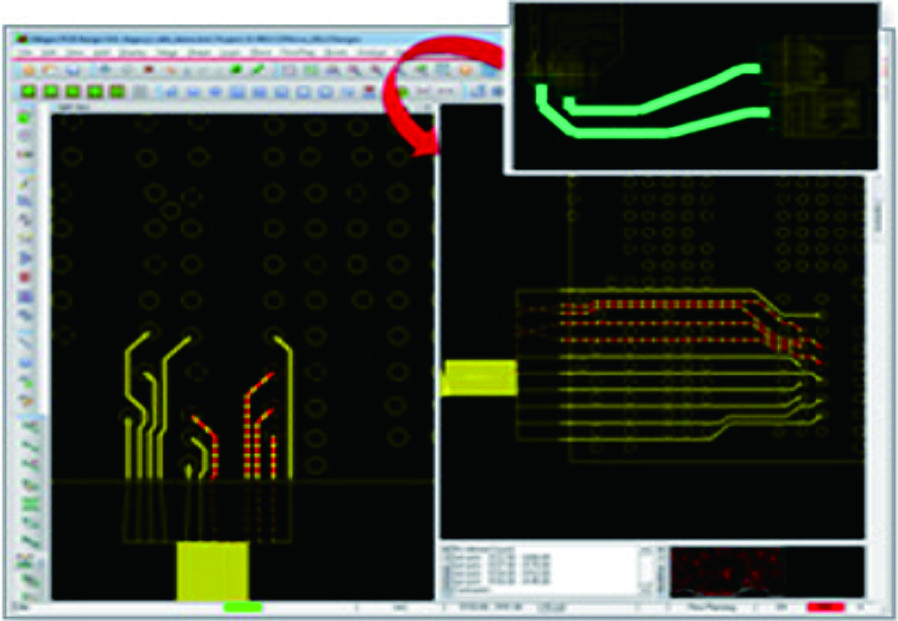

自动-交互式 Breakout 技术(AIBT)允许用户从头至尾的规划信号走线,提高用户设计效率。AiBT可以被用于设计新的,分割Bundle信号簇的顺序动态调整,,以此来实现更高质量更合适的缩短走线时间。(见图3)。

图3:分屏视图允许在两端工作放大界面