Sigrity X Platform 25.1

通过直观易用的平台,开启 PCB 和 IC 设计中的信号完整性与电源完整性未来

概述

借助 Sigrity X 重新定义信号完整性与电源完整性分析

借助 Sigrity X 平台迈向未来 —— 创新与优化在此交融。为您的 PCB 和 IC 封装设计开启 实现完美信号完整性与电源完整性的关键之门,远超当前 SI / PI 技术的局限。试想,您能轻 松应对电子设计的复杂难题,不仅能达成产品上市时间目标,更能精准且从容地突破这一目标。 借助 Sigrity X,您所使用的绝非普通工具;它能让您在 Allegro X PCB 与 IC 封装平台内, 开启无缝的设计中分析协同模式。您可深入使用一套全面的工具套件,其中包括信号完整性/ 电源完整性分析、 设计中互连建模以及电源分配网络(PDN)分析工具 —— 这些工具旨在大幅提升您的设计效率,确保您的项目不仅能按 期完成、控制在预算内,更能超出预期。 借助 Sigrity X 平台的强大功能,让您的下一个设计实现出色性能与可靠品质。

Sigrity X Platform

面向 PCB 与 IC 封装设计的端到端 SI/ PI 分析平台

主要优势

将设计效率提升 10 倍,助力实现产品上市时间目标

无可匹敌的性能

体验高达 10 倍的性能提升,助力您高效满足产品上市时间要求。

更高精度

Sigrity X 平台的先进算法可实现精准的 SI/ PI 分析,在满足项目进度要求的同时,还能将 PCB 或 IC 设计的迭代次数提升 3 倍。

设计中分析

通过与 Allegro X 设计平台及 Allegro X 高级封装设计平台实现无缝集成,轻松应对复杂的仿真工作。

应用

应对 PCB 和 IC 封装设计的 SI/PI 分析挑战

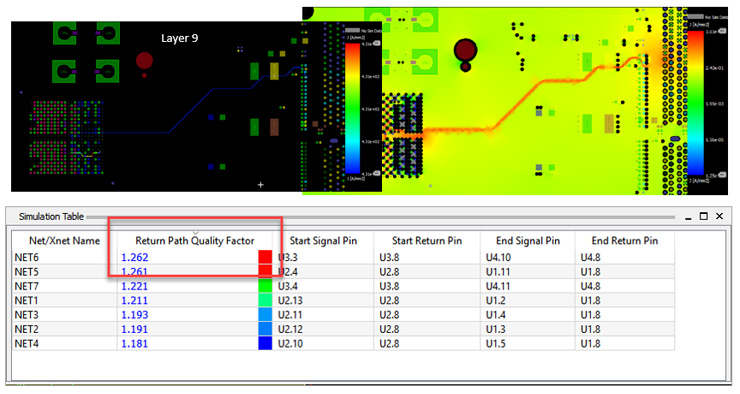

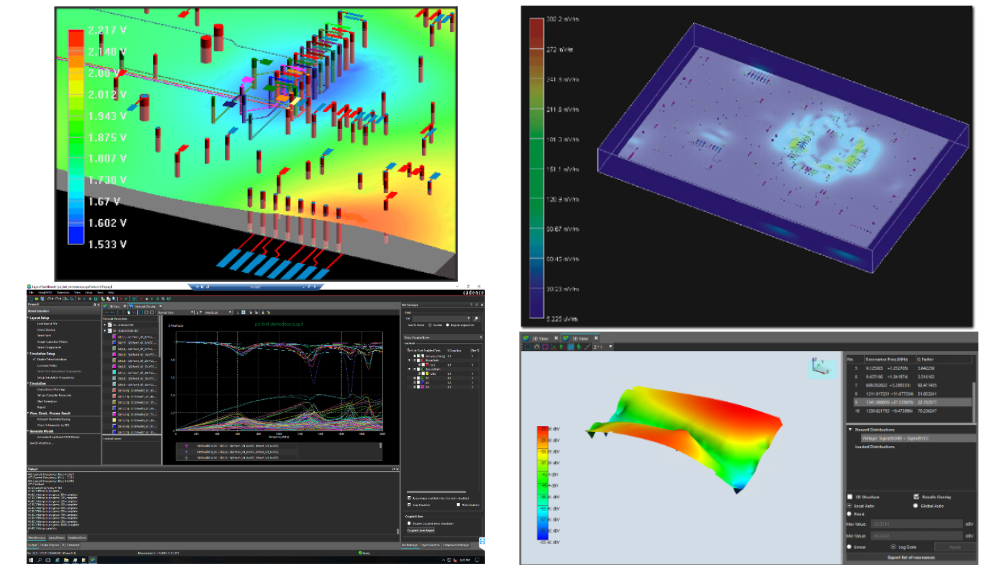

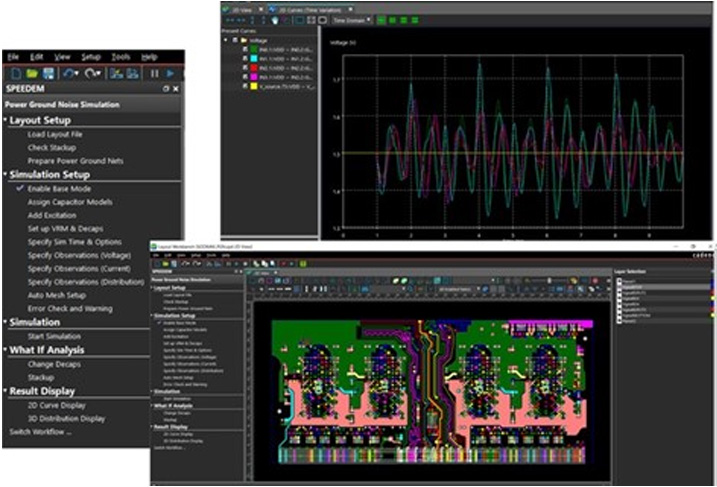

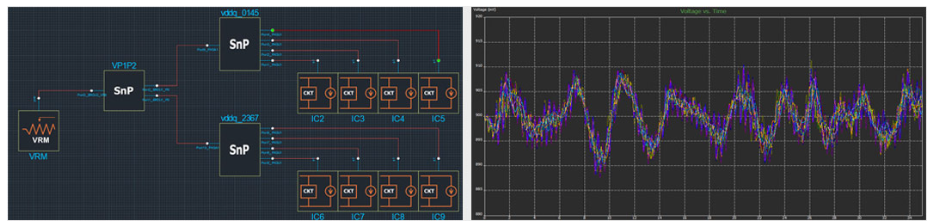

借助 Sigrity X 平台,体验 PCB 设计中无可匹敌的效率与精度,该平台在整个设计周期内提供全面的信 号完整性与电源完整性分析。Sigrity X 与 Allegro X 设计平台实现无缝集成,支持设计中分析,从而提升生产效率、减少 人工误差,并快速解决电气问题。Sigrity X 采用强大的分析引擎与直观的方法体系,通过基于 SPICE 的仿真器、嵌入式混合场求解器以及功耗感知型 IBIS 模型,在 Allegro X 环境内直接提供仿真结果。这种支持可确保在布局前与布局后阶段均能开展全面的高速信号分析,助力实现回流路径流程、直流电源完整性(DC PI)分析,并能在设计画布上直接可视化关键指标。凭借 Sigrity X 的专业级功能,提升您的 PCB 设计流程

用户认可

听听客户怎么说

功能

从容设计,提升性能

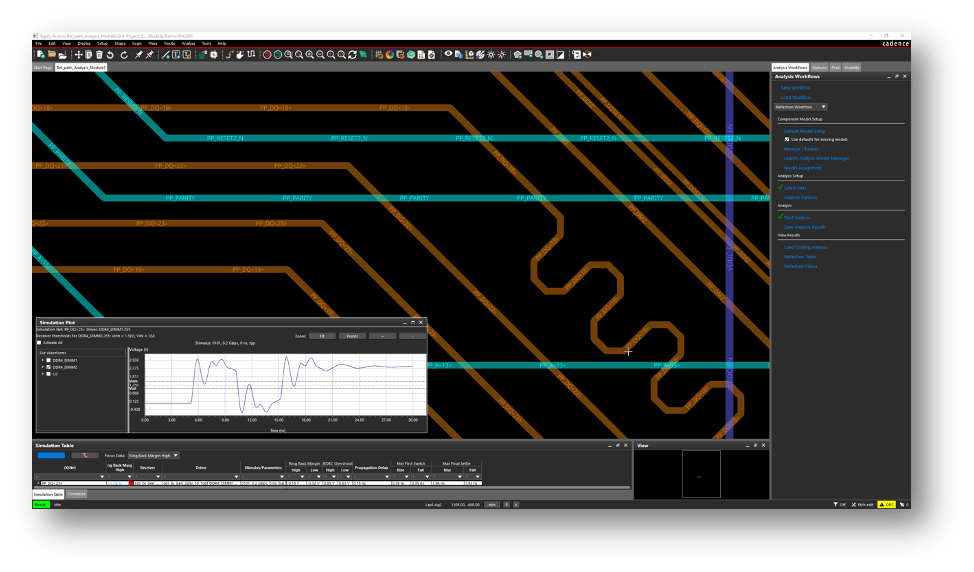

分布式仿真

借助 Sigrity X 的分布式仿真技术,彻底变革您的设计周期:该技术能最大化核心利用率,并利用多台计算机进行仿真,在与传统 “最坏情况” 简化仿真相同的时间内,完成对整个信号组的仿真。这一创新功能可确保实现全面分析,识别串扰或 同步开关噪声等关键问题,并增强对原型就绪度的信心。凭借 10 倍速的仿真效率、更短的设计周期以及更高的项目质量, Sigrity X 能助您高效满足紧张的项目进度要求。

产品

精准高效的信号完整性 / 电源完整性(SI/PI)分析,助力满足高速电子产品的紧迫交付周期

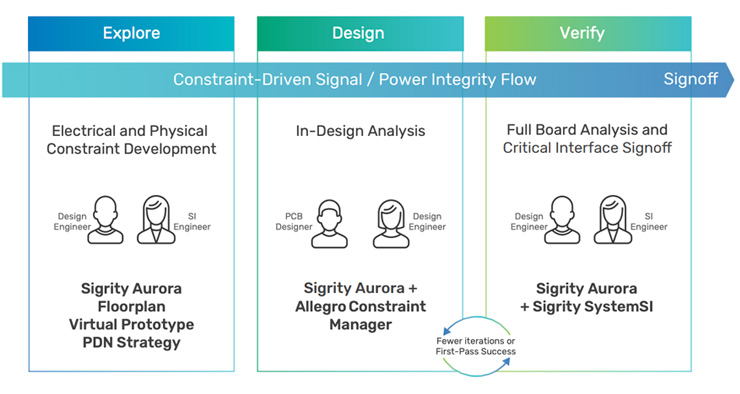

Sigrity X Aurora 与所有 Allegro X 平台深度集成,能助力设计人员尽早快速检测并修正信号与电源完整性问题,无需 专业人员进行人工检查,确保项目如期推进且不超出预算。这种无缝的设计中分析方法,在设计的每个阶段都支持全面的 信号与电源完整性分析,可实现精准的 “假设分析”(“what if”)场景规划,从而设定准确的设计约束条件,减少设计 迭代次数。

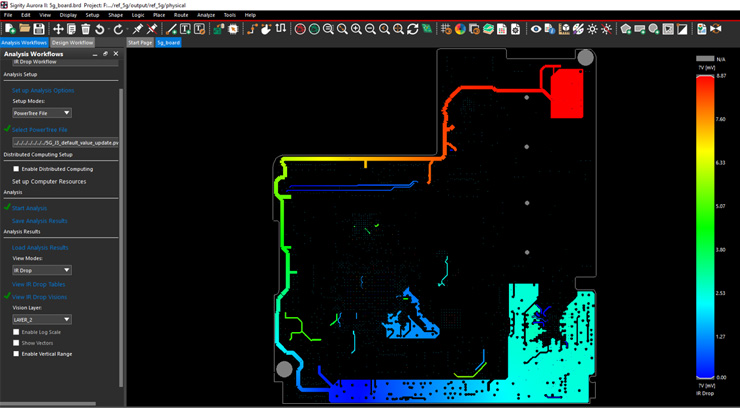

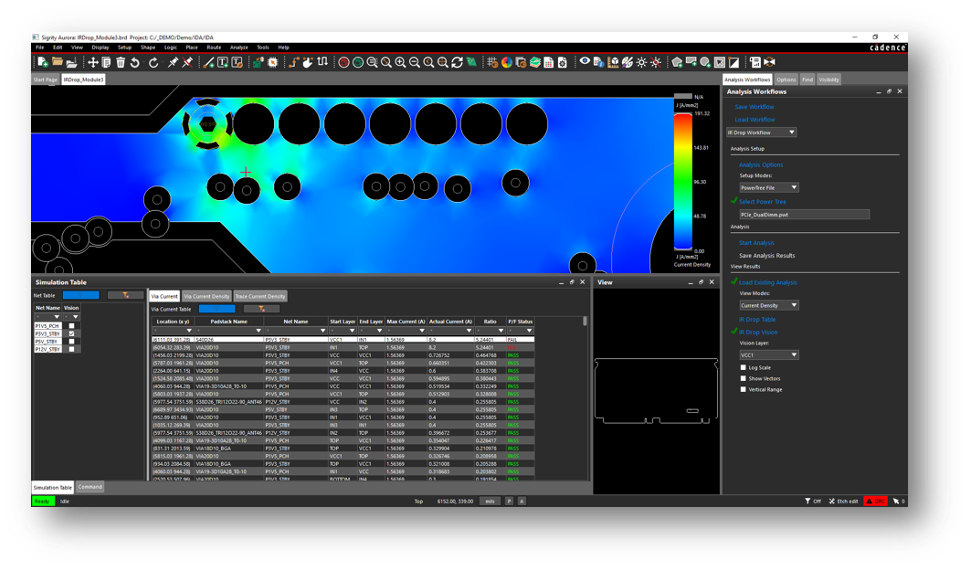

✓ 测量电源端(source)与负载端(sink)之间的任意电压降,并在设计画布上以电压、电压降或电流密度的形 式将结果可视化呈现。

✓ 在保持 Sigrity X 工具一贯著称的可靠准确性的同时,实现 10 倍性能提升,助力产品按时、在预算内交付。

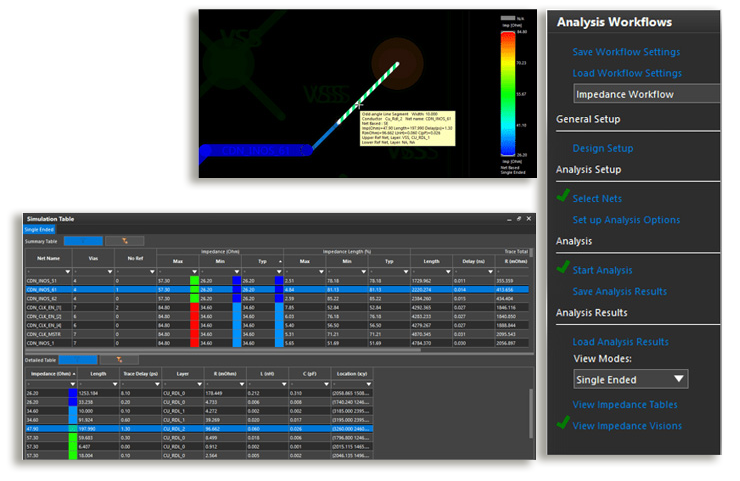

✓ 设计工程师与布局设计师可在其桌面端直接使用 Sigrity X Aurora PCB 分析功能,结合实时设 计修改,让分析结果能够直接转化为可执行的操作。

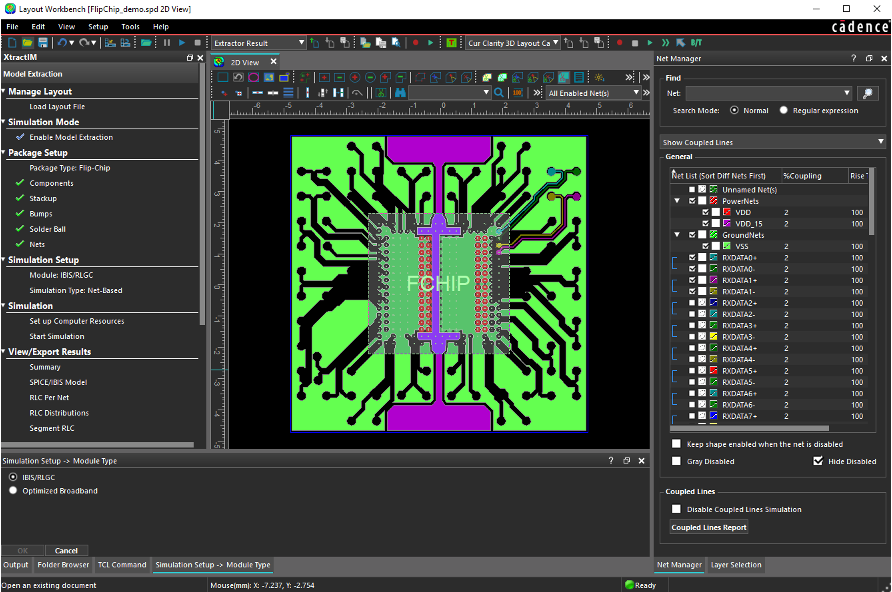

✓ 在 Allegro X 高级封装设计器(Allegro X Advanced Package Designer)中搭建设计,以开展全封装反射与串 扰仿真,同时进行互连提取、材料与横截面细节设置、直流网络识别、默认及特定仿真模型配置,以 及差分对管理。

✓ 通过支持分布式计算、全自动端口定义与去嵌入,以及具备查看 3D 几何结构和 S 参数的能力,简化全波 3D 互连模型提取流程。

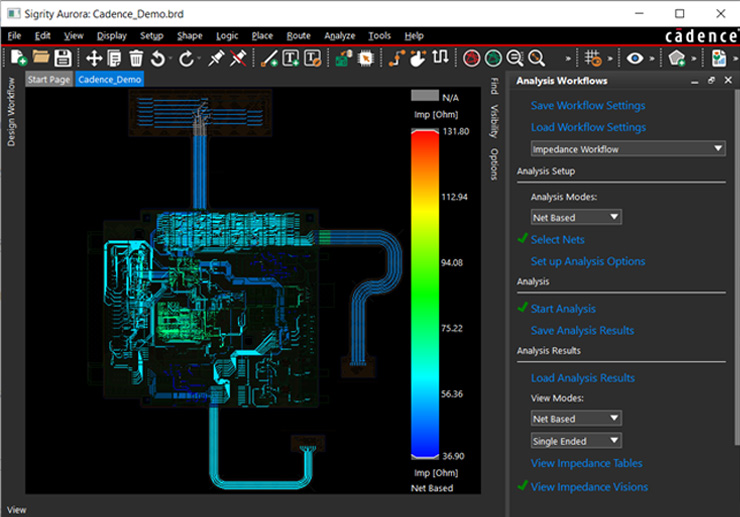

✓ 分析筛选项:阻抗、耦合、反射、串扰、电压降(IR drop)等。

功能

印刷电路板(PCB)与集成电路(IC)封装的设计前、设计中及设计后信号完整性与电源完整性分析

借助我们为高速电子产品量身打造的全方位解决方案,可实现精准的信号完整性与电源完整性分析,并满足紧迫的交 付期限。在紧凑的项目周期内,以无可比拟的效率交付具备卓越性能与可靠性的产品。

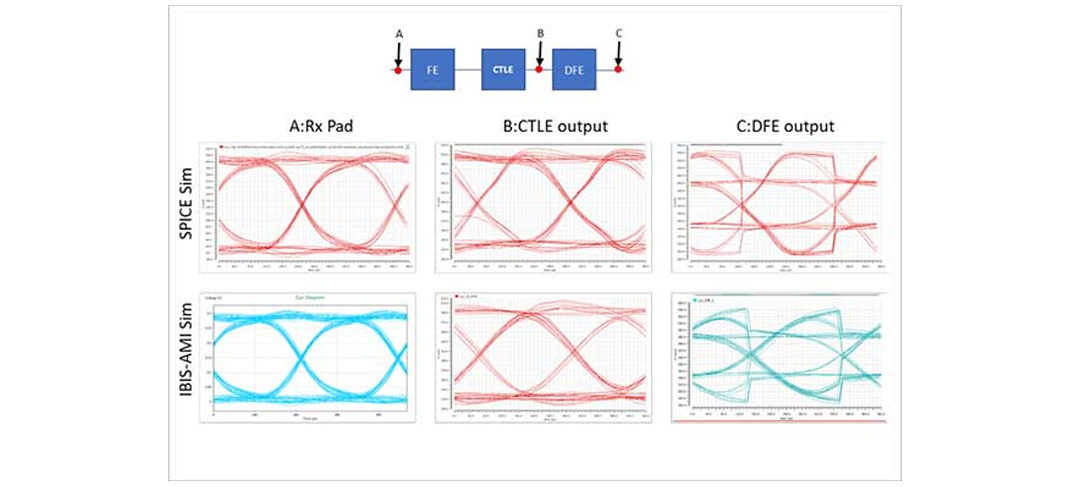

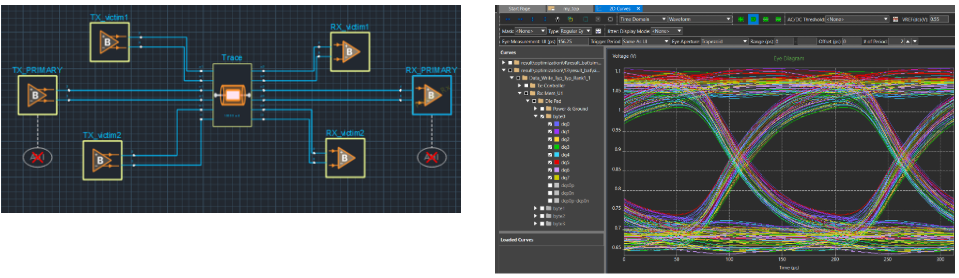

面向前沿 DDR5 和 112G 接口、具备功耗感知能力的高精度信号完整性(SI)分析,融合先 进互连建模与时域仿真,可实现全面的串列器 / 解串器(SerDes)分析及接口合规性签核。

提供更快的界面、可自定义的主题、上下文相关菜单以及统一的工作流程,所有功能均整合在 单个.spd 文件中,以提升易用性和效率。

Sigrity X 能够显著提升集成电路(IC)封装与印刷电路板(PCB)仿真的速度和精度。借助分 布式计算与代码优化技术,其性能提升幅度可达 7.18 倍至 15.1 倍,且全程不影响仿真精度。

借助 Sigrity X 经实践验证的仿真精度,并无缝利用电磁(EM)分析,提前发现电气问题,从 而交付按时、按预算的产品。

集成到高效且精准的 Allegro X 设计流程中,借助可视化功能可早期识别信号完整性与电源完 整性问题,从而减少分析和布局迭代次数,加快产品上市时间。

支持微软 Windows 和 Linux 的多系统适配

可对接来自 Cadence(楷登电子)、Mentor Graphics(明导图形)、Altium(奥腾)、 Zuken(图研)及 AutoCAD(欧特克)的印刷电路板(PCB)与集成电路(IC)封装布局数 据。

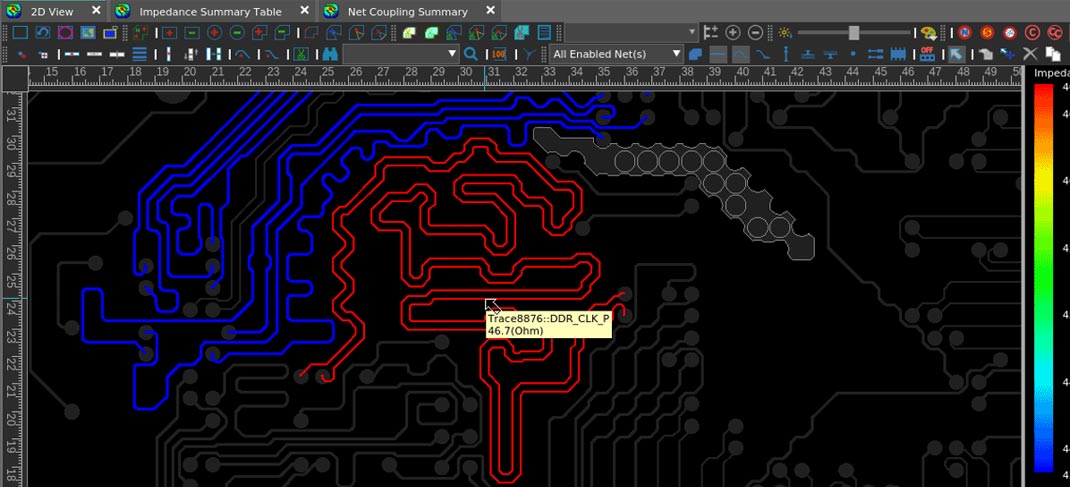

该分析筛选功能无需使用信号完整性(SI)模型,可通过直观的图形叠加层、表格和图表提供 全面的全局视图。用户能轻松对结果进行排序,从而快速识别并处理异常值。

耦合分析筛选功能可快速扫描设计,排查信号间存在过度耦合的情况,并通过图形、表格及图 表呈现结果的全局视图。

借助信号完整性(SI)模型对选定信号进行仿真,使设计人员能轻松对结果进行排序,并基于 各类信号质量指标分析异常值。同时,该功能还具备增强型能力,例如支持详细波形查看、批 量仿真、信息丰富的提示框,以及可灵活选用默认或自定义输入 / 输出(I/O)模型。

串扰分析功能允许设计人员使用默认输入 / 输出(I/O)模型或特定输入 / 输出(I/O)模型, 识别受扰串扰网络(victim crosstalk nets)以及单个干扰源(aggressors)和最差情况干扰 源。

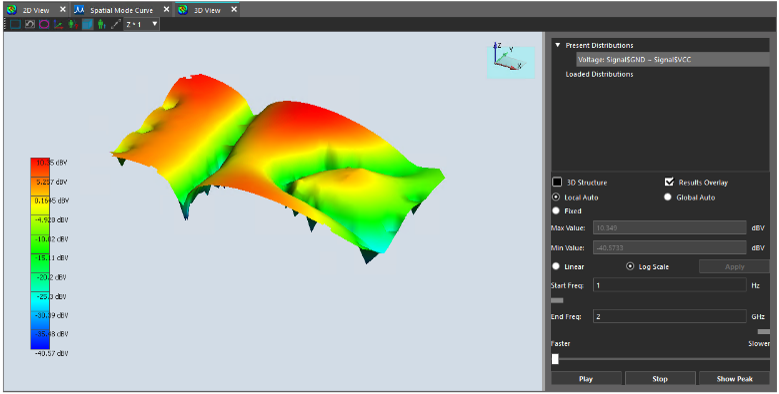

电压降(IR Drop)分析功能提供电压降、绝对电压、电流密度及电流四种视图模式,同时还 支持电流矢量、非理想接地,以及合格 / 不合格(Pass/Fail)约束条件设置。

准确处理非理想供电系统对信号完整性(SI)的影响。