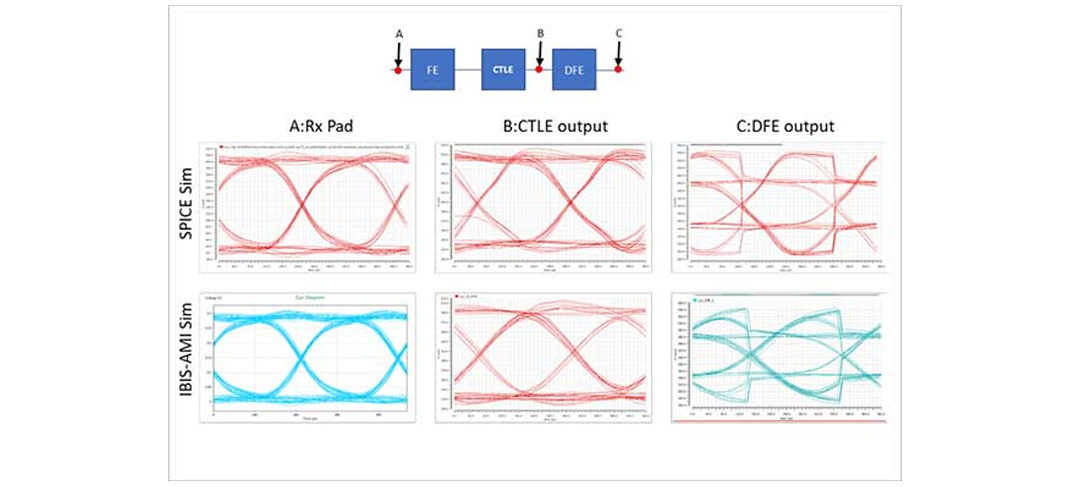

Sigrity X IBIS 建模功能可借助功耗感知型 IBIS 模型、百万比特通道仿真以及 IBISAMI 模型创建,实现对高速接口的精准仿真,确保为复杂拓扑结构提供 详尽且高效的仿真结果。该功能与 Sigrity X 高级信号完整性技术及 Sigrity X Aurora技术深度集成,支持 对串行链路和并行总线拓扑结构进行无缝建模与分析,同时保持晶体管级精度,并符合 IBIS 7.0 规范要求。

✓ 通过内置的时域仿真向导,验证行为模型相对于原始晶体管模型的准确性。

✓ 模型转换过程中已包含准确性检查环节。

✓ 对于熟悉现有 IBIS 模型格式的用户而言,其具备高度自动化特性且易于使用。

✓ 所有 IBIS BIRD95/BIRD98 功耗感知相关效应均已包含在内。

✓ 基于向导的方法可引导用户完成 IBIS-AMI 模型的创建。

✓ IBIS-AMI 模型会自动编译生成,适用于 Windows 和 Linux 系统版本。

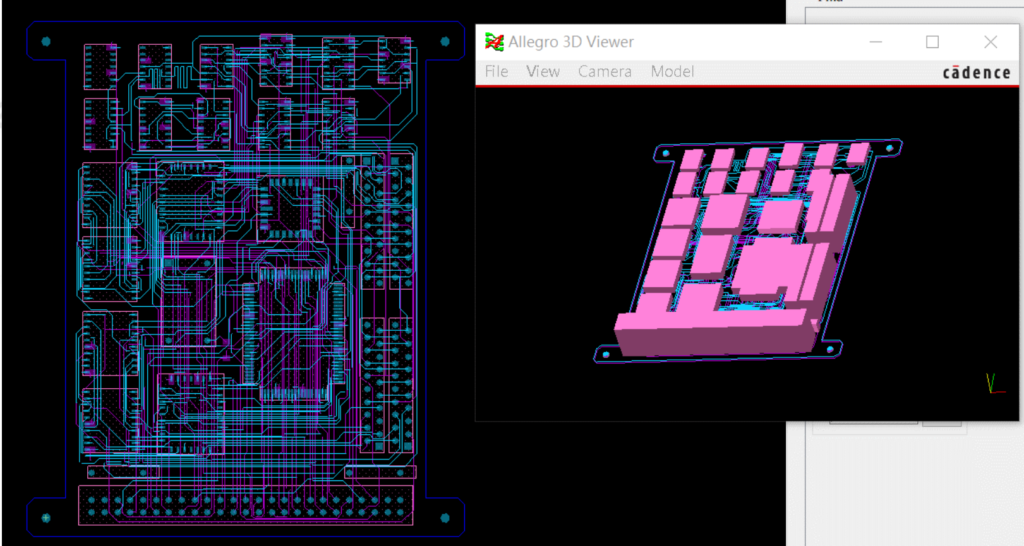

✓ 用于创建信号测试平台的通用拓扑环境

✓ 并行总线仿真环境,在此环境中,可对数十路信号进行同步开关仿真,同时还能对供电分配网络(PDN)和电 压调节模块(VRM)进行仿真。