【工具升级】 I Allegro X 新功能汇总,高效完成一体化系统设计

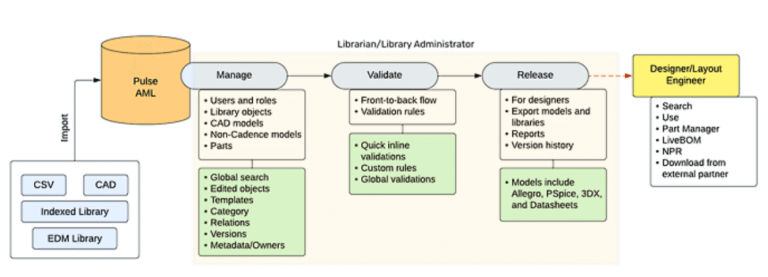

本文为大家详细介绍 Allegro X 平台的全新更新内容,本次更新实现了设计周期的缩短、协作能力的提升,并可与企业全流程工作流无缝集成,助力完成一体化的系统设计工作。 一、 25.1 版本更新 Allegro X 平台 25.1 版本进一步加速了高级设计流程,大幅提升用户设计效率。本次更新在基板布线、库集中化管理、印刷电路板(PCB)与先进封装设计(APD)编辑,以及系统级设计领域新增多项强大功

本文为大家详细介绍 Allegro X 平台的全新更新内容,本次更新实现了设计周期的缩短、协作能力的提升,并可与企业全流程工作流无缝集成,助力完成一体化的系统设计工作。 一、 25.1 版本更新 Allegro X 平台 25.1 版本进一步加速了高级设计流程,大幅提升用户设计效率。本次更新在基板布线、库集中化管理、印刷电路板(PCB)与先进封装设计(APD)编辑,以及系统级设计领域新增多项强大功

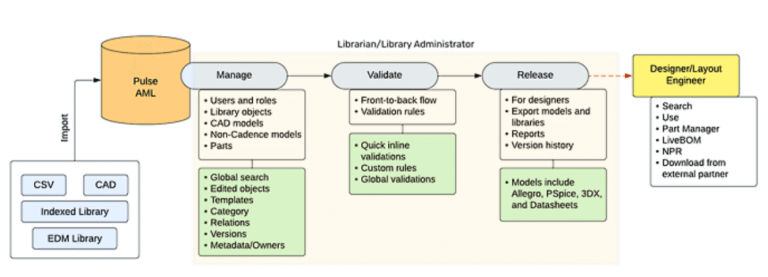

在电子电路设计领域,一款功能强大、适配协同工作的工具,能大幅提升设计效率与精准度。OrCAD X 系列版本更新,围绕协作、易用性、仿真分析三大核心,为个人及小型设计团队带来全方位的功能升级。以下是 25.1、24.1、23.1 版本的核心新功能汇总。 25.1 版本:强化协同与仿真,缩短设计周期 OrCAD X 25.1 版本的更新,实现了设计团队协作模式与设计完整性验证的重大突破,核心是让工程师

探索 OrCAD X 中的最新功能与增强特性,这些功能可助力个人及小型团队实现快速、精准且协同化的设计。 25.1版本更新 OrCAD X 25.1 版本在设计团队协作方式与设计完整性验证方面实现了重大突破。该更新以易用性为核心打造,为工程师提供了更简洁的方案,使其能在设计环境中直接进行设计审查、分享反馈与协同工作。其与 Sigrity X 分析工具的集成能力得到增强,可确保在设计流程早期就纳入性

汽车行业如今正处于技术飞跃的关键转折点,这次转变甚至要比从马车到汽车的转变更具革命性。这场变革迫在眉睫,它的转变方向不是电动汽车,也不是自动驾驶汽车,而是尖端电子技术的集成,这将重新定义汽车设计和性能的本质。 这次转变的核心是一系列趋势,所有这些趋势都指向汽车行业风向的重大调整——汽车电子行业正在快速发展,不断突破现代汽车的能力极限。 不断缩短的开发周期和全新的汽车愿景 在过去,汽车行业要经过几年

2025年2月11日,Cadence 在美国奥兰多举办了的 Cadence 全球合作伙伴会议,这场盛会汇聚了 Cadence 全球的优秀合作伙伴,共同探讨行业发展趋势,分享前沿技术与创新理念。而耀创科技(U-Creative)在此次会议中荣获“Cadence技术影响力”奖项! 耀创科技(U-Creative)还完成了2024年100%销售目标,这一成就的背后,是耀创科技(U-Creative)销售

4 月 10 日,Cadence(楷登电子)全球副总裁兼多物理场仿真事业部总经理顾鑫,Cadence 副总裁兼亚太区技术运营总经理陈敏等一行在吉林大学中心校区与吉林大学党委常务副书记冯正玉,汽车工程学院、通信工程学院、数学学院、电子科学与工程学院等学院相关负责人会面,双方就未来合作方向进行深入交流,达成新共识。 顾鑫对学校的欢迎和接待表示感谢,并介绍了 Cadence 作为全球电子系统设计领域的关

Cadence 在 2024 Chiplet 峰会期间展示了用于芯片间互联的多个 IP。与会者与我们讨论了他们的小芯片和多芯片设计需求,并了解了 Cadence IP 如何支持他们以最佳 PPA 目标实现系统需求。Cadence UCIe™ IP 硅演示因其广泛的测试而引起轰动。 Cadence 在峰会期间推出了首款采用有机封装的 UCIe IP 芯片。这是业界首创,证明了在整个互连距离(短距离、

3 月 28 日-29 日,2024 国际集成电路展览会暨研讨会(IIC Shanghai)在上海成功举行。此次盛会汇聚了集成电路产业的众多领军人物,共同探寻和把握集成电路产业的发展脉络。 在 29 日举行的 2024 中国 IC 领袖峰会上,Cadence 数字产品资深高级总监刘淼发表了题为《当汽车电子遇见 3D-IC》的精彩演讲;而在同期举行的主题技术论坛上,Cadence 资深技术支持总监王

2024 年 3 月 29 日,在由全球电子技术领域知名媒体集团 ASPENCORE 举办的“2024 国际集成电路展览会暨研讨会”上,Cadence 楷登电子再次以出色的业绩和创新实力,荣获 2024 年度中国 IC 设计成就奖之“年度卓越表现 EDA 公司”。 中国 IC 设计成就奖至今已举办 22 年,是中国半导体产业极具专业性和影响力的奖项之一。Cadence 已连续 12 年斩获该奖项,

3 月 20 日,SEMICON / FPD China 2024 开幕主题演讲在上海浦东嘉里大酒店隆重举行。本次开幕主题演讲汇集了众多全球行业领袖,演讲嘉宾们向现场观众分享了全球产业格局和技术市场趋势等方面的最新观点。 其中,Cadence 总裁兼首席执行官 Anirudh Devgan 博士以“如何在人工智能驱动时代取得成功”为主题,向与会者阐述了 AI 对企业目前产品矩阵不断完善的推动力,未

随着汽车加速迈进电动化时代,在电动汽车(EV)的竞争激烈和消费者期望不断上升的大潮中,设计创新成为推动力。一方面,传统的车企如今正面临着众多的新挑战,他们正在加速推出自己的电动产品系列来紧跟市场节奏;另一方面,“轻装上阵”的造车新势力来势汹汹,他们则在重新解读用户对交通工具的态度并试图重塑电动汽车的形式。 根据 European Alternative Fuels Observatory 的欧洲市

在身处技术驱动的大环境中,半导体设计需要做到更迅速、更节能以及更稳健。为了满足这一需求,半导体制造企业需要不断突破技术创新。通过对更多参数及其影响的分析,客户才能实现较现行设计方法更优秀的 PPA 目标。例如,全局额定值或全局的裕度会造成性能和功耗的显著浪费。 为了应对类似挑战,Cadence 持续创新并开发了 Cadence Tempus 设计稳健性分析(DRA)套件,提供解决上述问题所需要的分