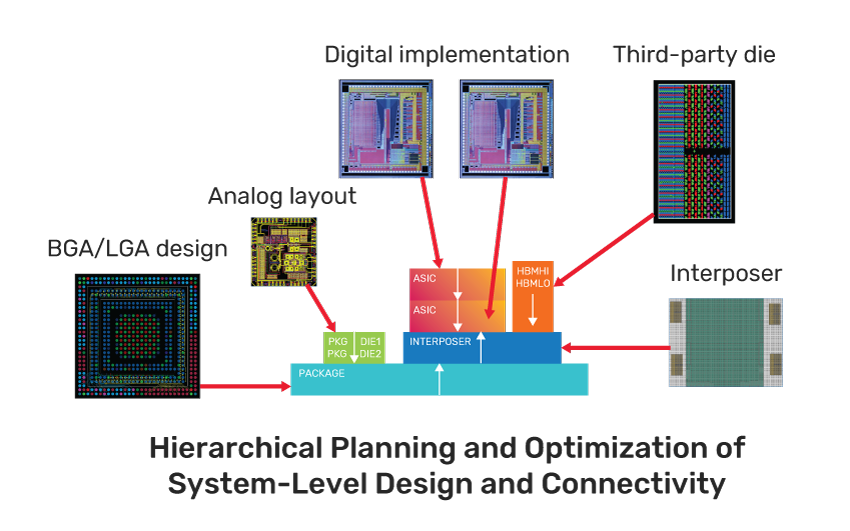

从芯片(硅片)到集成电路封装,再到 PCB 的系统 级设计规划与优化

Cadence Integrity System Planner 通过在单一环境中整合 IC 、 interposer、package 和 PCB 的数据,彻底革新 了系统级互连架构设计、评估、实施与优化流程。在实施前,用户可在完整系统背景下轻松推导并评 估信号到凸点 / 焊球的分配以及互连 / 布线路径方案。全系统互连可视化功能与统一数据模型,能够 支持用户快速探索设计变更,并将变更同步到相邻的基板(substrate),同时即时反馈这些变更对整 个系统产生的影响。此外,该系统设计还可作为系统级分析的基础,例如用于系统级版图与 schematic 一致性检查(LVS)、热分析(thermal)、电源分析(power)以及信号完整性(signal integrity)分析。

完整性系统规划器(Integrity System Planner)可帮助工程师或架构师在实施前,实现多基板互 连集成的合理平衡,以优化性能、成本和可制造性 —— 最终减少迭代次数,缩短周期时长。

概述

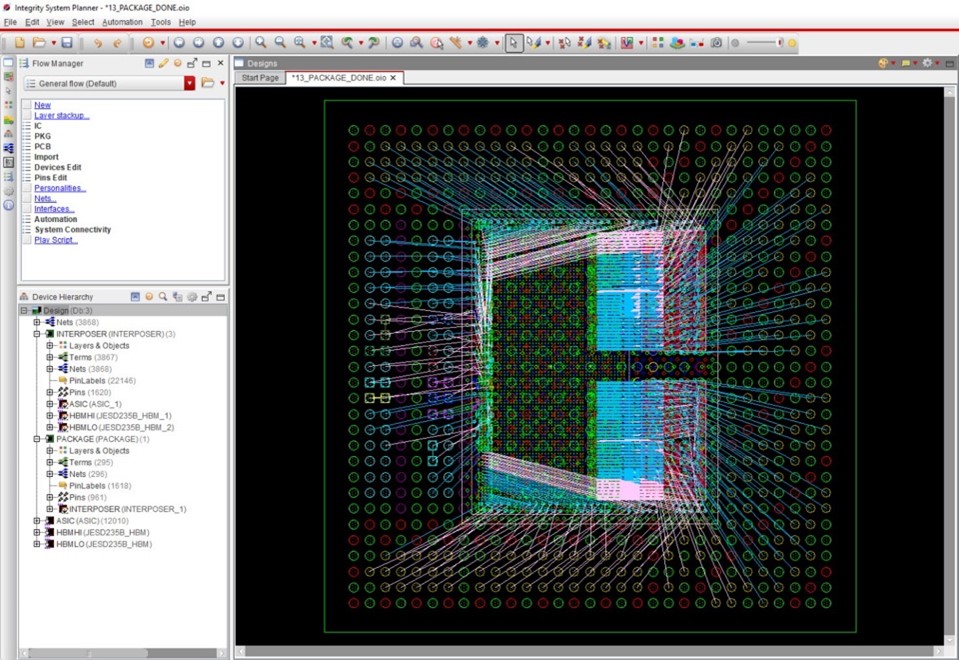

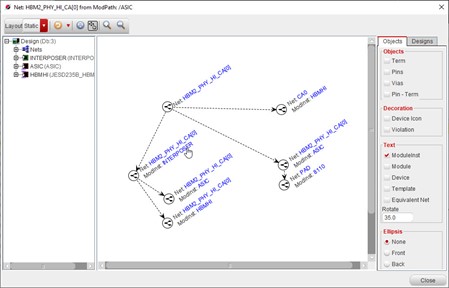

完整性系统规划器为设计团队提供单一工作环境,支持团队对构成系统的多个基板进行架构设计、评估并构建互连,进而帮助设计团队优化器件与系统性能。该工具非常适合系统架构师、项目负责人或独立设计师使用,可助力其开发管芯到管芯(die-to-die)、管芯到封装 / 中介层(die-topackage/interposer)以及封装到印制电路板(package-to-PCB)的接口,并确定凸点 / 焊球 (bump/ball)配置与信号分配的最佳组合。完整性系统规划器的一大关键优势在于,能够在保持各设计自身完整性与设计范围的同时,提供完整的系统视图与互操作性,如图 1 所示。每个设计都可针对相应的实施环境进行准备与管理。系统级分析可通过 Cadence 的高容量统一设计与分析平台 —— Integrity 3D-IC System Platform 进行配置和启动,该平台专门用于多芯粒(chiplets)设计。

图 1:组装并管理系统设计

优势

➢ “构建即正确” 的单一来源系统设计

➢ 优化的基板间互连与凸点分配

➢ 通过缩短整体布线长度提升性能

➢ 通过优化连接,减少布线层数与过孔数量

➢ 缩短工程变更单(ECO)的周期时长并降低其复杂度

功能

系统级组装与规划

完整性系统规划器提供了一个能够整合来自不同来源设计内容的环境,可用于开展系统级设计组 装、布局规划、互连定义与优化工作(图 2),并能将这些数据传输至各自对应的实施工具中以完成 后续流程。该工具是跨基板整体解决方案的组成部分,可在一系列 Cadence 产品间实现 互操作性,包括 Cadence Innovus Implementation System 与 Cadence Virtuoso Studio 。此外,在完整性系统规划器中开发的封装设计可直接导入 Cadence Allegro Package Designer Plus 环境,助力加快详细封装实施进程。通过这种方式,整个系统设计可基于单一来源进行创建,并贯穿实施全过程进行管理。系统级互连可视化能力与互连优化功能相结合,能够实现全系统范围内的凸点(bump)优化。

图 2:系统级互连定义、可视化与优化

Contact Layer Definition and Management

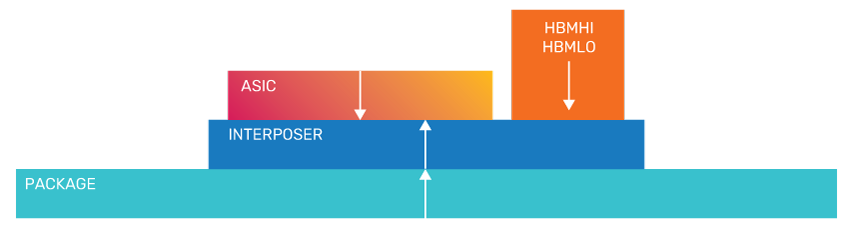

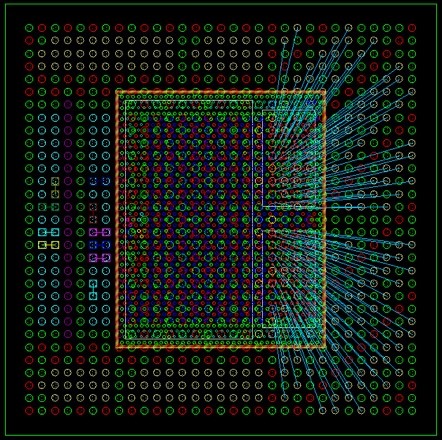

跨基板优化的初始步骤是确定管芯、封装、中介层与印制电路板(即各类器件)之间的物理关系。 首先识别出每个器件上用于建立物理连接的接触焊盘层,随后可在被连接的器件上自动生成配对的接触 焊盘。

Integrity System Planner 会自动管理这些关系,并在设计更新过程中保持 每个基板上接触焊盘的完整性,如图 3 所示。

图 3:配置设计堆叠

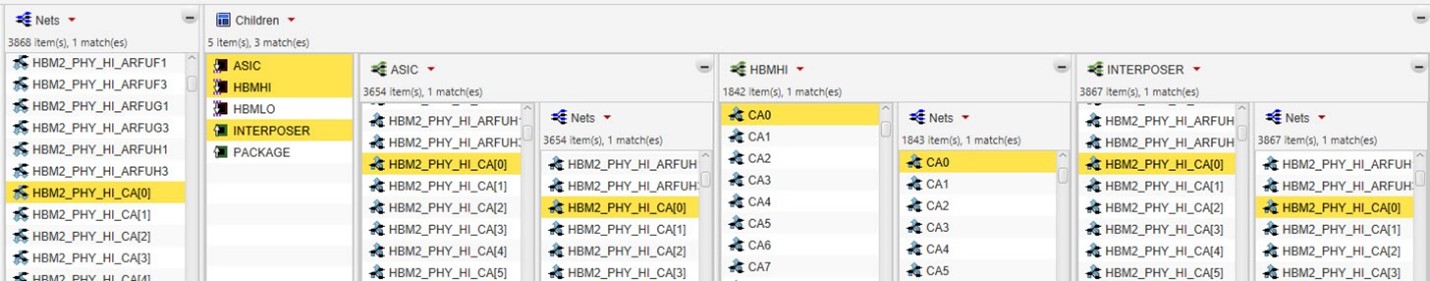

创建接触层还会在器件之间建立逻辑关系。通过接触焊盘的定义,网络会自动传播到被连接的器件 中。对于高带宽内存(HBM)等复制型管芯,网络名称前缀可对其网络名称进行唯一标识。之后,可通 过映射网络,在具有不同网络名称的器件之间建立互连。

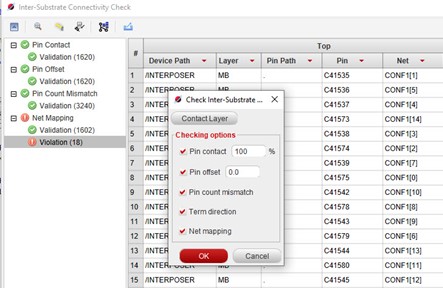

如图 4 所示,执行基板间互连检查的目的是验证接触层的完整性。检查内容包括引脚接触百分比、 引脚偏移量、引脚数量不匹配、端接方向以及网络映射。系统会列出所有违规项,且可高亮显示存在 问题的对象。该功能有助于在整个设计流程中保持系统设计互连的完整性。

图 4:基板间互连检查

互连定义与优化

作为一个灵活的探索环境,Integrity System Planner 可用于处理现有网表、 无网表的情况,且在多数情况下,也支持处理部分网表。如图 5 所示,网表编辑器(Netlist Editor)功 能允许设计人员在逻辑层级结构中上下传递和映射网表。互连可通过交互式映射网表来定义,在此过程 中,设计人员可使用正则表达式定义模式。通过创建接触焊盘或执行互连优化流程,网表会在各基板之 间自动传递。

互连也可通过导入 CSV 网络映射文件、CSV 端接文件或 Verilog 网表来定义。

图 5:交互式网络映射与可视化

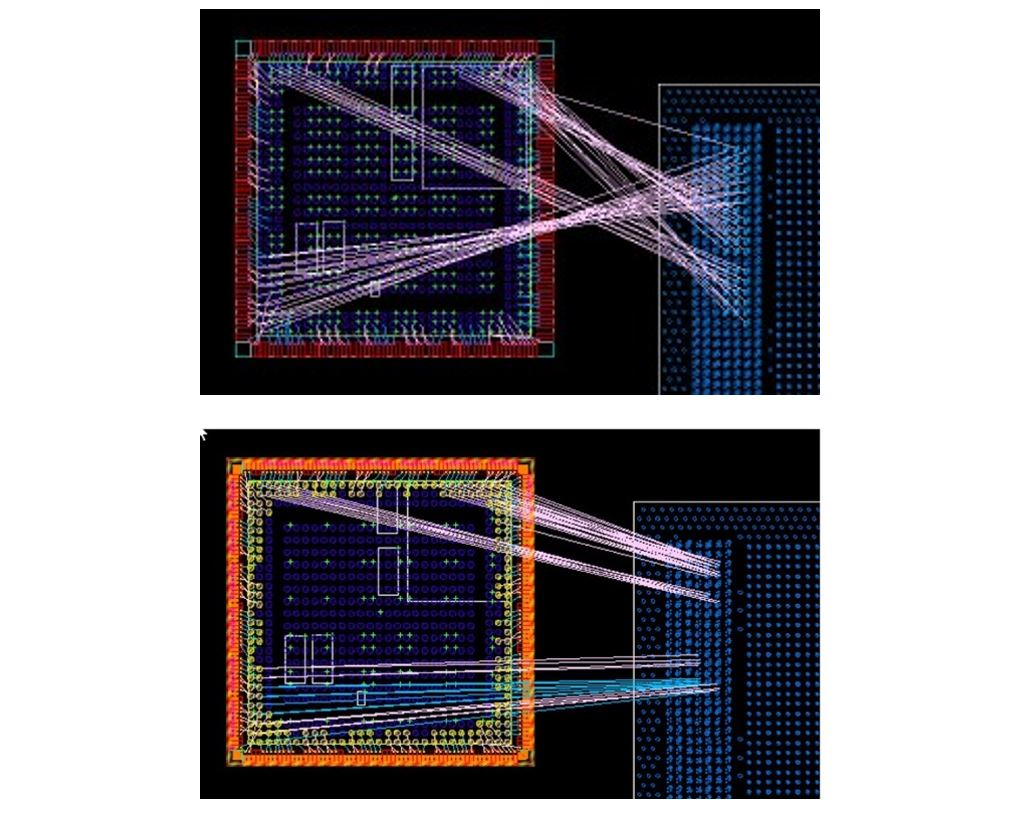

互连优化(Connectivity Optimization)功能支持自动引脚分配,以减少布线交叉和网络长度。如 图 6 和图 7 所示,该功能可用于优化管芯 – 管芯(die-die)连接,或优化顶部凸点 / 焊盘(top-side bumps/pads)与底部凸点 / 焊球(bottom-side bumps/balls)之间的连接。

图 6:管芯到管芯的互连优化

图 7:优化的底部凸点分配

系统级互连可通过网表编辑器(Netlist Editor)功能或网络图形(Net Graph)功能进行分析。如图 8 所示,网络图形会显示网络的完整拓扑结构,包括该网络上存在的已映射子网络名称、端接元件、 引脚以及过孔。

图 8:在系统设计中探究网络拓扑结构

实施集成

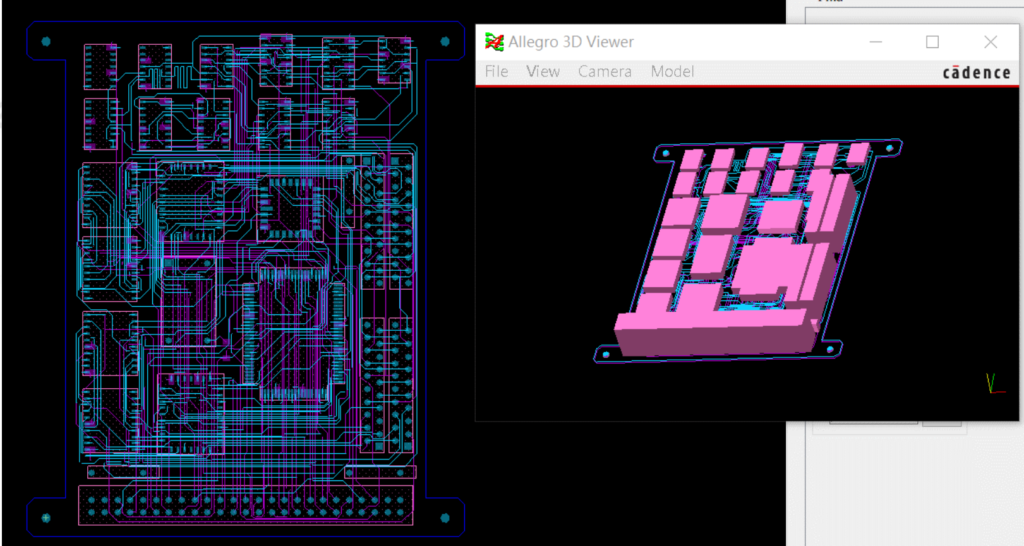

Integrity System Planner 与 Allegro Package Designer Plus 的集成效果优异。数据库可直接导入 Allegro 封装设计增强版,生成实施所需的符号、 层叠结构、焊盘堆叠以及网表。可在完整性系统规划器中进行增量变更,并将其导入当前活跃的 Allegro 封装设计增强版项目中。而在 Allegro 环境中所做的变更(如引脚交换、元件布局等),则可 合并回完整性系统规划器的源设计中,以保持两者同步。

Integrity System Planner 同时也是 Integrity 3D-IC 平台的核心控制中枢, 能与 Innovus Implementation System、Virtuoso Studio 以及 Allegro Package Designer Plus 实现紧密集成。

接口格式

➢ 芯片数据:管芯摘要(Die Abstract)、库交换格式(LEF)/ 设计交换格式(DEF)、管芯文本文件(die TXT)以及引脚 CSV 文件(pin CSV files)

➢ 封装数据:与 Cadence Allegro(文件格式为.sip、.mcm)直接进行数据交换,还支持管芯文本文件(die TXT)、引脚 CSV 文件(pin CSV files)以及管芯摘要(Die Abstract)。

➢ PCB 数据:Cadence Allegro PCB(文件格式为.brd)以及其他主流系统