就在你以为版图设计万无一失时,棘手的问题却接踵而至——莫名的信号反射、数据传输错误,或是无论如何调试都无法消除的信号噪声。

尽管信号完整性看似复杂难解,但多数常见问题都有切实可行的解决办法,只要掌握正确的思路、使用合适的设计工具,便能迎刃而解。

接下来,为大家梳理在设计中遇到的典型信号完整性问题,更重要的是,分享在设计过程中解决这些问题的方法。希望看完这些内容后,当你再面对信号完整性的挑战时,能多一份从容与自信。

简单来说,所谓信号完整性(SI),就是确保在 PCB 走线中传输的信号能无失真、清晰地抵达接收端。

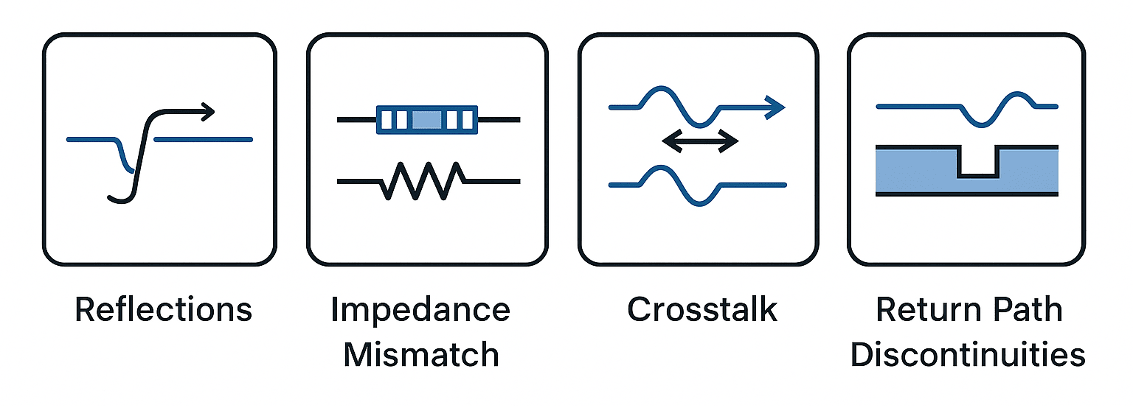

但实际设计中,高速信号的传输特性往往难以预测,各类问题也频繁出现。在我看来,引发信号完整性问题的最常见原因主要有以下几点:

就像在峡谷中大喊会听到回声一样,当 PCB 走线的阻抗不匹配时,信号传输也会出现类似的反射现象。信号遇到走线开路、端接方式不当等阻抗不连续的情况,部分信号就会被反射回去。

若走线阻抗与信号源、负载的阻抗不匹配,信号不仅会发生反射,还可能出现传输速率降低、信号衰减等问题。尤其是对于高速差分对,实现精准的阻抗控制至关重要。

相邻走线上的信号会相互干扰,这就是串扰。好比两个人在相邻的房间大声交谈,其中一个人的声音会传到另一个房间,造成听觉上的混乱,串扰对信号传输的影响亦是如此。

通常可以按照以下步骤诊断信号完整性问题:

重新确认 PCB 的叠层设计、介质常数以及走线宽度。即便是板材参数的细微变化,也会对阻抗产生影响。

借助 CAD 设计工具,验证走线阻抗是否符合设计标准——单端信号走线通常为 50 欧姆,差分信号走线一般为 90 欧姆。Cadence Sigrity 工具,能够轻松验证此问题。

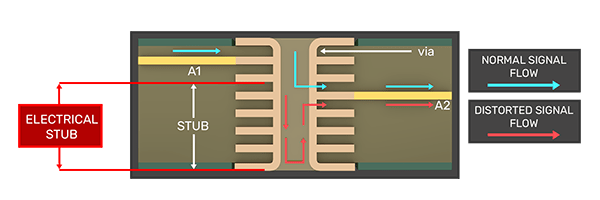

排查是否存在不必要的走线分支、尖锐拐角或过孔,这些都是可能引发信号反射和损耗的隐患。很多时候,优化走线布局就能解决一半的信号完整性问题。

确保高速走线下方有连续的参考平面,以此维持低电感的信号回流路径。一旦发现接地层存在间隙,就必须高度警惕。

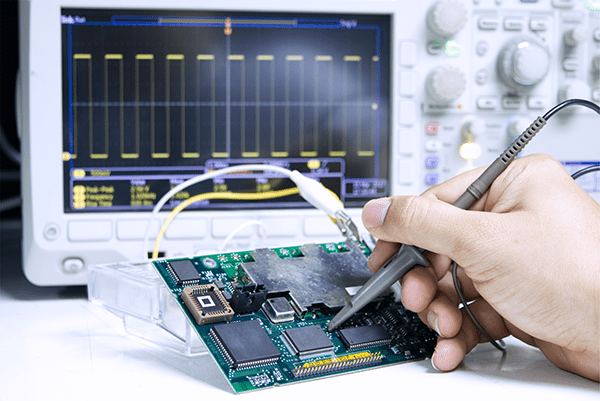

如果暂时无法使用高端仿真工具,我发现制作简易的测试夹具,或是用高带宽示波器测量样机的信号波形,也能发现大量问题。

在明确问题根源后,通常可以采用以下方法,让信号传输恢复正常:

严格按照叠层设计要求,把控走线的宽度和间距。对于差分对,保持间距一致、长度匹配,最大限度减小信号偏斜和噪声干扰。

尽可能让走线保持直连,减少过孔的数量——每个过孔都会增加走线电感,还可能成为新的信号反射点。若过孔无法避免,需在仿真中对其进行精准建模。

根据接口类型(如传输线、CMOS、LVDS),选择合适的端接方式。例如,在驱动器附近增设串联端接电阻,能显著降低信号反射。

重点保证接地层和电源层的连续性,无断裂、无间隙。完整的参考平面能有效降低回流路径的阻抗,减少电磁干扰。

若你在参与高难度的设计项目,灵活应用这些设计准则——尤其是优化接地层的连续性、设计合适的端接电路后,信号质量将会得到质的提升。项目也可从最初的设备故障频发,转变为最终产品信号传输干净、工作状态稳定,且所有测试项均留有充足余量通过。

3D 集成电路封装技术和新型 PCB 板材的应用,又为 PCB 设计增添了更多需要考量的细节。

建议是:保持持续学习的状态,在设计流程的早期就积极运用仿真工具,并且将仿真贯穿设计始终。对信号特性及其传输环境的理解越深入,在实验室调试时遇到的突发问题就会越少。

无论是验证阻抗匹配、优化走线布局,还是保障可靠的信号回流路径,这些步骤都能帮助你设计出性能稳定的高速PCB产品。

如果在设计中陷入困境,不妨回头重温基础理论,运用这些经过实践检验的方法。当然,Cadence系列设计工具功能强大,能在设计的每一个环节为你排忧解难,让信号完整性设计工作变得更轻松。