Cadence 的 Allegro FPGA System Planner,旨在解决工程师在 PCB 上设计一款或多款大引脚数现场可编程门阵列(FPGA)时面临的挑战 —— 这些挑战包括创建初始引脚分配、与 原理图集成,以及确保器件在电路板上可布线。该工具为 FPGA-PCB 协同设计提供了一套完整且可扩展的技术,能够自动 生成 “符合器件规则且精准” 的优化引脚分配方案。通过用自动化引脚分配综合替代人工且易出错的流程,这种独特的 “布局感知型” 解决方案可消除物理设计迭代,同时加快优化引脚分配的进程。

在 PCB 板上设计大引脚数现场可编程门阵列(FPGA)

如今的现场可编程门阵列(FPGA)不仅包含多种不同类型的分配规则,还具备用户可配置引脚,将这类 FPGA 集成到 PCB 上的过程耗时费力,且会延长设计周期。通常情况下,这些 FPGA 的引脚分配需在未关联 与 FPGA 相连的关键 PCB 元件布局的环境中,以逐个引脚的方式手动完成。由于不了解引脚分配对 PCB 布线的影响, 基于 FPGA 的设计项目往往被迫在两个欠佳的选项中抉择:一是接受非最优的引脚分配方案(这可能会增加 PCB 设 计的层数);二是在设计周期的尾声处理多次不必要的迭代。即便经过多次迭代,这种人工且易出错的方式仍可能 导致不必要的 PCB 设计返工。

使用手动方式为现场可编程门阵列(FPGA)生成引脚分配会耗费额外时间,这使得用户无法在可用的不同 FPGA 器 件与 FPGA 子系统中所用器件的成本之间进行权衡。这是因为进行这种权衡意味着用户必须并行开展两个项目,而这两个 项目之间无法实现任何形式的设计复用。

Allegro FPGA System Planner

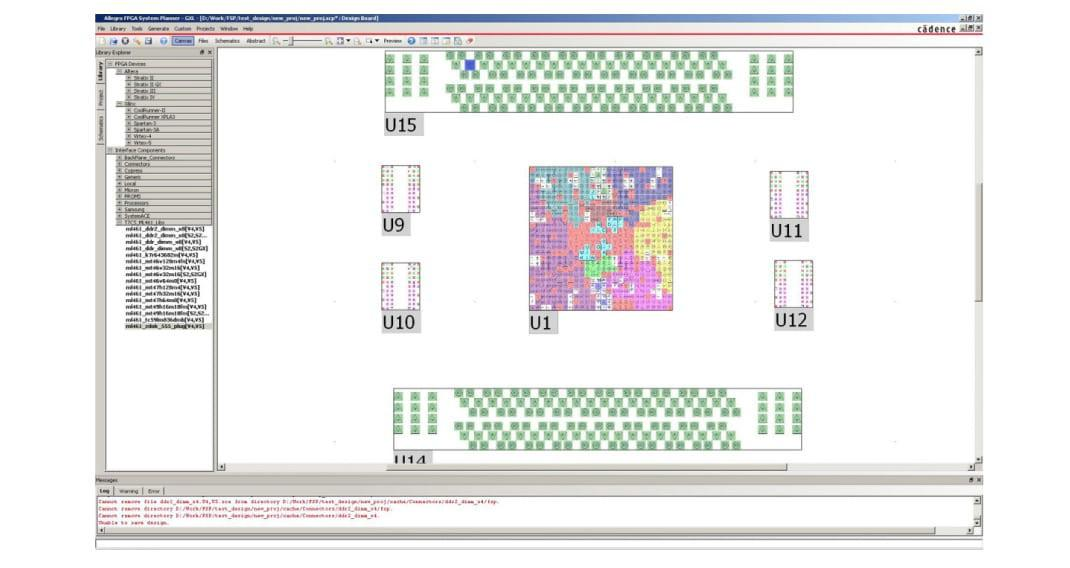

Allegro FPGA System Planner 为 FPGA-PCB 协同设计提供了一套完整且可扩展 的解决方案,能帮助用户生成 “设计即正确” 的优化引脚分配方案。FPGA 引脚分配会基于以下因素自动综合生成: 用户指定的、基于接口的连接关系(即设计意图)、FPGA 引脚分配规则(即 FPGA 规则),以及 FPGA 在 PCB 上的实际布局位置(即相对布局)。借助自动化引脚分配综合功能,用户可避开人工且易出错的流程,同时缩短生成初始 引脚分配方案的时间 —— 该方案会充分考虑 FPGA 在 PCB 上的布局位置(即 “布局感知型引脚分配综合独特的布局感知型引脚分配方法,能够消除人工方式中固有的不必要物理设计迭代。

通过一种能够高层利用一种能够基于用户指定的高层级设计意图快速生成优化引脚分配的方法,Allegro FPGA 系统规划工具使设计师能够探索其基于 FPGA 的架构,并为采用 FPGA 的量产设计或原型设计创建 “设计即正确” 的优化引脚分配方案。

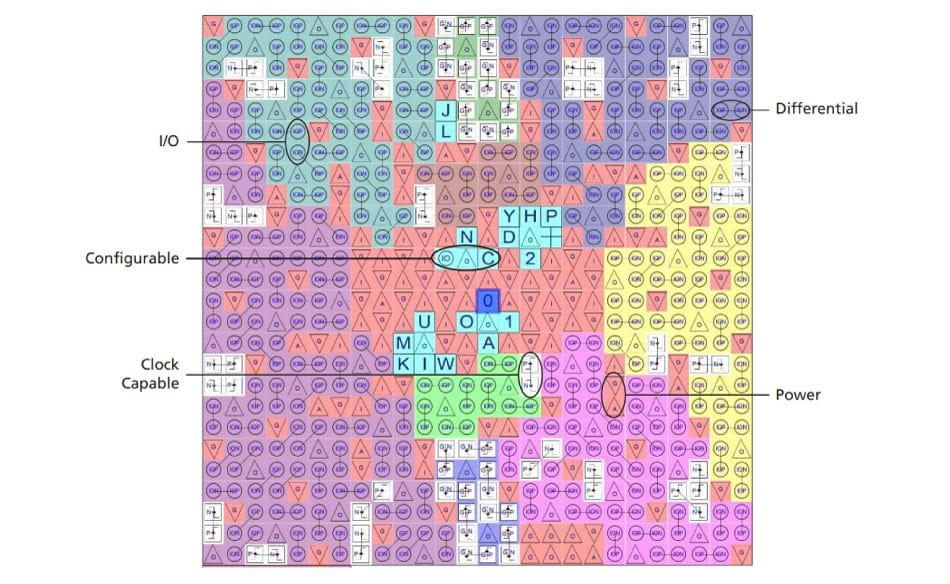

图 1:具有不同类型可配置引脚的多存储体现场可编程门阵列(FPGA)的 I/O 颜色编码图

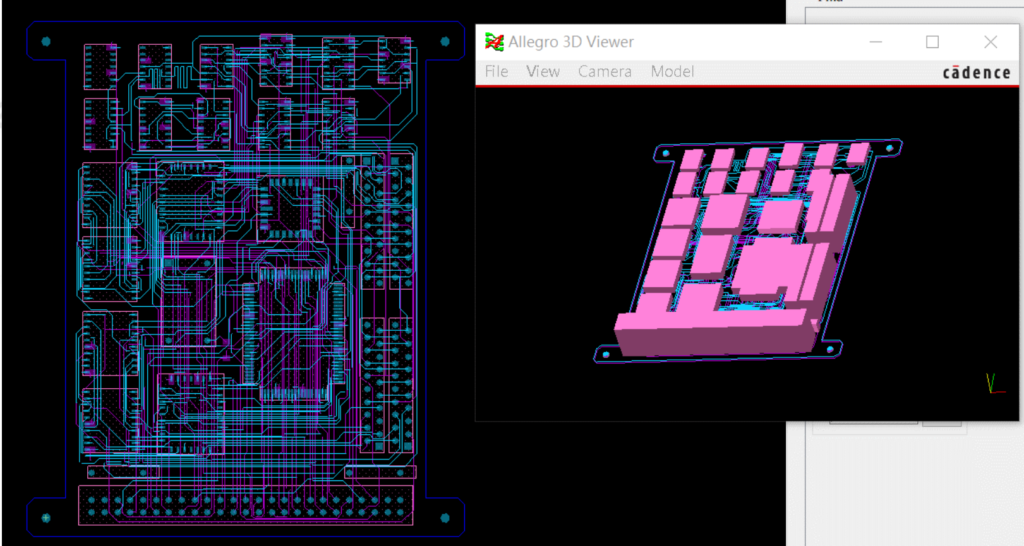

Allegro FPGA 系统规划工具与 Cadence 的设计创建工具相集成,包括 Cadence OrCAD Capture 和 Cadence Allegro Design Entry(CIS 和 HDL 版本)。该工具可为 OrCAD Capture 和 Allegro Design Entry HDL 读取并创建原理图符号。 此外,其布局规划视图可利用 OrCAD PCB Designer 和 Allegro PCB Editor 的现有封装库。若在布局过程中需要更改元件放置 位置,可直接从 Allegro PCB Editor 中调用 Allegro FPGA 系统规划工具的引脚优化功能。

优势

➢ 从 OrCAD 到 Allegro 工具的可扩展、高性价比 FPGA-PCB 协同设计解决方案

➢ 加速 FPGA 与 OrCAD Capture 及 Allegro 设计创作解决方案的集成

➢ 缩短生成优化初始引脚分配的时间,加快 PCB 设计进度

➢ 消除 PCB 布局过程中不必要且恼人的设计迭代

➢ 消除因 FPGA 引脚分配错误导致的不必要物理原型迭代

➢ 通过布局感知型引脚分配与优化减少 PCB 层数

➢ 规划模式允许 PCB 设计师基于布线规划提出 FPGA 引脚(重新)分配方案,从而减少设计的层数、缩 短布线时间,或同时实现这两个目标

2:布局 / 布局规划视图为用户提供关键元件的相对布局,以实现优化的引脚分配综合