系统级封装(SiP)实施为系统架构师和设计师带来新挑战。传统电子设计自动化(EDA)解决方案无法实现 高效系统级封装(SiP)和先进封装开发所需的设计流程自动化。楷登电子(Cadence)的 SiP 设计技术支持并 整合了复杂多芯片与分立基板组件的设计概念探索、捕获、构建、优化及验证流程,从而简化了将多个高引脚数 芯片集成到单一基板上的过程 —— 这是设计高性能复杂封装技术的必要前提。

Cadence 系统级封装(SiP)技术

高性能电子产品的设计师正转向先进封装设计,因为该设计具备多项显著优势,例如功能密度提升、不同芯片技术 的集成、低功耗、信号性能 / 完整性改善,以及易于集成到整体系统中。然而,这类设计也需要涵盖多个差异显著领域 的专业工程人才,这一点在以往限制了其在主流行业中的应用普及。 通过以连接性为导向的方法,将多个高引脚数芯片集成到单一基板的流程进行简化,Allegro X APD Layout 让设计师能够将以往仅为专业工程设计所具备的能力,应用于主流产品开发中。Cadence 的集成电路封装解决方案(IC Packaging solutions)可与 Cadence 的 Innovus 技术无缝集成,以实现芯片 / 封装互连的优化;同时也能与 Cadence 的 Virtuoso 技术无缝集成,用于支持原理图驱动的射频(RF)模块设计。

Allegro X APD Layout

Allegro X APD Layout 该工具增强了 Cadence Allegro X 先进封装设计平台(Allegro X Advanced Package Designer Platform)中以约束和规则为驱动的布局环境,助力设计师开发高性能、 复杂的封装技术。它新增了一套功能强大的自动 – 交互式流程、布线及调优特性,可加快关键互连(如 DDR 内存、高 速串行、硅基板和图形接口)的规划、优化、实例化及时序收敛速度。智能布线流程规划与自动引出工具(automated breakout tools)减少了耗时且繁琐的手动引出和布线工作,并能优化大型总线布线,以实现空间和层数的最小化利用。 此外,Allegro X APD 布局工具还基于 Specctra 技术,为硅基基板新增了额外的自动布线功能。

Allegro X DesignTrue 可制造性设计(DFM)全套综合技术与组装规则。该全套技术与规则可提高基板良率,并预 防制造及组装环节的问题。此选件支持对制造偏差进行评估,还能基于同一主设计生成具有不同基板叠层、管芯堆叠及 引线键合配置的设计变体。此外,该选件还支持与 Virtuoso 平台建立双向流程,以实现集成电路(IC)/ 封装协同设计。

优势

➢ 支持在集成电路(IC)、元件与基板之间进行连接分配和优化,可基于信号完整性和可布线性,实现层数的 最小化使用。

➢ 包含全面的基板可制造性设计(DFM)功能,助力快速完成生产准备工作。

➢ 基于基础设计生成键合与堆叠变体;结合设计规则检查和系统性能,评估工艺偏差(如线宽偏差)所产生的 影响。

功能

接口感知设计

在先进封装设计中,为满足产品对性能、功耗及带宽的需求,您可能会采用 DDRx、HBM(高带宽内存)、图形接 口以及高速串行总线等协议。您所使用的布局工具能否提供所需的速度与易用性,以跟上设计周期的要求?

倘若您能采 用一种分层式接口感知设计方法,来加速实施流程 —— 同时在此过程中提升设计质量、性能与可靠性,这将会带来怎样 的改变? 接口感知设计功能能够让您在更高的抽象层级进行封装设计,从而实现基于标准接口的更快布线。传统设计创作工 具仅支持总线或信号束,以及对一组信号的单一层级定义。然而,如今的接口已无法通过单一层级结构进行建模。此外, 还需应对其他挑战,包括:约束条件数量不断增加、设计密度持续提升、凸点与导柱间距逐渐缩小(同时高引脚数器件 数量不断增多),以及(在设计周期缩短、资源有限的情况下)设计布线耗时日益增加。

为快速便捷地实现接口连接,Allegro X APD 布局工具(Allegro X APD Layout)中的分层式接口感知设计功能可实现 以下操作:

➢ 支持在更高抽象层级进行设计创作,以提升工作效率

➢ 将接口定义传递给布局设计师

➢ 指导关键元件布局,并支持布线规划

➢ 支持使用自动 – 交互式技术,进一步加快接口的引出、布线与调优速度

该功能借助流程(flows)实现操作,支持您实例化接口与分层网络组(hierarchical Net Groups)、配置接口并将其连接至元件与模块、分配布线层,以及为实现可布线性和引出(escape)需求而调整分配方案。

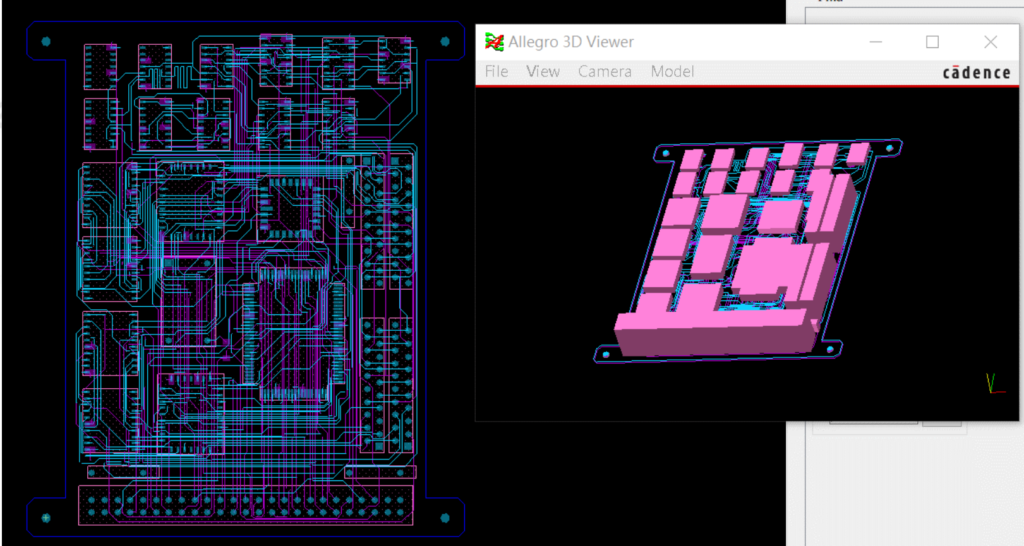

图 1:总线和接口通过流程(flows)呈现,简化了分配与布线的规划及优化工作。

自动 – 交互式功能与自动布线

Allegro X APD Layout 新增了一整套自动 – 交互式功能,可快速设计复杂的关键互连 (包括集成电路封装设计中的高速接口与总线)。该工具还包含基于 Specctra 技术的自动布线功能,适用于代工厂基 板与硅基基板。这些功能减少了繁琐、耗时的手动引出编辑工作及互连相关的手动操作。

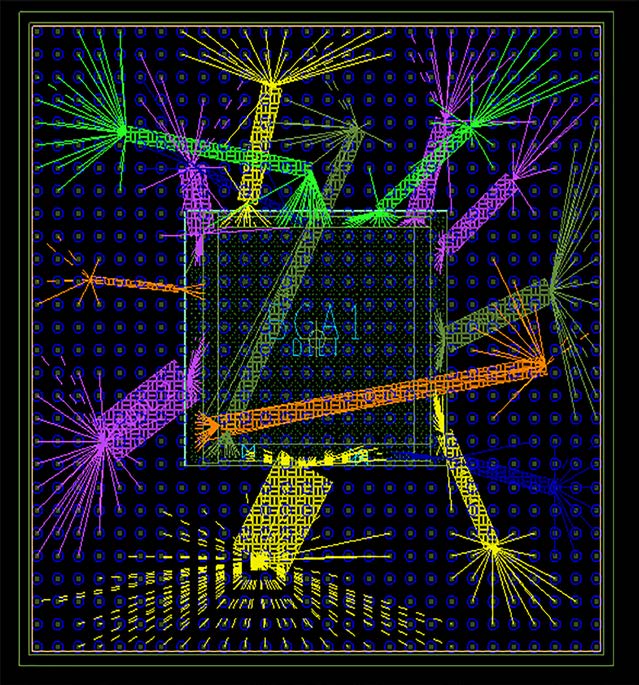

图 2:快速评估并修正差分对与总线的相位、延迟及时序问题。

全面使用 DesignTrue 可制造性设计(DFM)技术与 ARC(先进规则检查)功能

Allegro X Advanced Package Designer 中集成了一款在线高级语言规则检查引擎,可省去传统设计后繁琐的制造掩模检查工作。该引擎能大幅缩短生产准备时间,简化设计流程,并为封 装设计师提供有力支持。此外,借助可选的规则开发工具包(rules developer toolkit),还可编写并加密自定义设计规则检查(DRC)规则。

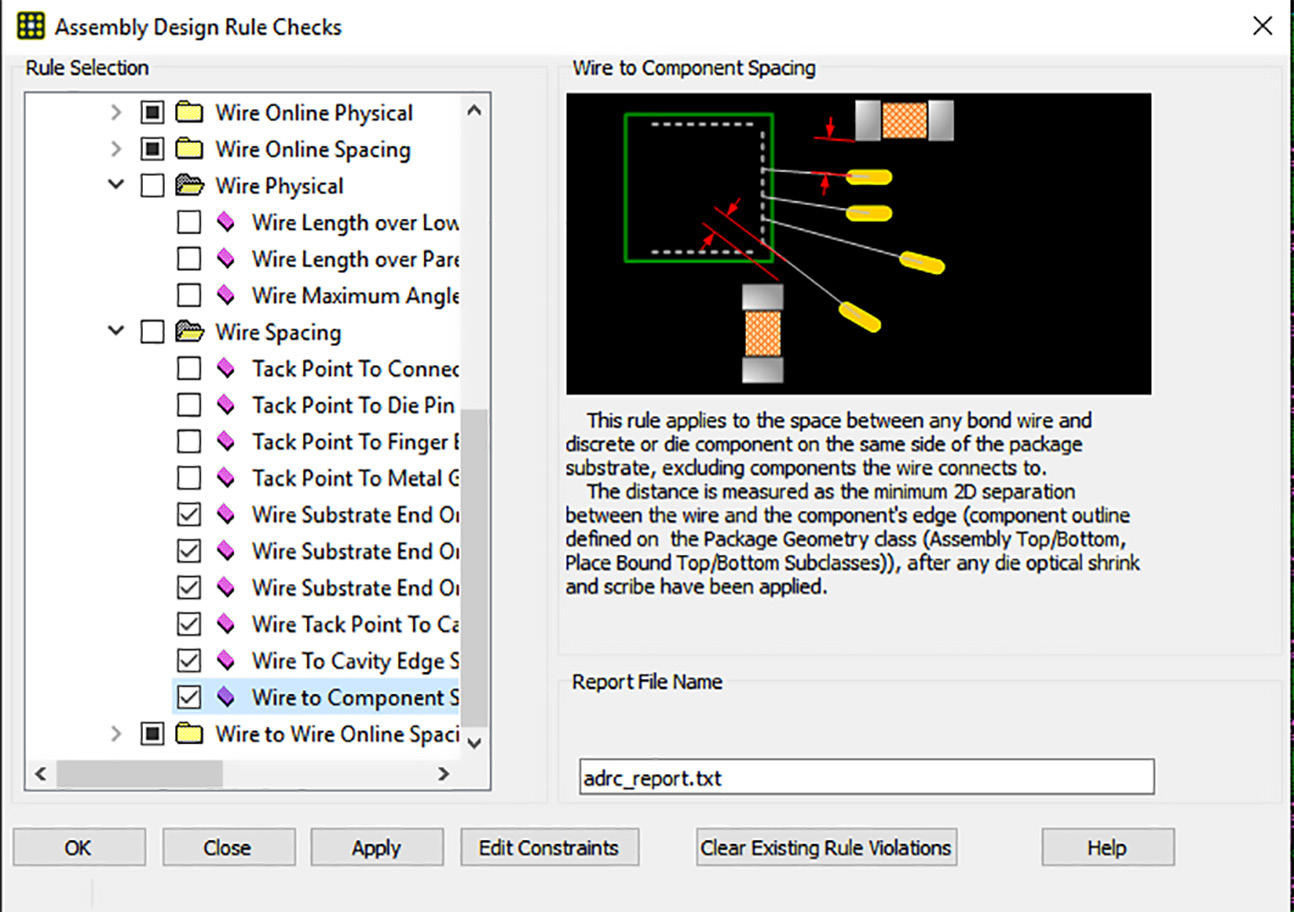

Allegro X APD 新增了一款全面的组装(及制造)规则检查器(ARC),可提供 50 余项集成电路封装专用检查功能, 包括复杂的引线间距与交叉规则检查。这些检查可通过检查组执行、单独执行,或按自定义选择执行;检查结果将显示在 “约束管理器” 的 “设计规则检查(DRC)” 选项卡中、“设计规则检查浏览器” 中,同时会以图形标记形式显示在设计界面内。 此外,该选件还支持使用全套全面的 DesignTrue 可制造性设计(DFM)规则,有助于提高基板良率,并预防制造及组装环节的问题。DesignTrue 可制造性设计(DFM)技术支持您真正地 “为制造而设计”—— 而非 “为制造而重新设计”,也无需为适配制造需求频繁修改设计 —— 进而加快新产品上市速度。您可在设计开始前定义制造商规则,并在设计过程中实时应用这些规则。

这样一来,当您完成设计时,就已经为首次可制造性设计(DFM)签核做好了准备。

可制造性规则的管理与协作十分便捷。与电气约束类似,其易用的电子表格界面对工程师和非工程师而言均直观易懂,规则复用也因此变得轻松。这些约束具备高度可配置性,支持启用或禁用规则组、完整规则类别,也可单独启用或禁用某一项规则。规则可应用于蚀刻模式、非蚀刻模式以及叠层模式,使设计师能够对图层、几何形状和切口进行隔离操作。

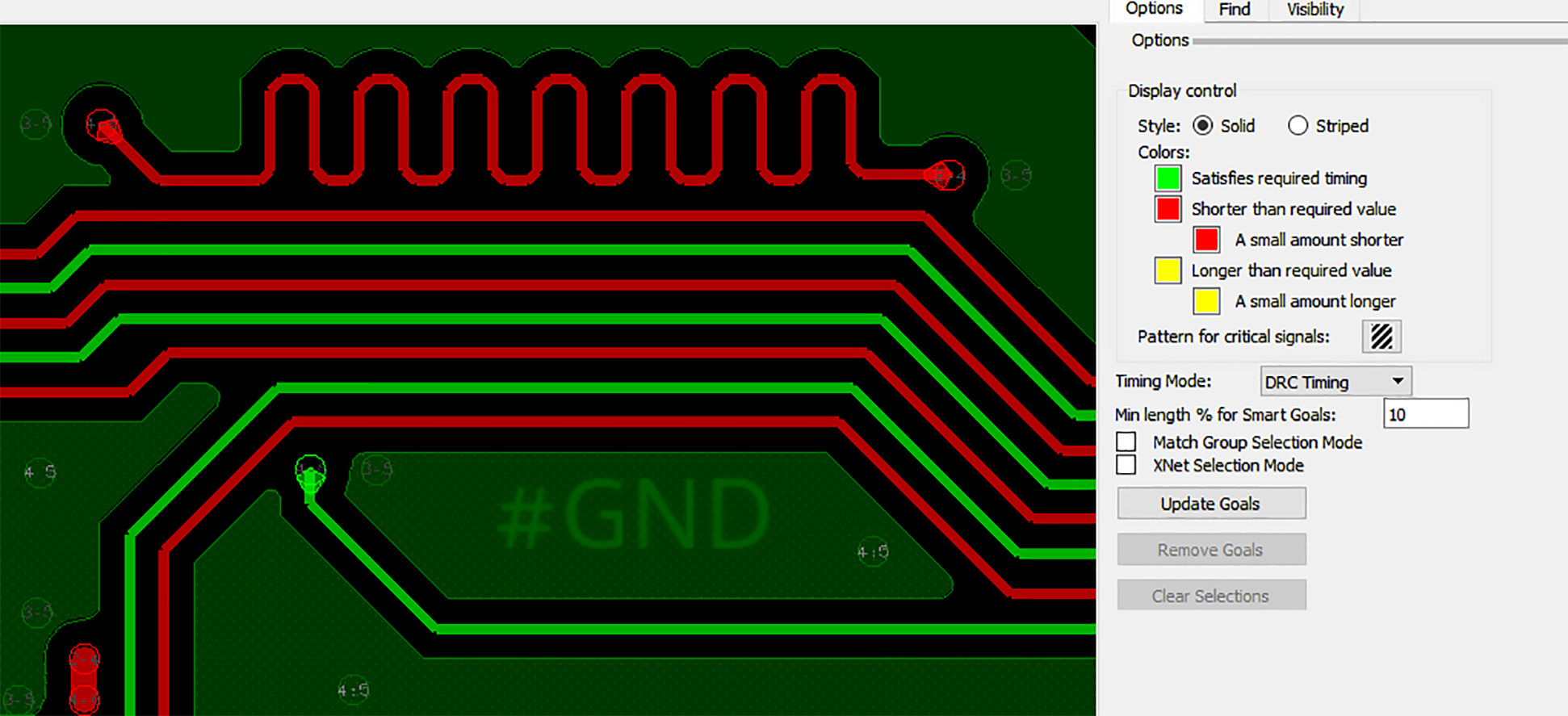

图 3:DesignTrue 可制造性设计(DFM)技术会对您的设计进行可制造性检查。

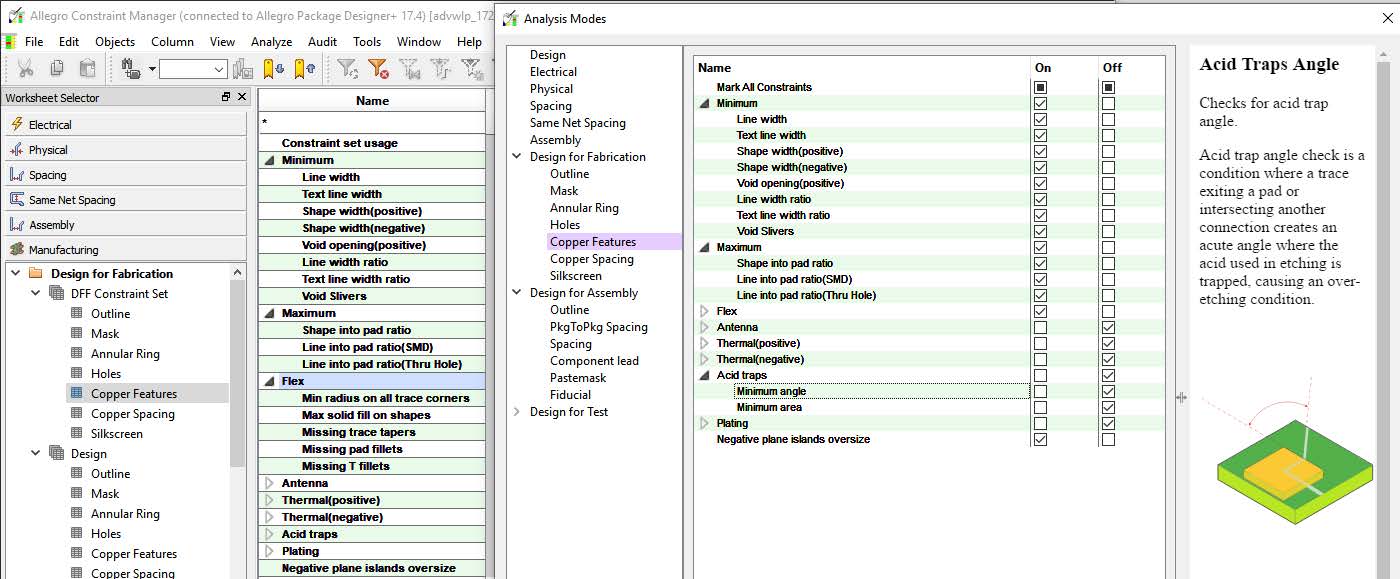

图 4:组装(及制造)规则检查器(ARC)检查复杂的引线相互作用及封装专用规则。

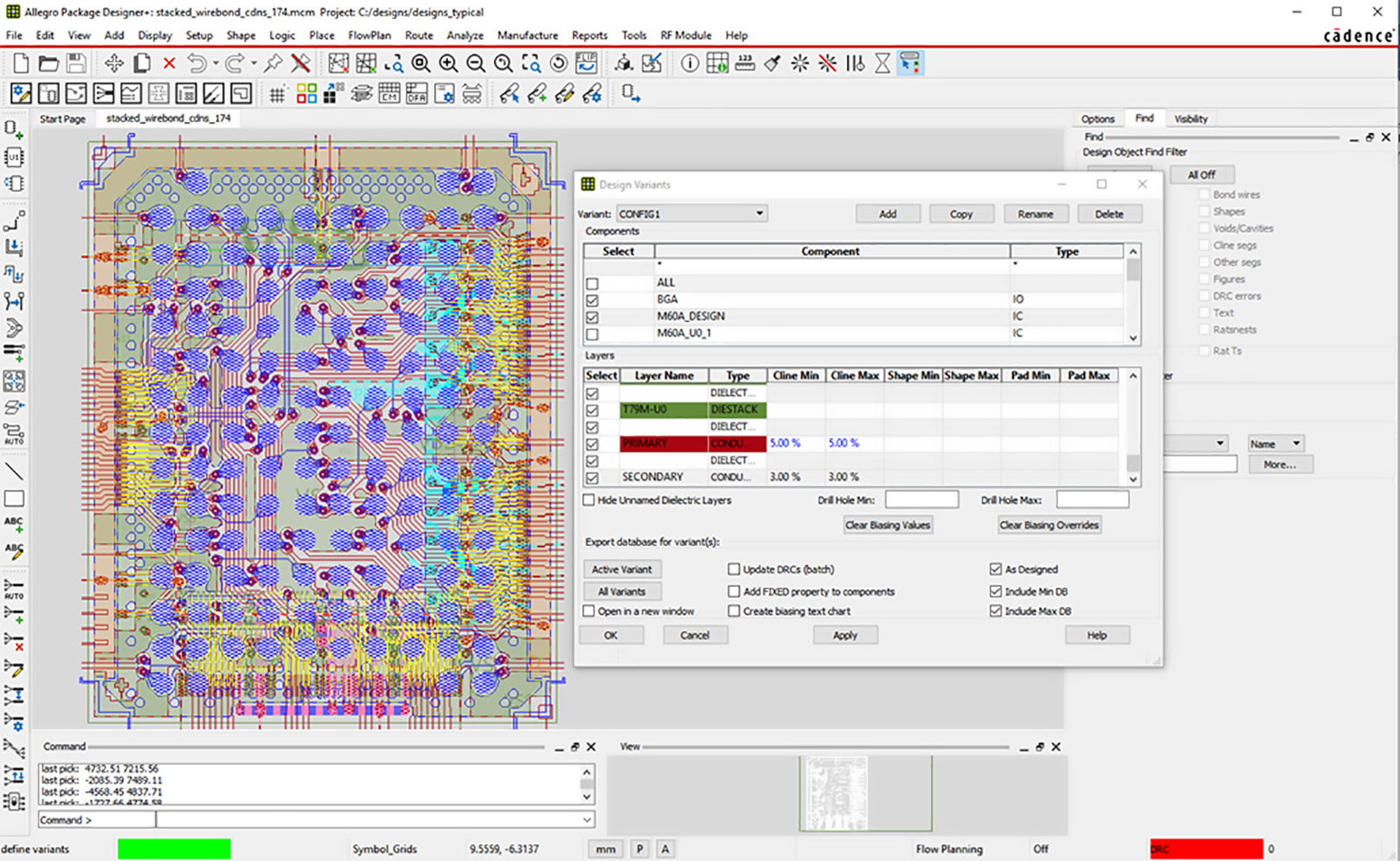

设计与工艺变体

在封装基板设计中,一款设计存在多种配置的情况十分常见,差异既可能体现在裸片数量与堆叠方式上,也可能体 现在裸片的键合引出方式上。Allegro X APD 支持设计师创建一个主设计,衍生出代表各变体的从 属设计,随后针对这些不同的键合与堆叠方案设计,进行物理设计规则检查(DRC)、引线设计规则检查(DRC)以及 信号完整性评估。此外,该选件还支持评估物理制造差异对设计规则检查(DRC)与信号完整性产生的影响。

图 5:可通过不同的裸片堆叠及键合方案创建设计变体。设计师还可评估制造 差异(如线宽差异)对性能与可制造性产生的影响。