高度灵活的拓扑环境使您能够从电压源到所有连接的元器件开展全面的电源完整性分析,支持通过早期 “假设分析” (what-if)场景,在多结构供电分配网络(PDN)中优化性能指标。随着设计推进,提取的 PDN 模型可无缝集成以反映 详细结构;若在签核(signoff)阶段出现设计故障,适应性强的拓扑界面能通过便捷地替换(接入或移除)理想 PDN 模 型,助力精准定位问题。

✓ 消除 PCB 和 IC 封装中的去耦电容过度设计问题。

✓ 降低新设计及量产产品的供电分配网络(PDN)成本。

✓ 为封装元器件制定有效的去耦电容(decap)指南。

✓ 优化印制电路板(PCB)与集成电路(IC)封装接口间的供电分配网络(PDN)。

✓ 稳健且经验证的底层混合电磁(EM)/ 电路分析技术。

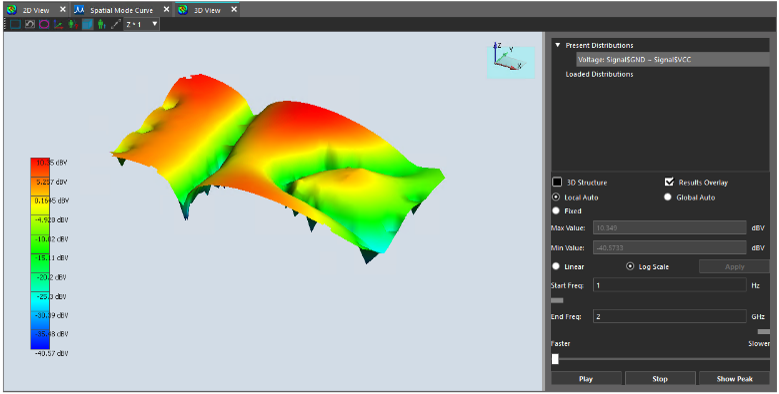

✓ 供电分配网络(PDN)性能的直观交互式可视化呈现。

✓ 布局前和布局后去耦电容(decap)优化的设置过程简单便捷。

✓ 借助 Allegro X,以及在 Mentor、Zuken 和 Altium 设计流程中,可可视化您原理图中的电源部分。

✓ 独特的器件阻抗与电磁干扰(EMI)谐振检查。