Allegro X Advanced Package Designer Platform 25.1

直观的集成电路(IC)封装与多芯片封装实现平台

直观的集成电路(IC)封装与多芯片封装实现平台

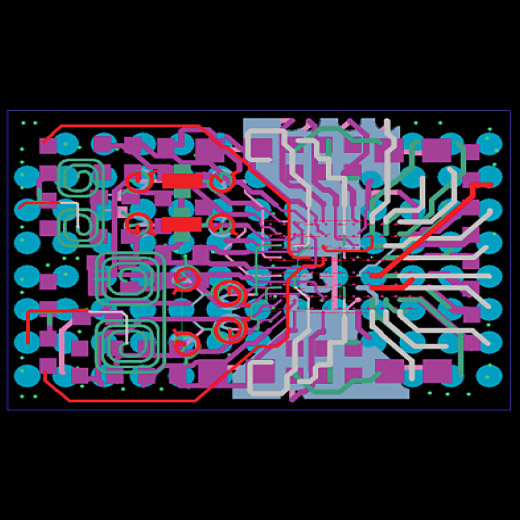

借助 Allegro X 先进封装设计平台,探索先进集成电路(IC)封装设计的巅峰水准。Allegro X 先进 封装设计平台能助力设计师以无可比拟的效率应对多芯片封装的复杂挑战,其搭载了一系列功能强大的 特性,专为满足现代半导体封装的需求而量身打造。从即时库文件开发,到约束驱动的布线,再到全面 的信号完整性分析,Allegro X 可确保即便在设计最复杂的封装时,也能实现一次设计成功。Cadence Allegro X 设计平台是应对现代电子复杂性的终极解决方案,可助力满足您多样化的印制电路板(PCB) 设计需求。作为一套全栈式工程平台,它为多板电子系统设计提供了一个具备可扩展性且高度集成的环 境。 Allegro X 先进封装设计平台能无缝集成到 “芯片 – 封装 – 电路板” 设计流程中,并支持多种布局方 案,因此成为优化成本、性能及产品上市时间的首选解决方案。目前已有超过 400 家全球客户信赖楷登 电子(Cadence)的集成电路(IC)封装设计技术,即刻提升您的设计能力吧!

Allegro X Advanced Package Designer Platform

凭借全面且直观的产品组合,实现卓越的集成电路(IC)封装设计

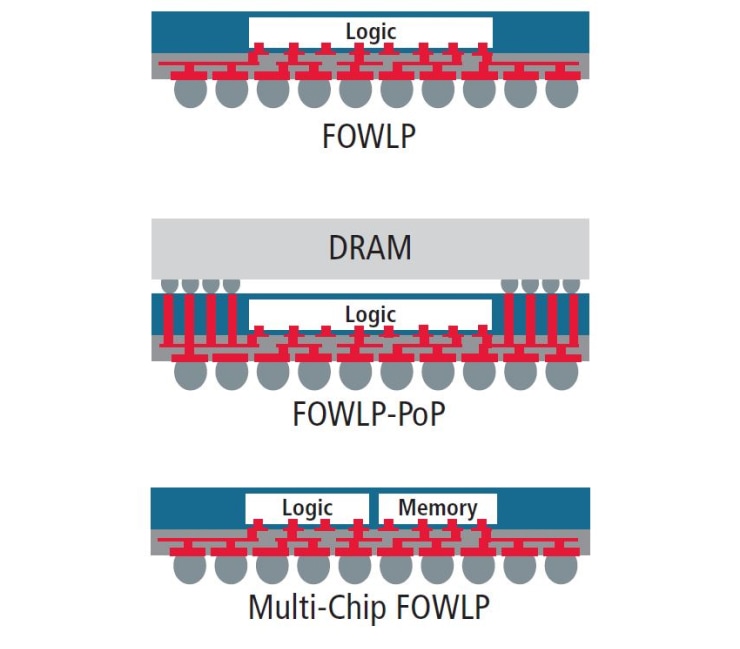

Allegro X 先进封装设计工具的硅布局选项旨在革新扇出型晶圆级封装(FOWLP)技术,凭借其轻薄设计、更高性能与成本效益,满足移动市场的需求。

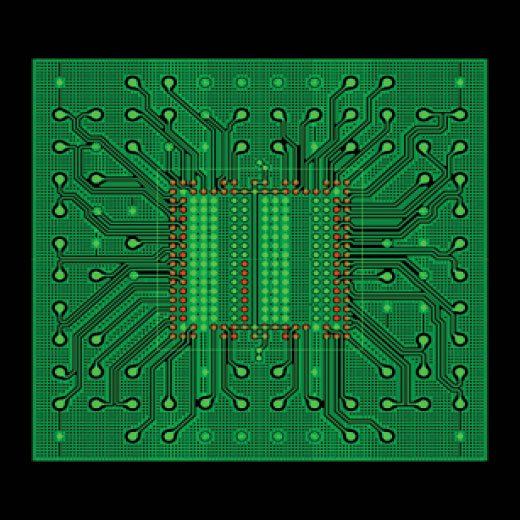

Allegro X APD 布局工具可应对系统级封装(SiP)实现过程中的各类挑战,简化高引脚数芯片在单 一基板上的集成流程。

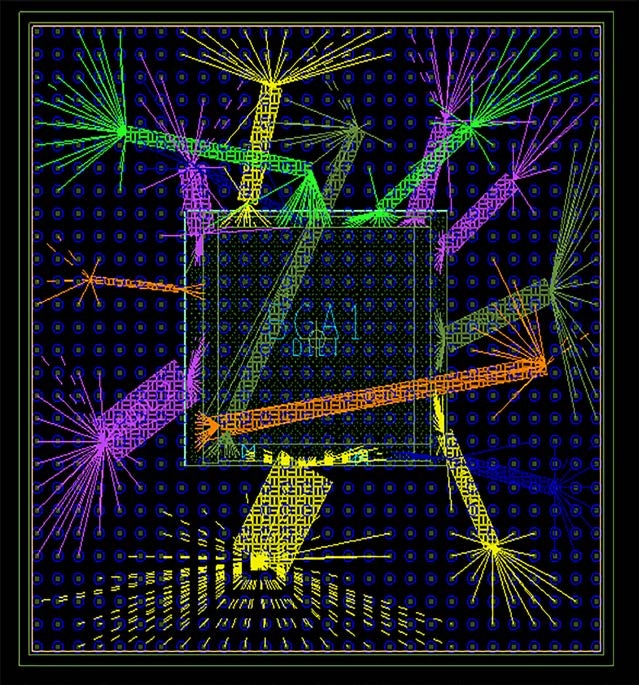

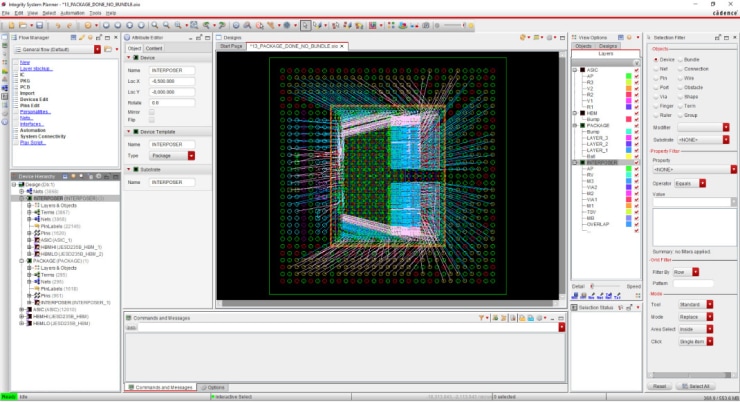

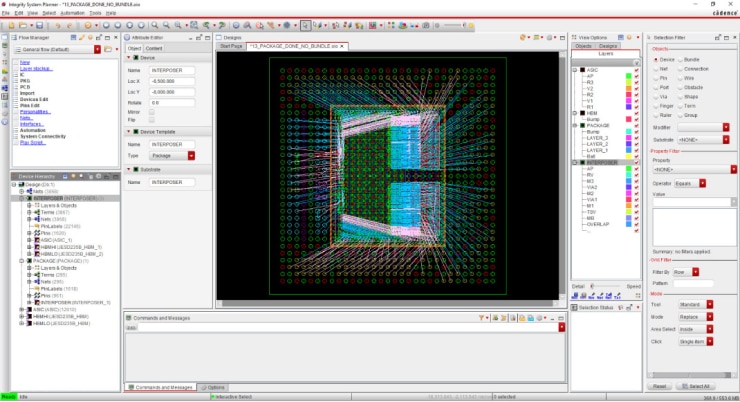

完整性系统规划器通过提供组装、布局规划和互连优化功能,简化了从芯片到印刷电路板(PCB) 的整个系统设计流程。

主要优势

满怀信心地设计、表征、验证并优化集成电路(IC)封装

加速封装设计

借助行业内针对先进基板的最全设计规则,设计复杂的多芯片封装;通过无缝集成与自动化布局指引,简化设计流程并将效率提升高达 50%。

提升设计信心

借助 Cadence 用于电气、电磁(EM)和热学验证的先进引擎,在设计阶段就开展分析 以实现 “左移”;通过实时检查,将设计验证时间缩短 30% 以上。

助力协同设计与签核

借助供应商组装设计套件(ADK)提供的布局指引与签核支持,实现集成电路(IC)封装与数字 / 模拟射频集成电路(RFIC)之间的无缝协同设计;在确保多芯片封装高效可靠的同时,减少重新设计次 数并加快产品上市时间。

应用

借助无缝的多芯片异构集成,助力您实现复杂设计

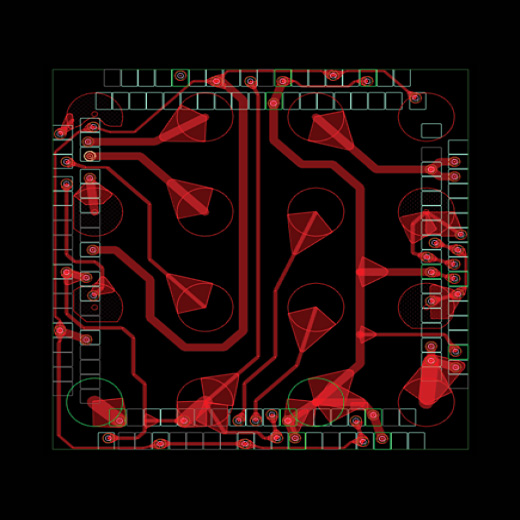

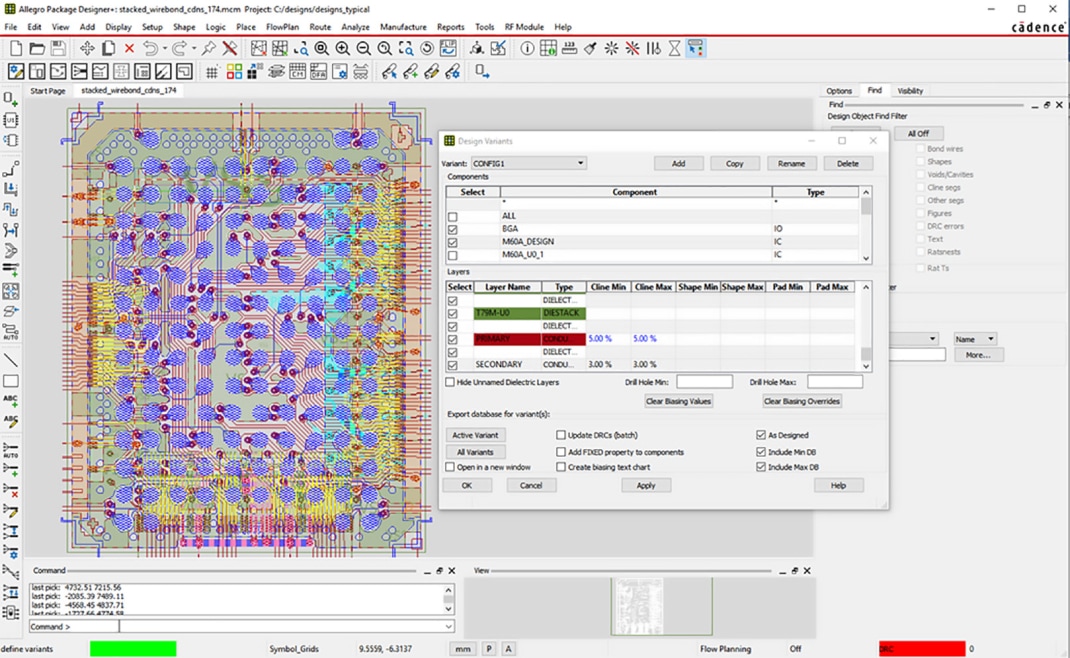

借助我们先进的二维(2D)与三维(3D)设计规则检查(DRC),充分释放您的塑料球栅阵列封装 (PBGA)设计潜力。我们的尖端技术会细致检查每一处角度与径向布线,确保您的引线键合型 PBGA 不仅符合、更能超越行业标准。通过采用我们的 DRC 流程,您不仅能优化性能,还能确保产品在最严苛 的应用场景下具备可靠性与长使用寿命。凭借我们全面的 DRC 分析,提升您的设计水平,突破设计可能 性的边界。

用户认可

听听客户怎么说

能力

精通现代集成电路封装:从多芯片设计到全面的系统级管理

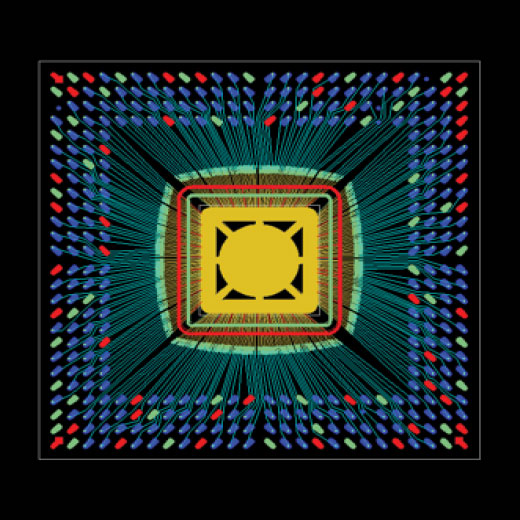

高效能多芯片裸片封装实现

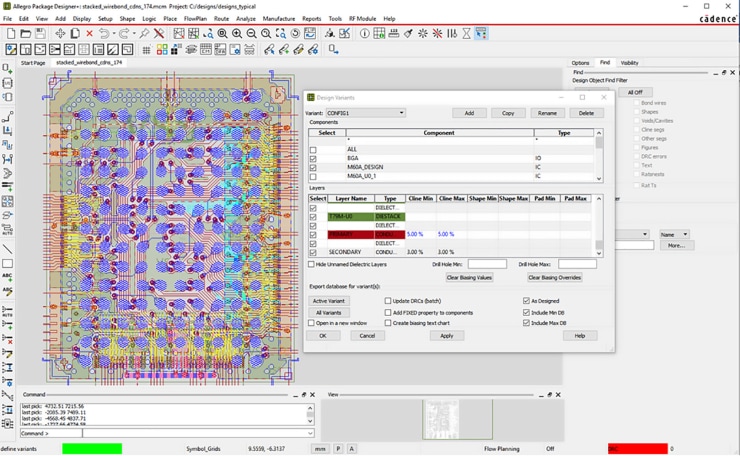

Allegro X Advanced Package Designer支持设计团队轻松完成多芯 片裸片封装设计,可实时创建库文件、实现芯片裸片堆叠、设计嵌入式空腔,并依据行业领先的设计规 则生成定制化制造输出文件。

产品

下一代集成电路封装解决方案:弥合性能差距

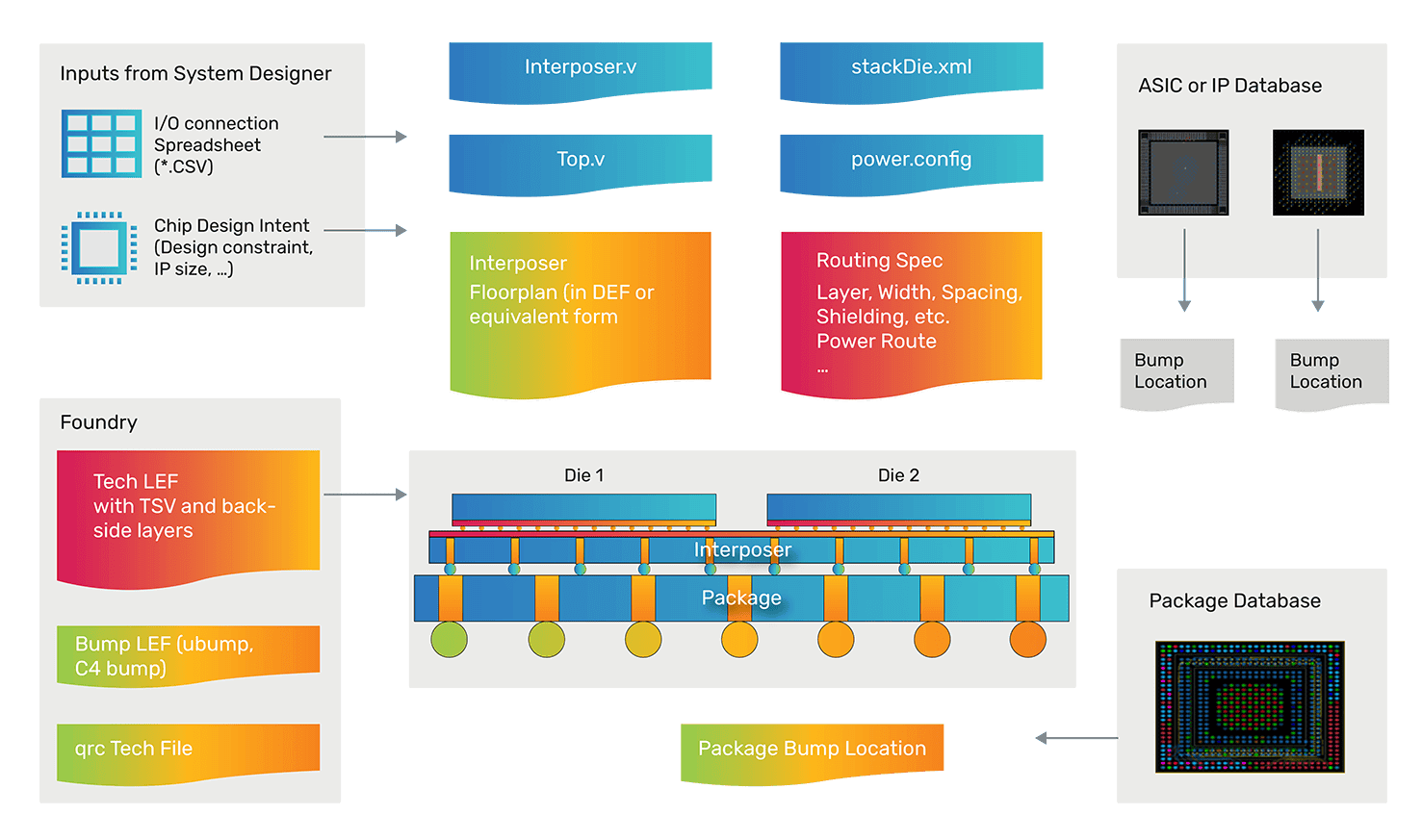

Allegro X 先进封装设计工具的硅布局选项旨在革新扇出型晶圆级封装(FOWLP)技术,凭借其轻 薄设计、更高性能与成本效益,满足移动市场的需求。这款创新性工具可简化设计与验证流程,实现集 成电路(IC)后端团队与封装基板团队的高效衔接。

✓ 针对扇出型晶圆级封装(FOWLP)设计优化:专为扇出型晶圆级封装(FOWLP)特有的设计与 制造挑战定制,满足现代移动计算的需求。

✓ 晶圆级实现:与集成电路(IC)制造流程相契合,有别于传统基于有机基板的集成电路封装制造 方式。

✓ 金属密度管理:适用于超薄封装(500 至 1000 微米)的局部金属密度创建与编辑工具。具备通 过网状金属和焊盘实现跨设计平衡的工具。

✓ 先进的 GDSII 掩模处理:支持为扇出型晶圆级封装(FOWLP)制造创建高性能掩模。

✓ 与 Cadence PVS 的无缝集成:可直接集成至设计与掩模验证流程,并依据 PDK 规则集完成签核。PVS 验证问题可在设计画布及约束管理器中直接高亮显示并生成报告。

✓ 支持 Windows(64 位)和 Linux(64 位)系统。

✓ 需要搭配 Allegro X 高级封装设计工具以及 Cadence PVS(二者均单独销售)。

功能

实现无缝集成电路封装的集成解决方案

Allegro X 先进封装设计平台通过将卓越的灵活性、先进的分析功能以及封装优化整合到无缝工作流程中,为下一代集 成电路(IC)封装设计提供支持。该平台为设计效率与创新设立了新标准,可支持尖端技术,以满足现代电子领域的需求。

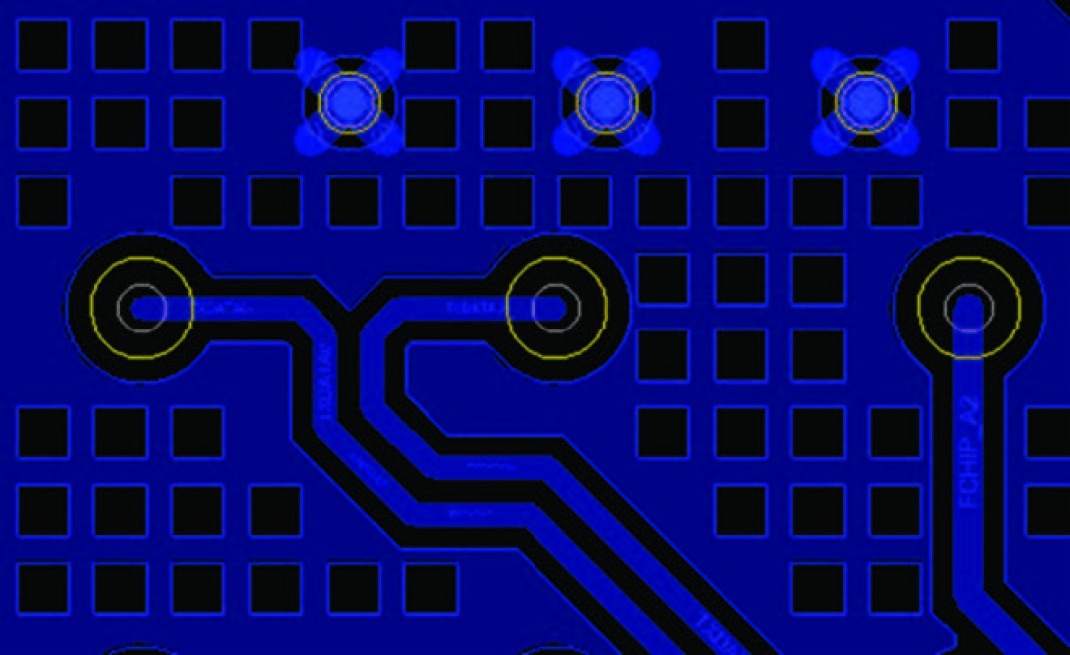

适用于单芯片与多芯片封装的完整解决方案,具备 “构建即正确” 的数据库、 物理设计规则的实时设计规则检查(DRC)以及电气约束功能。

受约束驱动的推挤式交互式布线、自动交互式布线以及全自动布线。

Allegro X DesignTrue 可制造性设计(DFM)规则检查集成功能,凭借卓越的灵 活性、尖端技术及全面的分析工具,为效率与创新树立了新的行业标准。

灵活的互连模型,支持网表、原理图以及 “即时生成式” 互连。

突破传统设计流程的局限,让您能够在完全沉浸式的三维环境中,对复杂导线和 设计规则进行可视化呈现与检查。

用于控制超薄封装(厚度 500 至 1000 微米)翘曲的局部化、高精度控制金属密 度生成与编辑工具。

用于跨设计平衡的金属密度工具集,支持网格状金属和网格状焊盘。

充分利用 GDSII 掩模处理的卓越功能,该处理是印制电路板(PCB)和半导体 器件制造过程中的关键环节。

这种动态协同效应为设计验证和签核提供了卓越的平台,可直接对接工艺设计套的无缝且强大的集成 件(PDK)规则集。

通过提供一套与集成电路(IC)制造流程高度契合的、从设计到验证的完整流 程,为无晶圆厂半导体公司的 IC 后端设计团队以及 IC 封装基板设计师拓展 IC 封装设计工具的功能。

支持并整合复杂多芯片与分立基板组件的设计概念探索、捕捉、构建、优化及验证流程。