PSpice中SPWM方波信号的生成

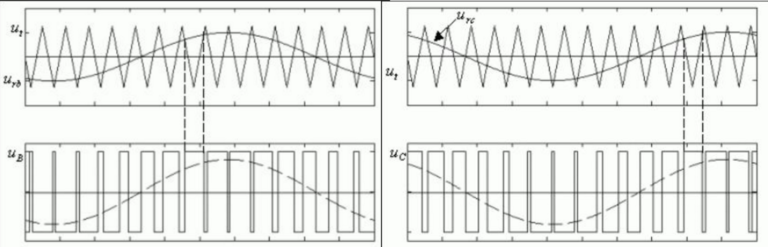

一、SPWM原理 以正弦波作为逆变器输出的期望波形,以频率比期望波高得多的等腰三角波作为载波(Carrier wave),并用频率和期望波相同的正弦波作为调制波(Modulation Wave),等调制波与载波相交时,由它们的交点确定逆变器开关器件的通断时刻,从而获得在正弦调制波的半个周期内呈两边窄中间宽的一系列等幅不等宽的矩形波。 二、SPWM分类 从调制脉冲的急性上,分为: 单极性脉宽调制 在

一、SPWM原理 以正弦波作为逆变器输出的期望波形,以频率比期望波高得多的等腰三角波作为载波(Carrier wave),并用频率和期望波相同的正弦波作为调制波(Modulation Wave),等调制波与载波相交时,由它们的交点确定逆变器开关器件的通断时刻,从而获得在正弦调制波的半个周期内呈两边窄中间宽的一系列等幅不等宽的矩形波。 二、SPWM分类 从调制脉冲的急性上,分为: 单极性脉宽调制 在

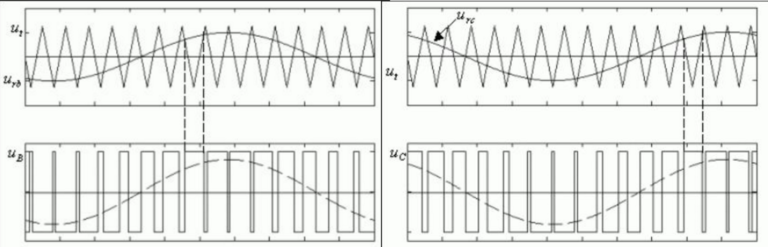

本文要点 寄生电容的定义 寄生电容影响电路机理 消除寄生电容的方法 当你想到寄生虫时,你可能会想到生物学上的定义——一种生活在宿主身上或在宿主体内的有机体,从宿主身上吸取食物。 从这个意义上说,寄生虫可能是巨大的麻烦或导致严重的健康问题。 当然,作为一个PCB设计人员,您可能知道另一种寄生虫——寄生电容。 虽然您不必担心电路中的生物寄生,但了解如何消除寄生电容可以帮助提高PCB设计中的信号完整性和

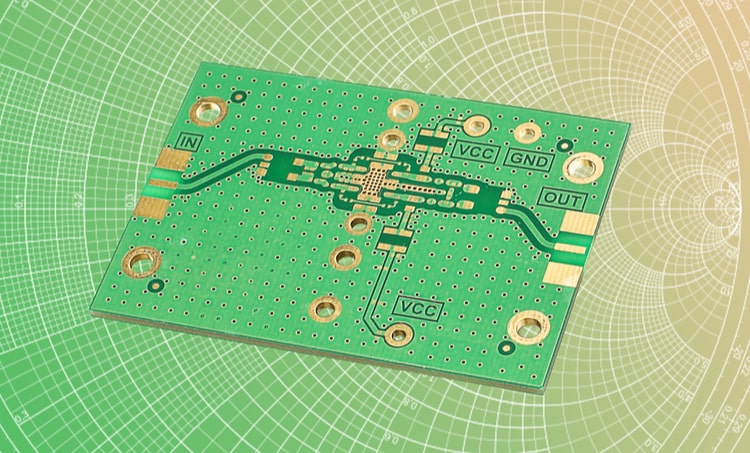

01什么是Temp Group? 所谓的Temp Group,就相当于临时创建的Group组,用于很多元素的选择,用于一起执行某项命令,比如移动、复制等等。执行完命令之后呢,Group组就打散了,不存在了,今天我们以移动命令为例,讲解一下如何使用Temp Group功能。 第一步 执行移动命令,Edit-Move功能,在Find面板中选择需要移动的元素,比如移动元器件与过孔,如下图所示; 执行移动

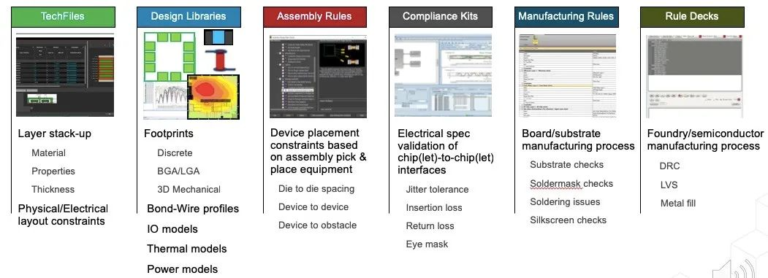

在今年的 IMAPS(International Microelectronics Assembly and Packaging Society,国际微电子装配与封装学会 )大会上,Cadence 资深半导体封装管理总监 John Park 发表了关于封装组装设计套件(Package Assembly Design Kits,简称 ADK)的演讲:什么是 ADK,以及 ADK 能为封装设计带来哪

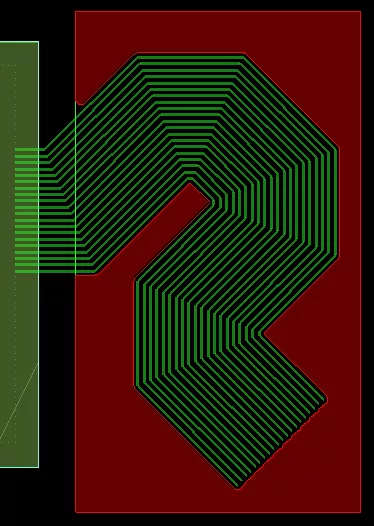

DDR布线技术的重要性 在如今的印刷电路板设计中,双数据速率(DDR)存储器非常普遍。许多设计都会用到DDR存储器配置的不同版本,这需要在布局中使用特定的布线模式。DDR的名称来源于其能够在每个时钟周期内发送和接收两次信号,是原先的单数据速率(SDR)存储器速率的两倍。由于速率增加了一倍,必须在布设DDR存储器的走线时保持更严格的参数,以满足性能规范。存储器电路设计的关键在于满足其时序规范。每个信

本文要点: 所有的物理系统在运行动态中都会表现出一些瞬态行为,电子产品也是如此 瞬态分析技术可以帮助了解不同电气状态之间的转换 当检查测量数据或软件仿真数据时,一些基本的瞬态分析技术可用于了解电气状态之间的转换 当打开或关闭 LED 时,随着光线变亮或变暗有一个缓慢的过渡。这种类型的瞬态行为非常简单,但这是一个电子系统改变状态时的基本反应。使用瞬态分析可以充分理解时域中的信号转换,以及它们与重要系

复用模块(Reuse Module)是布局中可以重复应用的部分,可以应用在相同的设计上,也可以应用在存在类似电路的不同设计上。 非正式的模块可以透过place replicate命令生成,以便快速应用于模块复用的电路设计中。正式的模块通常与电路的电路图相关联,以便在放置过程中加以利用。 为了方便在其它设计中能应用模块,位置复制流程通常是以建库的方式完成。为了维护设计意图和完整性,在 Allegro

本文要点 部分元等效电路 (PEEC) 法是一种依靠麦克斯韦方程积分表述的电磁仿真 PEEC 方法的基本公式是麦克斯韦方程的电场积分方程 (EFIE) 全波解 PEEC 方法的优点包括: 只有系统中的材料被离散化,这减少了单元的数量 解的变量也是电路变量 您是否注意过电子产品上的 CE 符号?这个符号表明产品符合安全、健康、环境和电磁兼容 (EMC) 标准。 CE 符号表明产品符合 EMC 标准

如果您曾经尝试过去除设计的某个区域,您可能会发现这个过程比想象的更加复杂。 如果我们使用显示元素(show element)功能来选择该区域中的铺面,就会选中整个形状。这样可能会超出到想要修改的区域之外;区域周边走线也会较为曲折。我们是否要删除整个 cline,再重新连接其他的线?是否会分段删除、减少需要替换的布线,而反而留下了一些间距奇怪的连接点需要再小心地接上?过孔要如何处理?如果它们与要去除

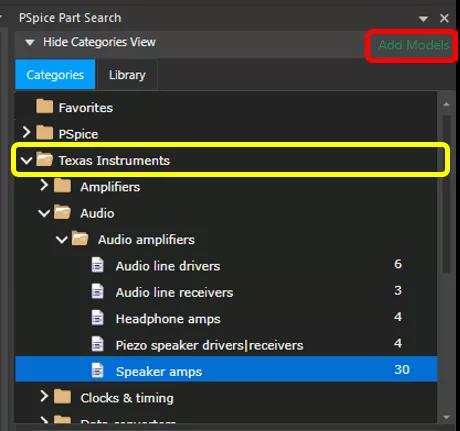

2019年末 Cadence发布了PCB 产品线的SPB 17.4主版本,并在之后持续发布更新。在这个新版本中,PSpice增加了许多新功能,性能也大幅度提升。全方位满足用户需求。 本文向大家介绍在PSpice17.4中增强的功能有哪些。 1、程序主题增强 在17.4版本中,PSpice和PSpice高级分析的主题改为黑色,黑色主题可以减少功耗,提高可视性,并使屏幕更易于阅读。 用户可以自定义应用

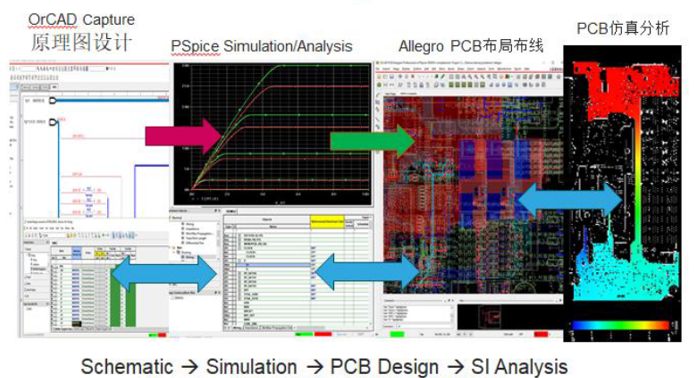

各家EDA厂家,基本都提供有原理图仿真工具,其中,Cadence公司的PSPice是业界应用较广泛的原理图仿真工具,那么,为什么说它是原理图仿真的优选工具呢?这里,说说它的几大特点: 一、一体化集成 早期的Pspice,是需要用户手动输入Pspice Netlist以及Profile,才能进行仿真。现在的Pspice,直接集成到Cadence的Capture和Concept中,实现了从原理

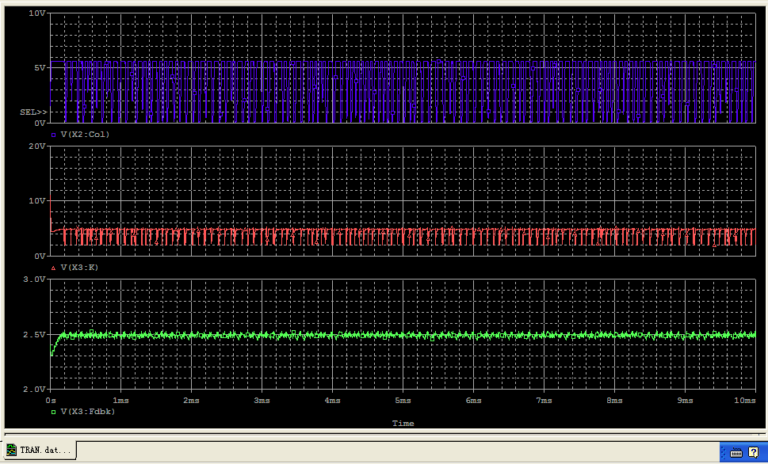

输入电压(最高输入时):350Vdc,输出负载1.3Ω: 1、输出电压波形 输出电压Vout的波形图 从上图中可以看出:输出电压稳定在5.4V,建立稳态时间约0.2ms。 取2.0ms-2.2ms波形放大如下图所示: 从上图中可以看出:建立稳态输出后,在2ms-10ms内最小输出电压为5.27862V,最大输出电压为5.48191V,正负波动电压小于0.1v(<2%)。 2、RtCt、电流采