PSpice用于开关电源仿真案例分析(二)

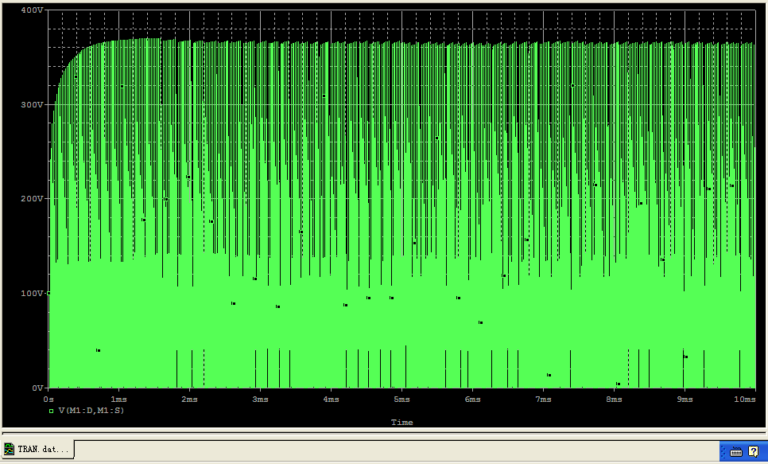

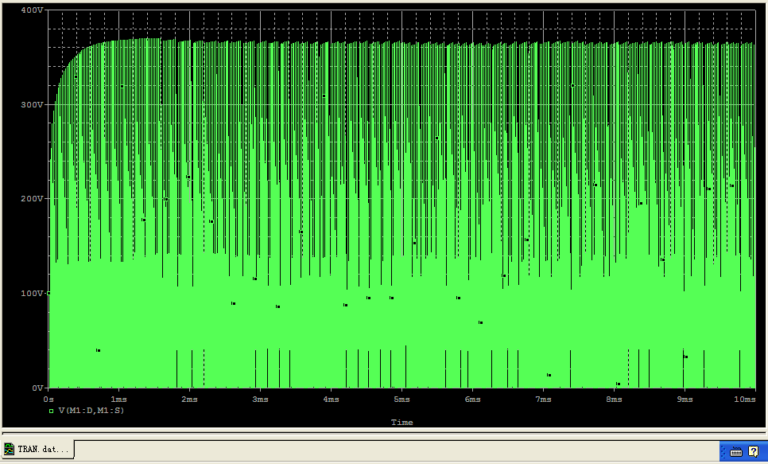

设计电路原理图 注:本设计主要考虑反激式变换器的工作特性,对于变压器的生产绕制工艺暂不考虑。根据以上计算得出的主要参数,画出电路的原型设计。 隔离反激式变换器设计原理图 设计电路的瞬态仿真波形 瞬态仿真参数设置: 输入电压(最低输入时):100Vdc,输出负载1.3Ω: 仿真时长:10ms 1、输出电压波形 输出电压Vout的波形图 从上图中可以看出:输出电压稳定在5.4V,建立稳态时间约1.2m

设计电路原理图 注:本设计主要考虑反激式变换器的工作特性,对于变压器的生产绕制工艺暂不考虑。根据以上计算得出的主要参数,画出电路的原型设计。 隔离反激式变换器设计原理图 设计电路的瞬态仿真波形 瞬态仿真参数设置: 输入电压(最低输入时):100Vdc,输出负载1.3Ω: 仿真时长:10ms 1、输出电压波形 输出电压Vout的波形图 从上图中可以看出:输出电压稳定在5.4V,建立稳态时间约1.2m

案例简介: 该设计是应用TI公司电流模式PWM控制器芯片UC2845来设计隔离反激式变换器,设计的基本要求如下: 输入电压:90VAC-264VAC(100VDC-350VDC); 输出电压:5.4V; 输出电流:4A; 开关频率:100KHz; 技术分析 一、工作原理 如图1所示,隔离反激式变换器的工作原理是: 开关导通时, 能量存储于变压器原边的电感中,注意变压器的同名端,当开关关断时,漏极电

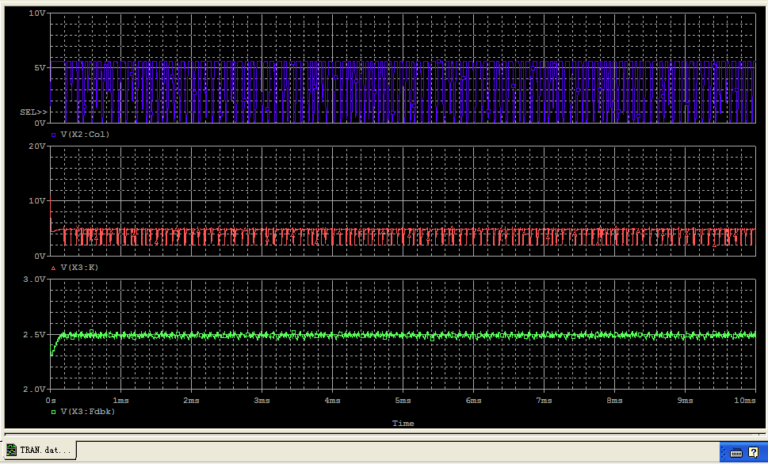

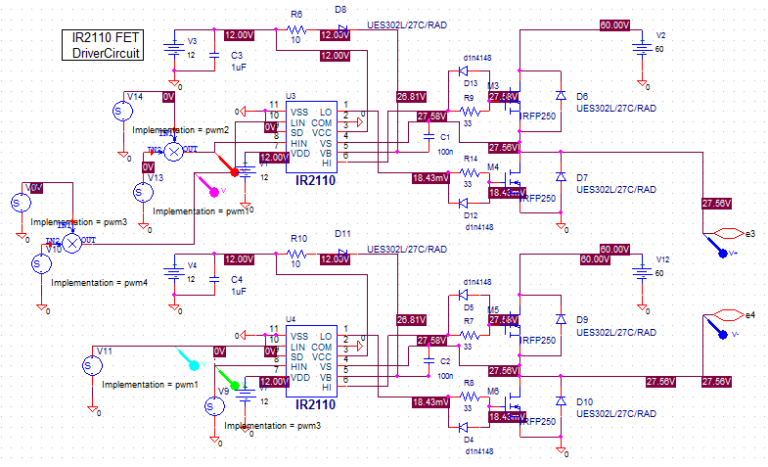

IR2110是International Rectifier Company 利用自身独有的高压集成电路及无门锁CMOS 技术,开发的大功率MOSFET和IGBT专用栅极驱动集成电路,已在电源变换、马达调速等功率驱动领域中获得了广泛的应用。该电路芯片体积小(DIP-14、SOIC-16),集成度高(可驱动同一桥臂两路),响应快( ton /tof = 120/94 n s ),偏值电压高(<

大多数封装基板的设计设想是基于如果零件安装在正面,那么封装基板就会置于主 PCB 上。这意味着,BGA 的焊球位于横截面的底层、裸片安装在上面。 对于引线键合裸片来说,裸片仍然是朝上放置(裸片焊盘位于远离基板的位置)。但是,对于倒装芯片,芯片朝下放置;芯片被翻转,并安装在主 BGA 顶部布线层上表面的 Bump 上。当封装完成后,BGA 会创建一个零件,供 PCB 设计工程师使用。 那么,如果我们

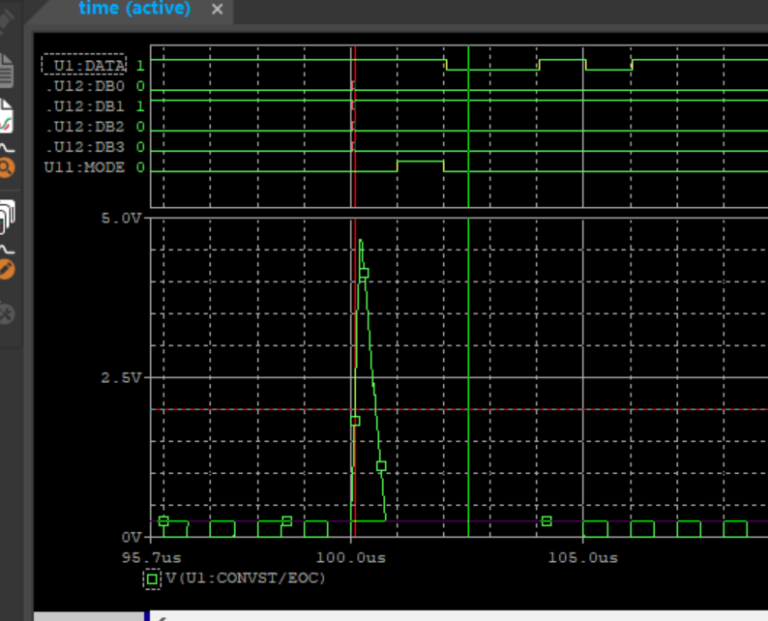

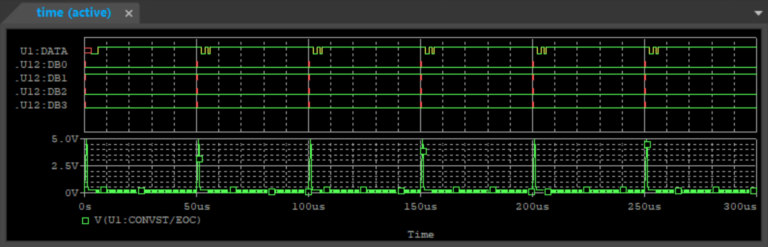

技术专题|串行模数转换器PSpice仿真分析(二) 《技术专题|串行模数转换器PSpice仿真分析(一)》我们使用了ADCSER4进行仿真,为了提高转换精度,这次我们使用ADCSER24。 在Capture中打开ADC_DEMO.opj,把U1替换成ADCSER24,原理图如下: 选中AD转换器,点击鼠标右键,选择Desend Hierarchy,可以进入

技术专题|串行模数转换器PSpice仿真分析(一) 在pspice的仿真中,经常需要使用模数转换,往常,一般忽略模数转换部分,只对其它部分进行仿真。其实,在pspice中,也提供了模数转换模型库,可以在电路中对AD/DA转换进行仿真。 在pspice提供的仿真库中,有一个dataconv库,里面就包含了AD/DA模型。其位置位于“安装路径”\SPB_17.4\tools\captur

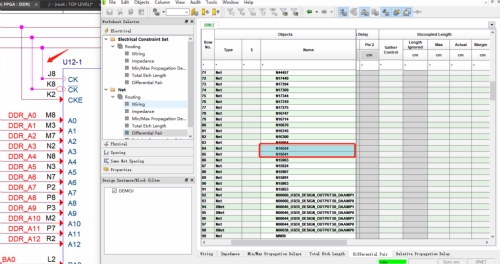

随着高速电路越来越普及,电路板设计密度越来越大,对于通讯行业、商用服务器、以及工控、军工领域对高速电路需求较多性能要求较高的地方,PCB的布线阻抗成为了一个必须关注的重要话题。我们知道在整个信号系统的传输链路里面,PCB板级的设计中会有较多的情况造成阻抗不连续或者突变。比如布线线宽的改变、锐角走线、厚度的不一

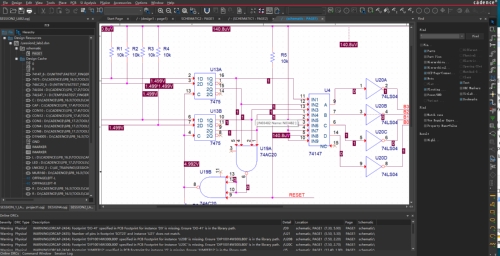

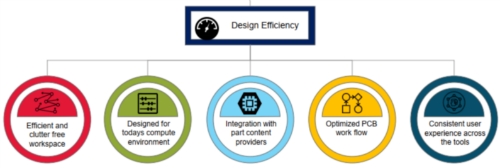

CadenceOrCADCapture是一款多功能的PCB原理图输入工具。新发布的OrCADCapture17.4作为行业标准的PCB原理图输入方式,是当今最流行的原理图输入工具之一,具有简单直观的用户设计界面。OrCADCapture17.4有很多新功能更新,功能操作、界面主题、图标、布局排列都有一些新变化,今天带大家体验下OrCADCapture17.4版本。1.简化的项目

CadenceOrCADCapture是一款多功能的PCB原理图输入工具。新发布的OrCADCapture17.4作为行业标准的PCB原理图输入方式,是当今世界最流行的原理图输入工具之一,具有简单直观的用户设计界面。OrCADCapture17.4有很多新功能更新,我们梳理了很多资料后发现,OrCADCapture和Allegro已经支持约束规则的双向设置及同步啦,这个双向的规则

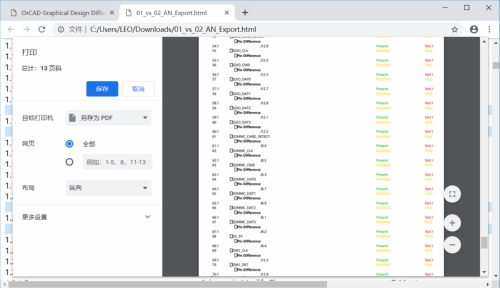

很多时候,我们的DSN原理图都会设计修改多次,而且出现很多文件版本,每个版本中具体有那些电路被删除或者被新增,以往的设计工具都不能给出明确的结果和报告。在CadenceOrCAD17.4的DSN设计差异对比功能对电路板的差异对比进行了加强。可以选择不同的版本的DSN原理图文件夹或者原理图图纸页面做差异化对比,比对结果可查看存在差

CadenceOrCADCapture是一款多功能的PCB原理图输入工具。新发布的OrCADCapture17.4作为行业标准的PCB原理图输入方式,是当今世界最流行的原理图输入工具之一,具有简单直观的用户设计界面。OrCADCapture具有功能强大的元件信息系统,可以在线和集中管理元件数据库,从而大幅提升电路设计的效率。OrCADCaptureCIS提供了完整的、可

CadenceOrCADCapture是一款多功能的PCB原理图输入工具。新发布的OrCADCapture17.4作为行业标准的PCB原理图输入方式,是当今世界最流行的原理图输入工具之一,具有简单直观的用户设计界面。OrCADCapture具有功能强大的元件信息系统,可以在线和集中管理元件数据库,从而大幅提升电路设计的效率。OrCADCaptureCIS提供了完整的、可