OrCAD X

快速设计、精准设计、协同设计

概述

兼顾各方需求的统一 PCB 设计方案

OrCAD X 是一款全面的 PCB 设计平台,它在单一、可扩展的环境中整合了原理图输入、混 合信号仿真、PCB 布局、供应链智能、设计中分析以及制造准备等功能。该平台采用直观的界面和以性能为核心的工作流程,消除了设计各阶段之间的衔接障碍,同时能够满足当今高密度、高速率及基于标准的设计需求。 凭借在自动化、约束管理、云端协同及数据安全方面的显著提升,OrCAD X 经专门研发,可简化从概 念设计到生产制造的完整电子设计流程。其具备出色的灵活性,无论是用于简单的消费级物联网设备, 还是面向医疗植入物、航空航天控制电子设备、汽车功率模块等安全关键型系统,均能发挥高效作用。 无论针对何种市场领域,OrCAD X 都能助力团队更快完成设计、更早开展验证,以更少的风险和迭代次数将产品推向市场。

应用

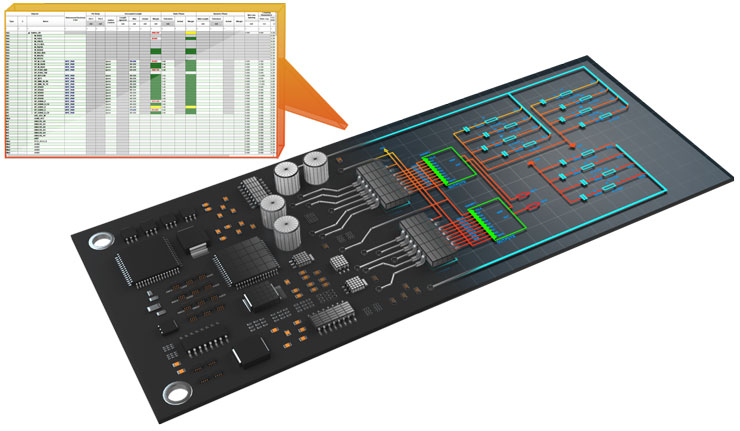

OrCAD X 原理图设计工具(OrCAD X Schematic)提供了业界最完善的原理图输入环境之一,既融合了数十年积累的易用性改进成果,又具备现代系统设计所需的深度功能。工程师可通过分层方式组织项目、复用成熟的子电路,并在原理图输入阶段就应用电气约束与物理约束。OrCAD X 的物料清 单(BOM)管理功能是其核心差异化优势,能将原理图物料清单与实时供应链情报保持同步。该功能 以 Sourcengine™(注:专业供应链数据平台)为技术支撑,通过这一集成可获取来自数千家供应商的 超过 10 亿种元器件信息。设计师在绘制电路时,便能查看元器件的生命周期状态、交货周期、合规数 据及价格预测。此外,预测分析功能可在设计早期识别元器件淘汰风险、供应短缺问题或成本风险 — — 助力工程决策与采购策略保持一致,避免后期重新设计。

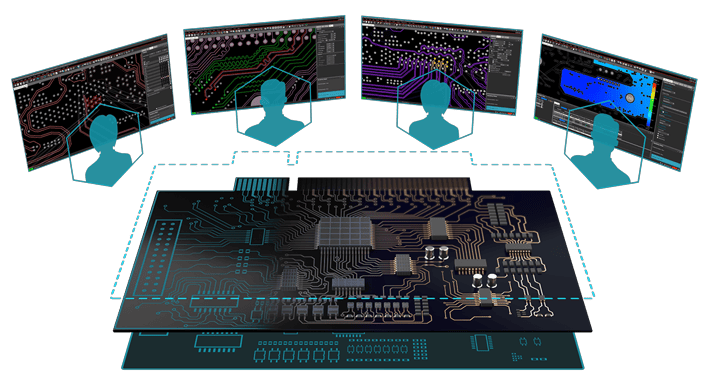

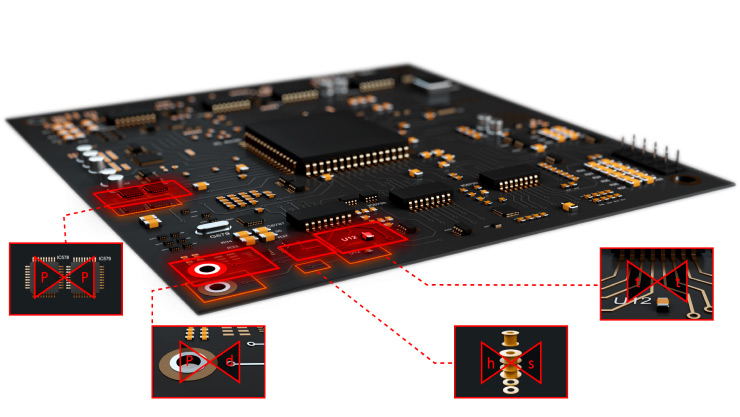

在原理图中定义的约束通过统一的约束管理器(Constraint Manager)进行管理,该管理器 可使差分对、时序、长度匹配及信号类别相关规则无缝同步至 PCB 布局环节。双向同步功能确保引脚或门电路交换、元器件替换、位号修改等更新在各设计领域(此处特指原理图与 PCB 布局) 保持一致。这种紧密集成的方式能够避免错误,并减少因人工协调所浪费的时间。

OrCAD X 的最新更新新增了在原理图内部直接集成设计评审与标注的功能。相关人员无需依赖静态 PDF 文件或独立的评审工具,而是可以在实时原理图上直接添加注释、突出显示关键内容,并提供可执 行的反馈意见。这些标注与设计数据库一同存储,便于追溯且易于处理。此项改进缩短了评审周期,提 升了设计团队与验证团队之间的沟通效率,并确保每一次设计修订都能整合来自工程、制造及合规等相 关方的意见。综合来看,这些功能使得 OrCAD X 原理图设计工具不仅是一个原理图输入环境,更成为 一个集协同合作、供应链情报与设计准确性于一体的平台。

综合来看,这些功能使得 OrCAD X 原理图设计工具不仅是一个原理图捕获环境,更成为一个 集协同合作、供应链情报与 “构建即正确” 设计意图于一体的平台。

功能

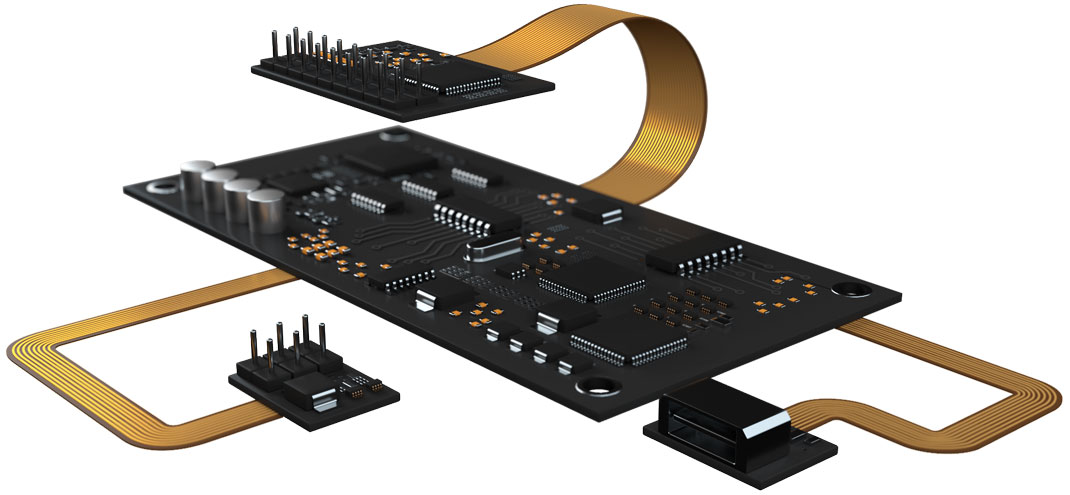

OrCAD X 叠层管理器支持先进的刚柔结合结构设计,允许在单个 PCB 内定义多个叠层区域。每个 区域均可独立配置,包括选择合适的铜箔层、介电材料、阻焊层、表面处理、加强板以及其他制造属性。 这种精细化配置能力确保设计师能够精准建模真实的刚柔结合结构,避免在制造环节出现意外问题。

设计师可通过添加折弯线、设置折弯角度与折弯顺序,进一步完善叠层区域设计,构建出电路板 的真实三维交互式模型。通过结合场景可视化折弯效果,工程师能够评估导线、过孔和元器件如何与 机械约束条件相互作用,从而大幅降低柔性区域出现铜箔断裂或分层的风险。OrCAD X 会自动应用相 关的禁布区、约束区域以及可选的设计空间,确保元器件布局与布线符合机械限制要求。

轮廓布线功能能够识别柔性区域的独特几何形状,并加快不同区域间的连接速度,从而提升刚柔结 合板的布线效率。OrCAD X 将设计中规则与约束执行相结合,即便面对高度复杂的柔性几何结构,也能 确保 “构建即正确” 的设计在首次发布时就具备可制造性。

为何选择 OrCAD X

- 统一的原理图、仿真、布局、库及制造流程

- 具备实时供应链智能的物料清单(BOM)管理

- 真正的并行 PCB 布局

- 由 Sigrity X 技术支持的设计中信号完整性 / 电源完整性(SI/PI)探究

- 支持云技术的资料、库及评审管理

- 无缝的机械计算机辅助设计(MCAD)集成与云平台协作

- 通过 ISO 26262 认证,适用于汽车安全关键工作流程

- 可扩展至 Allegro X,以支持先进技术

- 人工智能赋能,助力提升下一代生产力

应用

- 消费电子与物联网领域:结构紧凑、快速交付且成本目标严格的电子产品

- 汽车领域:动力传动系统、信息娱乐系统、传感器

- 医疗与可穿戴设备领域:小型化、高可靠性电子产品

- 航空航天与国防领域:坚固耐用、飞行关键型电路板

- 工业自动化领域:机器人技术、电力系统及控制系统