- 准确的分布式模型(包括 TSV),可反映真实的电路行为

- 有效提取电源网格结构和 I/O 信号互连结构的互感和耦合电容

- 最大限度提高精度,且芯片模型紧凑、引脚密度高

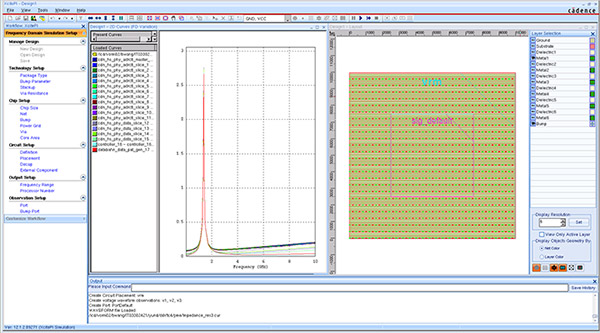

Cadence® Sigrity™ XcitePI™ Extraction 技术可以支持 GDSII 或 LEF/DEF 格式的芯片版图数据,生成由完全分布式的 PDN 和多个 I/O 网络组成的,包含所有信号、电源和地网络之间的电磁耦合效应的综合 SPICE 模型。这些模型可与封装和PCB电路板模型结合,用于进行芯片/封装/电路板的电源完整性 (PI) 分析或兼顾电源感知的信号完整性 (SI) 分析。

通过一系列的电气性能评估与可视化选项,XcitePI Extraction流程可以为设计迭代提供有效支持。这些选项显示了改变电容位置、bump、焊盘和电源网格设计时的影响,帮助设计团队避免昂贵的后期重新设计。

主要功能

- 快速进行what-if假设实验,以达到改进设计性能的目标

- 通过压缩整个多层电源、接地与/或信号连接模型,使得电路规模更加紧凑

- 在芯片设计的任何阶段,即使芯片尚未完成,也能进行简单轻松的仿真

- 生成全芯片 PDN 的 SPICE 模型,用于芯片/封装/PCB电路板仿真

- 生成芯片级的信号/电源/地耦合的SPICE模型,用于高速通道和总线的芯片/封装/电路板分析

- 包括MCP连接协议,可轻松实现与封装和 IBIS 模型的连接

- 所生成的模型包括TSV结构的寄生效应

- 将潜在的芯片性能问题可视化

- 评估片上去耦电容的实现方案

- 对去耦电容、bump、金线、过孔尺寸和位置进行what-if假设分析