供电网络 (PDN) 设计

集成Layout设计和仿真分析于一体的约束驱动设计方案

主要优势

- 基于团队的约束驱动设计流程:由PCB layout专家执行初级PI分析;由此节省下来的时间,使PI专家得以集中精力攻克高级分析任务

- 自动完成交流(AC)和直流(DC) PI分析设置,并可对设置进行复用,从而轻松便捷地实现更改后的设计分析

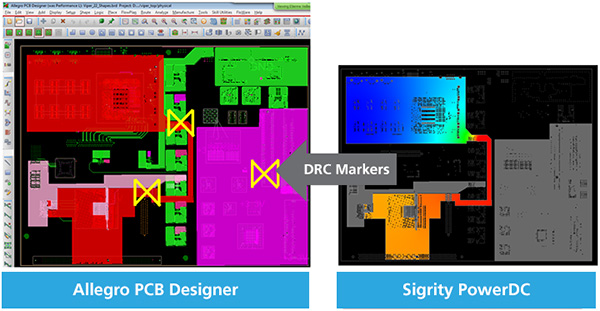

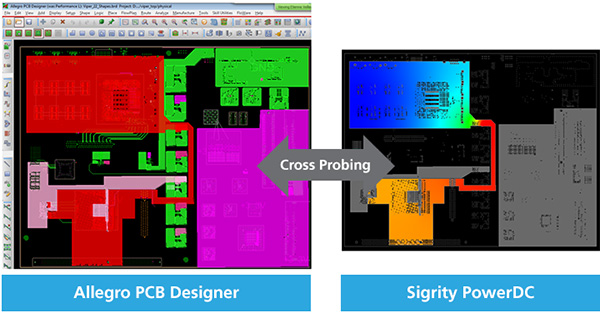

- 使用设计规则检查(DRC)标记和交叉检测,轻松识别可满足PDN特定要求所需的布局、布线更改

在PCB设计中,由于多方因素共同导致了电源完整性问题,因而直流分析至关重要。随着电路的核心电平持续下降,低于1.2V的情况在如今已十分常见。而随着电压的降低,电流的需求则会增加(直流压降= I * R)。电子器件的小型化使得电路板层数减少而密度增加,从而减少了电源网络的可用面积。过孔周围的反焊盘不仅会穿透电路板更会产生重叠,雪上加霜(瑞士奶酪效应)。

此外,PCB设计人员还面临着额外的供电网络(PDN)挑战:首先是来自硬件设计师或电源完整性(PI)工程师的条条指令,这些指令通过电子邮件、电话、经验规则等传达给PCB设计人员。而PCB设计人员则必须将所有这些指示和规则应用于多个供电网络。一经完成,则又将面临新的额外任务——例如: “你能将面积缩小20%吗?” 、“你能去掉两个平面层和五个电容吗?”、以及老生常谈的问题“你能提前完成吗?”

复杂的电路板可能有几十个电源通道、数百个电源网络(包括滤波网络)以及大量构成PDN的组件。对数百页原理图进行整理以确认PDN在逻辑上的连接关系是一大痛点。然而,当在设计过程后端,电源完整性分析要求指定所有网络和组件并为其建模时,一切则是痛上加痛:仅仅完成设置都可能需要花费几天甚至几周的时间。

另一个挑战则是如何沟通设计问题:PI工程师如何向PCB设计人员提出问题并进行指导?PCB设计人员如何与PI工程师沟通解决方案?PCB设计人员如何确定解决方案的可行性?我们的集成功能可帮助PCB设计人员和PI工程师有效解决如上问题。此外,如果PI工程师尚未传达指导意见,PCB设计人员可以使用工具自动完成初级电气约束条件计算,从而顺利开展工作而不必坐等浪费宝贵产品开发时间。

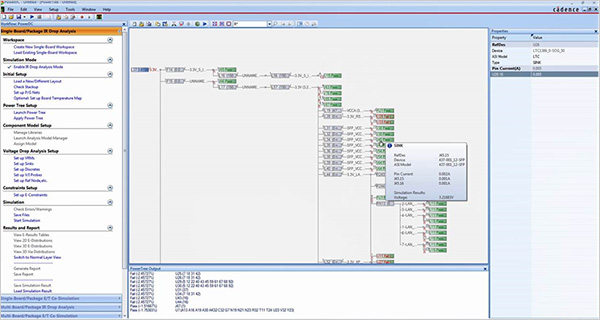

PowerTree图形环境

Cadence Allegro® PowerTree™ Technology允许PCB layout专家和硬件设计师在PDN拓扑结构中以图形方式查看源端/负载端的定义、离散器件的参数值、模型名称、网络名称、去耦电容值以及目标阻抗约束等。

硬件设计人员更可以轻松一键实现早期可行性检查分析。通过读取原理图数据,即可确定PDN拓扑结构是否已被正确捕获并符合电源设计标准。

通过由硬件设计师和PCB layout专家分担执行简单的分析,PI专家可以由此专注于更专业的分析。PowerTree technology的自动化设置,使得PI专家甚至设计新手们不再花费数天或数周的时间进行PI分析的参数设置。将PowerTree数据应用于物理设计使得仿真变得极为简单,只需几个按钮即可完成任务。

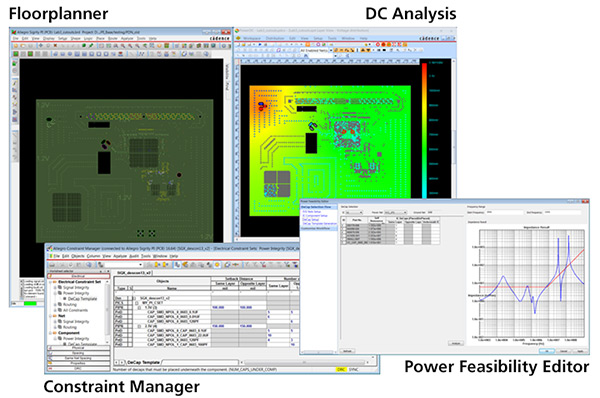

集成功能

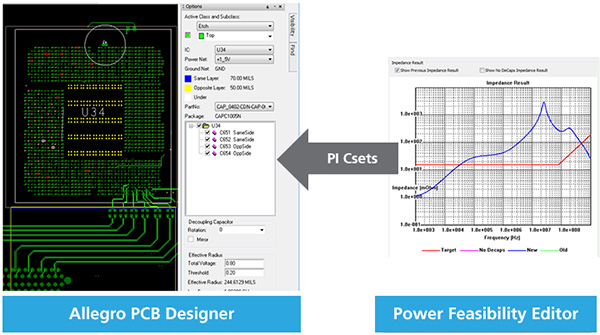

去耦电容放置规则要求PI专家进行PI分析之后再确定每个IC的理想去耦方案。此外,PI专家必须创建PI约束集,才能指导PCB设计人员把去耦电容放置在合适的位置上。

由PI设计人员的规则所决定的DRC标记被标注在Cadence Allegro PCB Designer中。这些标记使PCB设计人员能够理解PI工程师发现的PDN问题并进行相应处理。

Allegro PCB Designer和分析结果之间的交叉检测使PCB设计人员能够使用可视化分析结果来确定PCB中需要改变的内容,例如增加电源铜皮面积的大小、添加过孔、增加电源平面的层数等。

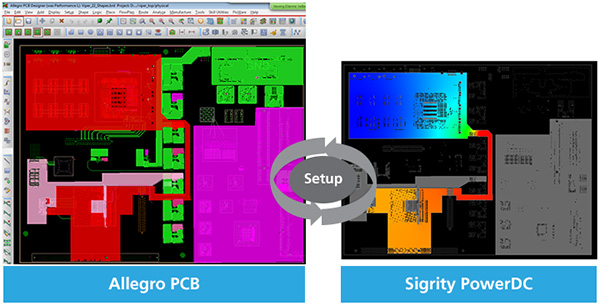

复用PI专家的设置可以令PCB设计人员对设计进行修改并再次仿真分析修改后的成果,同时也可对原始设置进行更改。

Allegro / Sigrity集成

Allegro Sigrity™ PI Base集成了Allegro和Sigrity技术,用于PCB、IC封装和系统级封装(SiP)设计的PI分析,并通过集成layout设计和仿真分析于一体实现了约束驱动设计。Allegro Sigrity PI Base的主要优势包括:

- 可靠的Sigrity分析引擎

- 从原理图生成的PowerTree数据可自动执行仿真设置

- 业界首个约束驱动的PI设计流程,可执行去耦电容的选择和布局

- 直流分析后自动进行layout设计和分析结果之间的交叉检测,可轻松识别并解决物理设计(PCB电路)中的直流压降问题

- 针对版图设计师和PI工程师

- 用于详细分析、合规性和评估的附加选项