3D-IC(三维集成电路)设计挑战与需求

概述

随着对更高密度、更大带宽和更低功耗的需求不断提升,许多集成电路(IC)设计与封装团队正密 切关注多芯片及芯粒的垂直堆叠技术。这种被称为三维集成电路(3D-IC)的技术,相比传统的单芯片 平面设计具有诸多优势。一些人用 “超越摩尔定律(More-than-Moore)” 一词来描述这项新技术的发 展潜力。通过芯片堆叠以及先进封装技术实现集成,设计人员能够在尺寸小得多的外形结构中融入更多 功能,同时提升性能并降低成本。3D-IC 架构可将逻辑芯片、存储芯片、模拟芯片、射频芯片(RF)等 多种同类型及异类型芯片 / 芯粒集成到单一设计中。这为单片系统级芯片(SoC)集成提供了一种替代 方案,对于设计人员希望在单一设计中实现的所有功能而言,该方案有望避免为采用新一代工艺节点而 投入高昂成本。凭借在模拟与数字实现、封装以及印制电路板(PCB)设计工具方面的全面产品布局, Cadence 在支持 3D-IC 技术变革方面占据独特优势,并有能力为 3D-IC 的高性价比设计提供所需功能。

介绍

三维集成电路(3D-IC)预计将在网络、图形、人工智能 / 机器学习(AI/ML)以及高性能计算等 领域产生广泛影响,尤其适用于需要超高性能、低功耗设备的应用场景。具体应用领域包括多核中央处 理器(CPU)、图形处理器(GPU)、分组缓冲器 / 路由器、智能手机以及人工智能 / 机器学习 (AI/ML)应用。

尽管业界对这项新兴技术抱有浓厚兴趣,但它仍处于早期发展阶段。目前缺乏统一的标准定义, 供应链生态系统也仍在变化中,设计、分析、验证及测试方面的挑战仍有待解决。本文将简要概述三 维集成电路(3D-IC)技术,随后探讨其设计挑战、生态系统需求以及所需的解决方案。尽管各类多芯 片封装(multi-die packages)已问世多年,但本文的重点仍放在多芯片堆叠的三维集成与封装技术上。

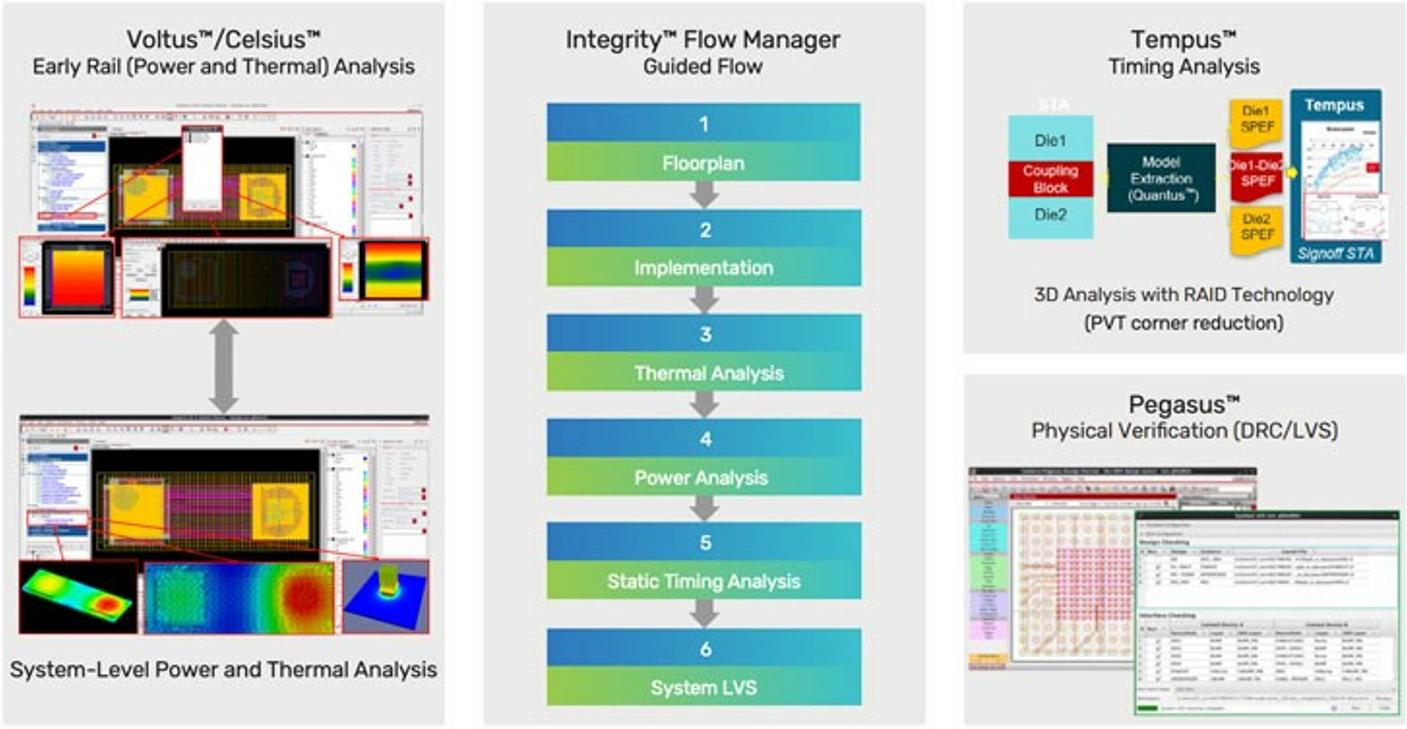

从设计角度来看,实现真正的三维集成(3D integration)可能需要对工具进行一定的重新调整。在 架构分析、热分析、跨芯片布局、时序分析、测试以及验证等方面,都需要更强的功能支持。

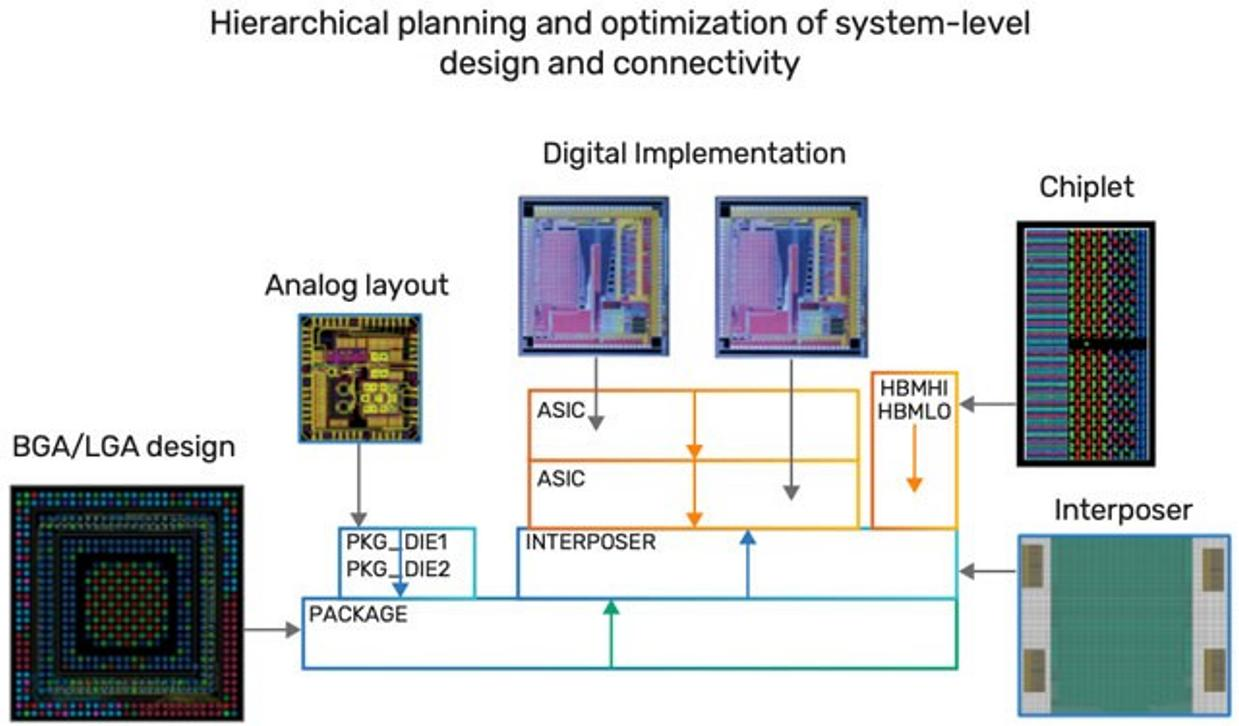

此外,还需要新的系统级功能,例如顶层规划与优化、芯粒间信号完整性(SI)以及集成电路 (IC)与封装协同设计。其中部分功能目前已可获取,并能通过系统设计工具加以利用。

最终,设计人员需要一个能够将所有必需功能整合到单一设计平台中的解决方案。一个成功的三维 集成电路(3D-IC)设计环境需预先捕捉顶层设计意图,支持通过早期功耗 / 热分析估算实现抽象化设 计,并通过实现、提取、时序收敛、测试、分析及封装等环节达成设计收敛。

如今,系统级芯片(SoC)在单一硅芯片上集成了数量惊人的功能。系统级芯片通常包含处理器、 数字逻辑电路、存储器和模拟元件,同时还集成了嵌入式软件。许多系统级芯片拥有数亿个逻辑门,且 运算速度正朝着千兆赫兹(GHz)级别迈进。

如今,系统级芯片(SoC)设计面临的最大问题或许是不断攀升的开发成本。据行业估算,在 5 纳 米(5nm)工艺节点下,系统级芯片的硬件与软件开发成本可能会突破 5 亿美元。

此外,漫长的开发周期会导致额外成本增加。若成本无法降低,采用先进工艺节点的系统级芯片 (SoC)可能仅适用于少数大批量生产的应用场景。

此外,传统的单芯片系统级芯片(SoC)还存在一些固有劣势。其一,所有元件都被集成在同 一工艺节点的单颗芯片上,但先进工艺节点下的模拟电路与射频(RF)电路设计难度极大。若设 计团队尝试在先进工艺节点上实现模拟电路,不仅需要投入大量时间开发和测试所需的知识产权 (IP)模块,还需应对与工艺相关的问题,例如工艺偏差(variability)和漏电(leakage)。

单芯片系统级芯片(SoC)面临的另一项挑战是混合信号集成与验证。将模拟电路与数字电路近距 离放置会引发诸多问题。当然,也可将对干扰敏感的模拟元件或噪声较大的数字元件置于独立的集成电 路(IC)中,但这就需要在不同封装之间传输信号 —— 这种方式不仅会增加功耗,还会降低性能。

最后,最先进的系统级芯片(SoC)设计正逐渐触及制造层面的物理尺寸限制(即掩模版尺寸限 制)。当然,这类接近掩模版尺寸上限的芯片,其良率通常不会很高。

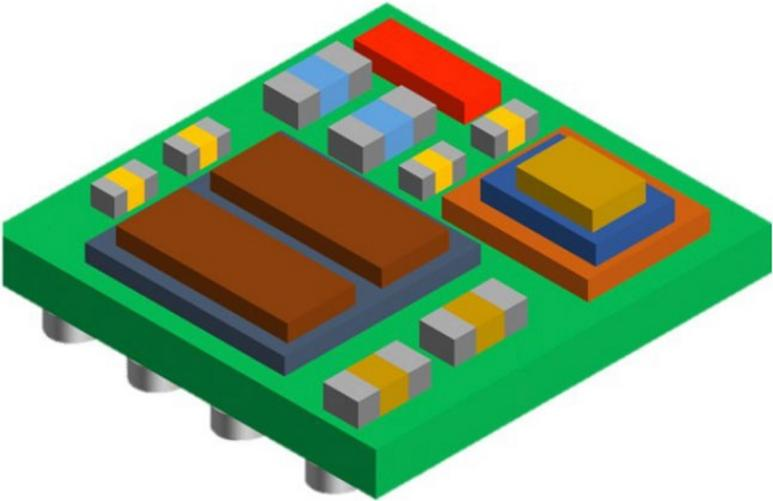

图1:典型的系统级封装(SiP)

图2:典型的堆叠封装(PoP)结构

长期以来,单芯片系统级芯片(SoC)方案之外的另一种选择,是将多颗裸芯片集成到单一封装内。 例如,这种方式可实现对模拟 / 射频(RF)电路采用 28 纳米工艺,而对数字逻辑电路采用 10 纳米工艺。系统级封装(SiP,见图 1)与多芯片模块(MCM)这类术语,均指代上述多芯片集成技术 —— 在这些技术中,多颗芯片被装配在同一层压基板上,通过该基板实现芯片间的互连。此类技术早在 20 世纪 80 年代就已开始应用。

与系统级芯片(SoC)方案相比,系统级封装(SiP)方案具有多项优势,其中包括:模拟芯片、 数字芯片和存储芯片等各类芯片,均可针对自身领域特性,采用最适配的技术工艺来实现。除逻辑电路、 存储单元、模拟电路和射频(RF)功能外,现代系统级封装(SiP)还可能集成微机电系统(MEMS) 元件,例如天线或反射镜等。

多年来逐步发展起来的另一种封装方案是堆叠封装(PoP,见图 2)—— 在该方案中,一个 封装可直接安装在另一个封装的顶部,并通过模塑通孔(through molding vias)实现连接。堆叠 封装组件虽可归为三维封装范畴,但该方案在性能、功耗、密度及外形尺寸方面,均无法达到真正 的三维集成电路(3D-IC)水平。

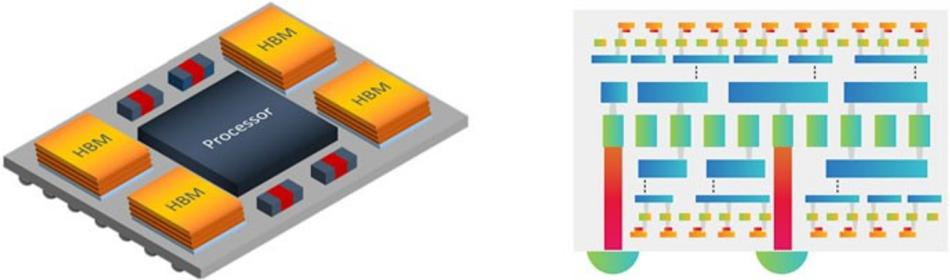

当前最新发展的三维封装技术之一,是带有硅通孔(TSV,Through-Silicon Vias)的硅中介层 —— 这类中介层可实现从顶部金属层到背面金属层的直接连接。硅中介层在芯片与层压封装基板之间构建了 另一层级的封装集成结构,能提供精度更高的芯片间互连。这种特性可提升性能并降低功耗,该技术通 常被称为 2.5D-IC(二维半集成电路)设计,不过部分设计人员也会将其归入 “3D-IC”(三维集成电 路)的范畴。与引线键合式系统级封装(SiP)相比,硅通孔(TSV)具有更低的电阻 – 电感 – 电容 (RLC)寄生参数、更优的性能、更高的功耗节省率,且能实现更密集的集成。而与硅中介层方案相 比,采用混合键合技术的垂直三维芯片堆叠,可实现更高层级的集成、更小的外形尺寸,以及更短的设计周期(见图 3)。本文将重点探讨三维集成技术,尽管为 3D-IC 开发的设计方法学,同样也非常适用于 2.5D-IC 硅中介层的设计。

图 3:典型的硅中介层设计(左)与三维集成电路(3D-IC)或三维集成示例(右)

结论

三维集成电路已成为半导体产业的重要发展趋势。该技术在多类应用场景中展现出显著的功耗、性 能与尺寸规格优势,并有望缓解系统级芯片(SoC)开发成本持续飙升的压力。由于设计人员能够堆叠 不同工艺节点的芯片,如今不再需要将模拟/RF 等所有系统组件强制迁移至单一工艺节点。

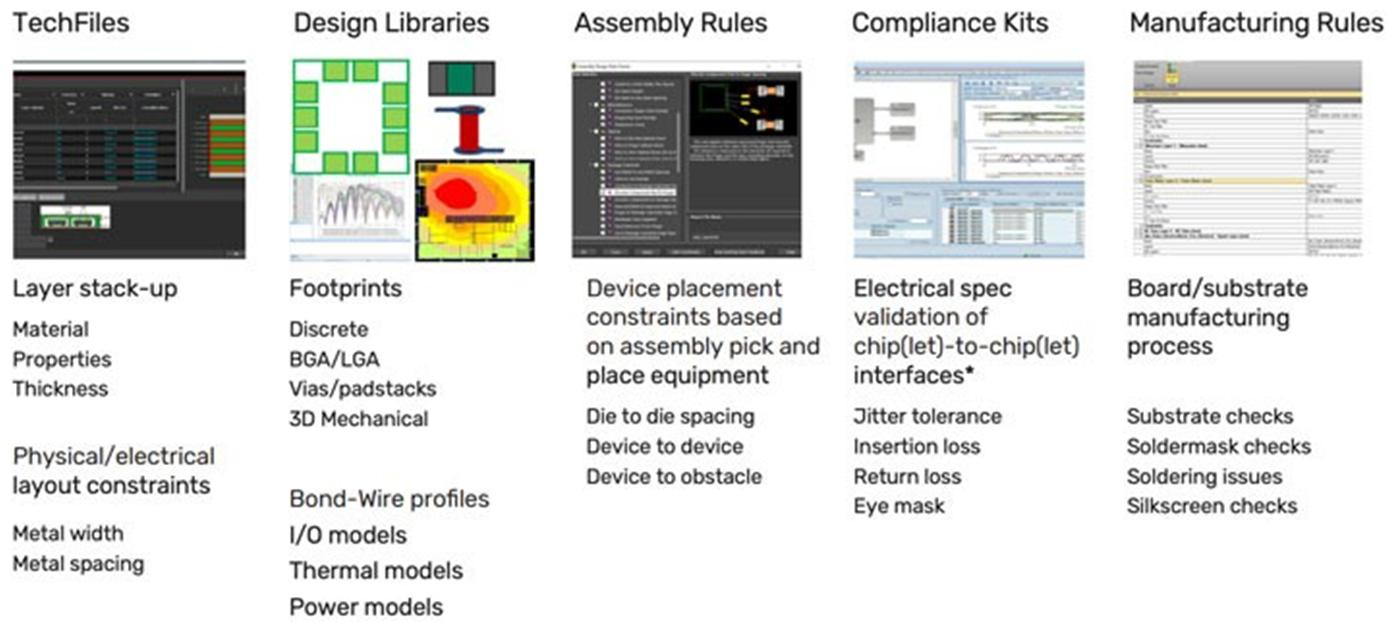

正当设计流程的挑战逐步攻克之际,要将三维集成电路推向主流用户的大规模量产仍任重道远。 当前亟需在系统级架构探索、三维布图规划、设计实现、参数提取/分析、测试及芯片封装协同设计等 领域建立新的技术能力。为实现优化、高效且成本可控的设计,3D-IC 流程需支撑统一的设计意图、 抽象化协同以及物理制造数据的多域收敛。唯有构建涵盖晶圆厂、IP 供应商、EDA 厂商和封测企业的 标准化产业生态,配套完善的设计工具包与参考流程,才能打通三维集成的产业化路径。

实现高性价比的三维集成电路设计需要芯片、封装与电路板三大领域的协同设计。楷登凭借其在模拟与数字实现、封装及 PCB 设计工具领域的全面解决方案,在支持 3D-IC 技术革命方面占据独特优势, 能够为成本优化的三维集成电路设计提供不可或缺的技术能力。