系统级封装(SiP)的实现为系统架构师和设计师带来了新的障碍。传统的EDA解决方案未能将高效的SiP发展所需的设计流程自动化。通过启动和集成设计理念的探索,捕捉,构建,优化,以及验证复杂的多芯片和PCB组件的分立基板,Cadence的SiP设计技术简化了多个高引脚数的芯片与单一基板间的集成。

Cadence SiP技术

高性能消费类电子产品制造商正转向到SiP设计,因为它提供了一些显著优势,如增加功能密度,整合不同的芯片技术,低功耗,改善信号质量/完整性,并且易于集成到PCB系统中。然而,SiP设计还需要广泛的各种领域的专家设计人才,这些领域要在历史上具有有限的主流应用。

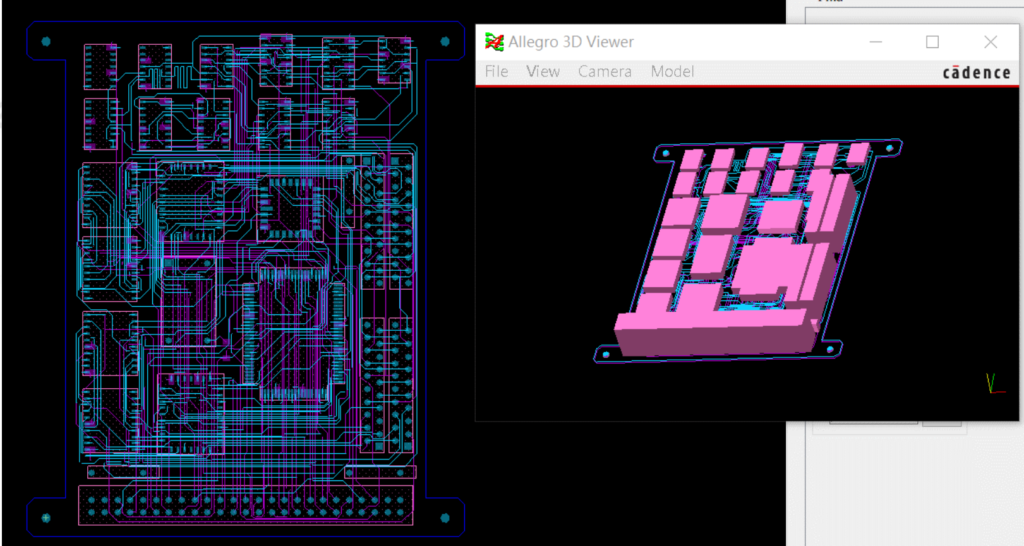

通过互连驱动的方法,将多个高引脚数的芯片与一个单一基板的集成简化(图1),Cadence SiP协同设计技术允许企业采用曾经专业的SiP工程设计能力为主流产品进行开发。Cadence SiP解决方案无缝集成Cadence Innovus技术精细化芯片/封装的互连与Cadence Virtuoso技术无缝集成进行原理图驱动的模拟/混合信号模块设计。

图1:复杂的多芯片SiP设计,包括引线键合及倒装焊芯片,在这个强大的约束规则驱动的环境中可以很方便并快速的创建出来。

互连驱动的SiP

Cadence互连驱动的SiP流程被调整为可以将多个大尺寸高引脚数的芯片整合到一个单一的基板上。这个流程的目标是针对系统级封装级别互连的定义及管理所面对的主要挑战—系统级封装平面布局的物理概念原形化。包括多芯片堆叠,转接板,基板腔体,及芯片凸点矩阵的精细化一优化及最小化基板互连布线及信号完整性的挑战。SiP流程是围绕一个独特的系统互连管理器建立的,这个系统互连管理器也是SiP Digital Architect这个产品的一部分。

Cadence完整的SiP实现技术包括芯片padring/凸点矩阵精细化,详细的封装级信号完整性分析及提取与三维建模,是通过使用以下四个关键产品技术来实现的:

- Cadence SiP Layout:详细的约束规则驱动的基板物理实现及加工制造的准备。包括die abstract的精细化,以实现芯片的凸点矩阵与BGA球图的协同优化。对芯片凸点矩阵的改变可以通过一个分立的ECO流程与Innovus及Virtuoso进行交互

- Cadence SiP Digital Architect:前端逻辑互连的设计定义,跨多基板以构成系统级封装

- Cadence Virtuoso SiP Architect:提供一个模拟/混合信号原理图及电路仿真驱动的SiP模块设计流程

- Cadence Allegro Sigrity Package Assessment and Extraction Option:详细的互连抽取,三维封装建模,及电源感知的信号完整性分析

SiP Layout

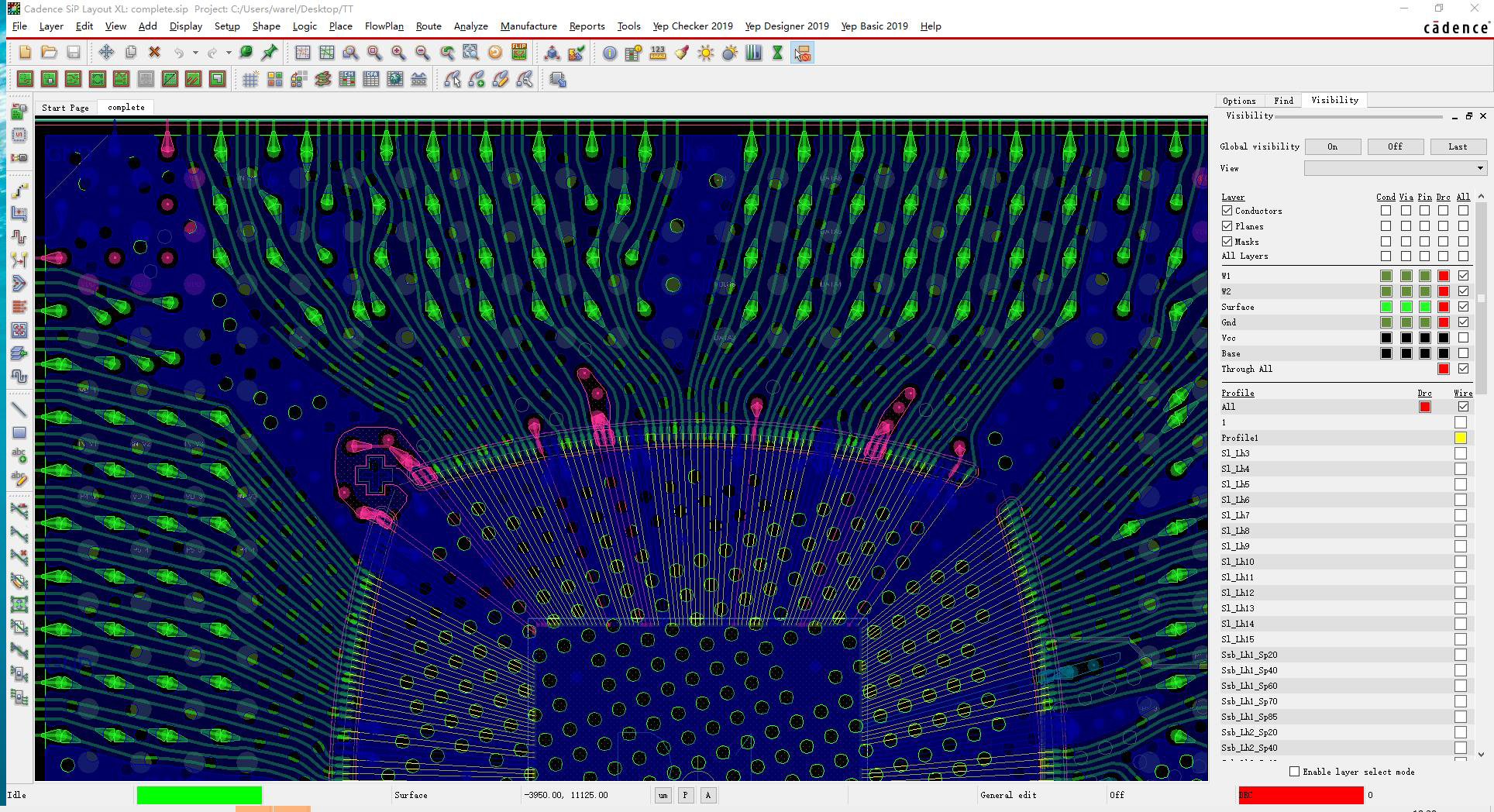

Cadence SiP Layout为系统级封装设计提供了一个约束规则驱动的布线环境。包括基板的布局布线,芯片、基板、与系统级的最终互连的优化,生产制造数据的准备,完整的设计验证及流片。环境集成了芯片/封装的I/O Padring/凸点矩阵精细化及三维芯片堆叠创建与编辑功能。此外,完整的在线设计规则检查(DRC)支持复杂的和独特的层压,陶瓷及沉积基板技术的所有组合要求。多层倒装焊芯片与径向的任意角度布线实现了快速的规则驱动的互连的创建。

芯片padring/凸点矩阵精细化

SiP Layout允许封装设计师通过Die Abstract,基于芯片封装的BGA球图及相关联的扇出与布线,来精细化/优化芯片的凸点矩阵。Die Abstract是一个开放的的ASCII XML格式的文件,包含芯片的I/O padring,RDL,及凸点矩阵。Die Abstract可以被芯片设计工具创建(Innovus和Virtuoso解决方案)或者从Cadence Orbit 10 interconnect Designer创建(图2) 。在封装设计过程中对Die Abstract作的精细化可以被作为更新的Die Abstract传回给IC设计者,并可以被Innovus与Virtuoso直接读取。