Cadence®OrbitIO™通过交叉协同设计优化环境为互连设计工程师提供设计早期中对集成电路中的IC、封装和PCB设计进行快速评估、设计实现和优化,并提供对信号路径上的Bump/BGA Ball的合理化分配、优化的互连特性和最佳布线路径方案评估。完整的系统可视化和统一的数据模型可以快速提取和传递设计中对相邻之间基板特性的任何变更,提供整个系统之间相互影响的实时反馈效果。使用OrbitIO的互连设计师可帮助工程师或架构师实现跨基板设计时的快速合理化互连解决方案,以在实现最佳性能、成本和可制造性要求,减少设计迭代次数并缩短研发周期。

OrbitIO互连设计工具帮助设计团队优化通过器件和系统的性能,它提供了统一的系统设计架构环境,用来评估和优化关键高速接口传输,例如DDR3、DDR4、PCIExpress®(PCIe®)Gen 3、USB3.0以及其他多种跨基板的系统互连设计。OrbitIO互连设计工具可供系统架构设计师、项目负责人或封装设计师用于快速评估芯片到封装,封装到PCB的接口互连,提供Bump/BGA Ball的最佳化IO组合和信号合理化分配。它使无晶圆厂的半导体设计公司和系统化设计之间可以快速合理的评估IO封装路径及布线。

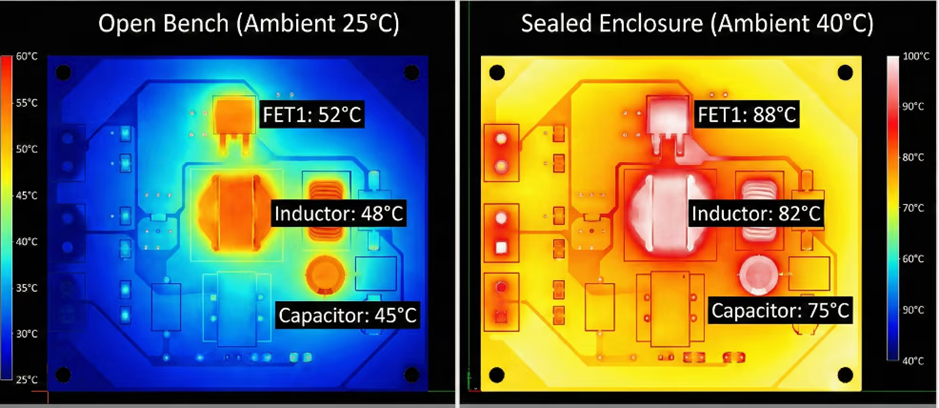

图1 快速芯片/封装路径方案开发和评估

特点:

- 提供早期预测并避免产生因上下游交叉跨基板的互连设计问题

- 大大缩短优化芯片和封装之间的接口设计所需的时间

- 优化关键PCB器件到封装Ball球焊盘的定义

- 更好地预测成本和设计性能

- 快速生成抽象化设计方案以便快速灵活的响应市场需求

- 提供清晰的传达设计意图并规划外部设计资源

- 协调引脚交叉分配,满足对高速接口多种基材选择合理性

- 与OSAT提供者之间的设计工具全兼容

功能:

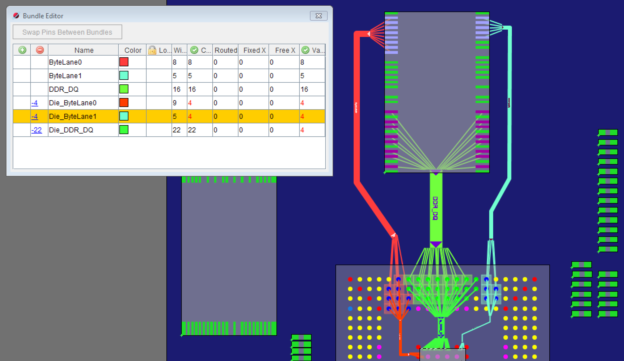

1.跨基板交叉设计与优化

OrbitIO互连设计工具提供统一的设计环境满足对设计路径的实现与优化,提供跨基板互通性操作的解决方案。通过Cadence Innovus™或Virtuoso®技术平台提供的硅芯片模型,采用统一的XML格式数据,提供单一文件交换格式与I/O规划来达到保护关键敏感性的芯片IP。

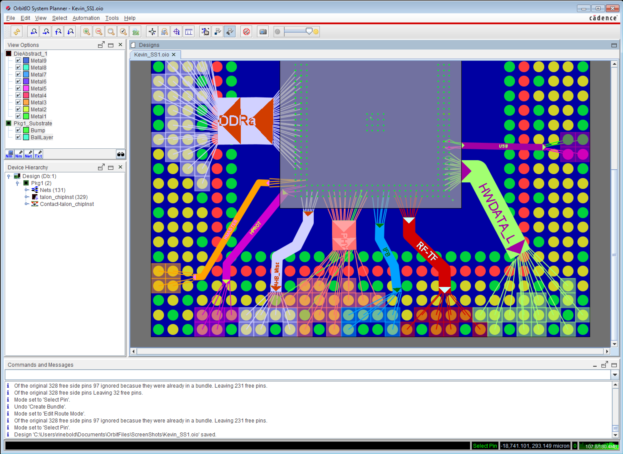

图2 PCB驱动封装和Die分配

封装定义和互连设计由OrbitIO互连设计师直接导入Cadence SIP布局有助于加快系统级封装的设计过程。 这种设计方法是对于与其合作的公司而言具有巨大的价值,可以去除外部设计资源沟通误区,提供设计中的快速评估设计意图和优化设计路径的合理化解决方案。

PCB相关的互连设计级优化可以与Cadence Allegro®PCB、第三方工具实现交互设计,支持行业标准格式例如LEF / DEF、Verilog、TXT / CSV格式。

2.系统化设计

跨基板设计优化的第一步在于建立芯片、封装和PCB的物理连接,OrbitIO 互连设计工具提供自动的层次化系统设计,可以管理多个设计进行数据相互关联,包括设计的基板、设计约束和堆叠等。OrbitIO 互连设计工具的通用应用在于实现PCB上的关键器件和连接器来驱动封装的BGA Ball 球或者Flip-chip bump的引脚分配,实现从上到下的系统兼容性互连设计。指导这些器件可以完成布线的Fan-out扇出,实现更高级别的系统级布线优化。

3.预测发展规划

常规设计方法有是自上而下的串行方法,往往硅芯片下游向上反馈的信息较少,随着芯片和封装功能不断集成和发展,结合最新一代Multi-Gigabit并行总线接口如DDR3或DDR4,需要非常谨慎的处理系统互连架构和基板的设计实现。 如此复杂的设计在效率极低的方法指导下是很容易产生错误的。

OrbitIO互连设计工具环境可以实现快速探索和评估芯片互连设计架构,提供即时反馈相邻基板设计之间的影响。可用于早期可行性方案评估,利用最佳设计数据或即时创建设备。采用适用满足双向互通的从硅芯片自上到下或从封装/PCB的自下而上的设计方法学和实际协同设计环境,用来驱动芯片设计和封装PCB的物理和逻辑互连。