Cadence Allegro PCB Librarian包含一个高级库开发环境,面向板级设计组件。一个全面的库编辑工具组让元件设计快速而简单,将多引脚数元件有关的开发时间从几天缩短到几分钟。Allegro PCB Librarian让元件创建任务自动进行,消除了手动确认的必要,并且为原理图符号保存修改历史。

主要优势:

- 在高级元件创建与验证功能的帮助下加速元件创建

- 提供整合的在线验证与流程验证功能,使用互动与批量工具,为设计工具提供可靠的库数据。

- 能够从表格、栅格、文本文件和多种其他常用格式轻松导入元件信息。

>新元件的完善

>逐步增添变更元件以加速更新 - 提供强大的图形编辑功能用于创建原理图符号和可重用的形状。

- 为多种设计环境提供一个通用的库开发环境。

- 集成Allegro Design Entry HDL

图1:综合电子表格与图形编辑器

功能特点:

元件创建

引脚数目大的元件正在成为现货供应型元件的标准。为原理图和PCB布局创造这些大引脚数元件,如果不使用特殊工具加快速度,那么可能要花费几个小时甚至几天时间。

Allegro PCB Librarian 强大的导入与电子表格编辑功能,为操作大引脚数元件数据提供了辅助。用户可以根据多种符号迅速分离引脚,将引脚名与引脚数一一对应,并指定电源与接地引脚的可见性。

强大的图形编辑器让符号创建简单易上手。用户不仅可以创建复杂的IEC与IEEE形状代表引脚与功能,还可以将它们保存为可重用的库元素。

Allegro PCB封装向导为多数常用元件提供模板,使得封装创建十分简单。使用封装向导,用户可以在几分钟的时间内精确创建有数千个引脚的复杂封装。

Allegro PCB Librarian 还为Verilog和VHDL模型提供了将HDL模型与原理图元件迅速关联的能力,用于系统级数字仿真。

在Allegro PCB Librarian中,元件的所有变化都会被跟踪,元件版本之间的区别会被自动发现并保存。这消除了库管理员需要记录元件所有变化的负担。校验和验证被集成到系统中,会追踪在库系统外对元件所作的任何修改。这会保护数据免受未经许可的修改,并在被修改的元件在系统中打开时通知库管理员。

多中设计环境支持

Allegro PCB Librarian 允许用户为Allegro Design Entry HDL、Cadence Design Entry CIS、Mentor Graphics Viewdraw/DxDesigner和Mentor Graphics Design Architect创建符号。元件信息也可以被导出为用逗号隔开的值(CSV)和XML格式。

数据导入

Allegro PCB Librarian提供了多种导入选项和工具加速元件创建。用户可以通过导入多种数据格式的元件库。裸片数据文件导入可用于协同设计,同时FPGA导入帮助在前端设计中执行FPGA流程。通过IBIS和DML模型导入,前端模型可以从第三方高速模型中被轻松创建。Allegro PCB Librarian会检查被导入的数据的一致性和有效性,在前端标出错误。预览窗口让用户可以在元件被创建之前评估元件数据。

数据表采集

能够读取引脚表格与引脚栅格的功能使得从PDF数据表的描述中创建元件非常容易。用户可以从数据表中将pin-out/ball-map图标复制到Allegro PCB Librarian。该数据为自动集成,并且可以进行微调以符合公司的命名标准。

此外,用户可以从数据表复制信息的完整表格,并可以配置引脚类型与总线标记的转换。

原理图符号编辑

Allegro PCB Librarian带有一个强大的图形编辑器,用于创建可重用的形状与原理图符号。一个带有符号信息的可编辑的电子表格,以及一个带有导出功能的符号编辑。一个图形化的比较界面可以方便地用来比较多个实体之间的接口将界面与多种零件封装信息对比,包括封装、原理图符号和SI模型。ECO导入模式让执行递增式变更极为容易,ECO模式可以大大减少重复工作。

PCB封装编辑

PCB封装创建流程是为简化当今封装模型不断提高的复杂性而设计的。强大的向导让用户能够使用模板迅速创建封装,它可以处理大多数封装类型,包括DIP、SOIC、PLCC/QFP、PGA/BGA离散通孔、SMD离散、SIP和ZIP。

有效确认

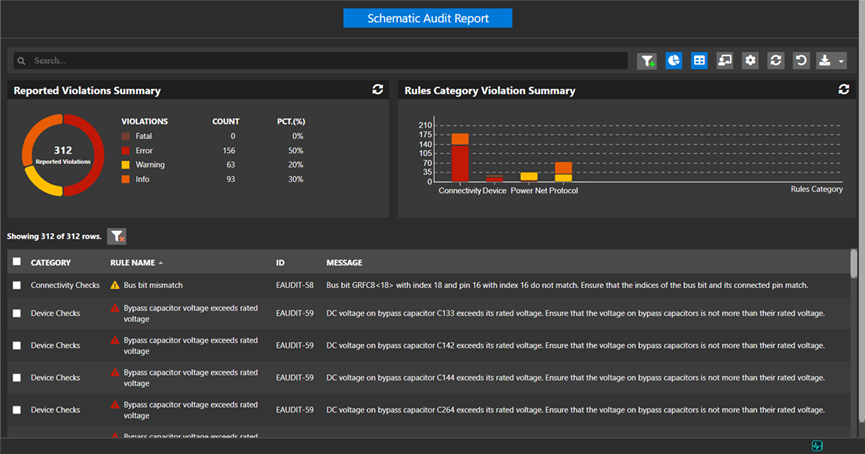

Allegro PCB Librarian提供了全面的元件确认功能,在元件创建的每一个阶段进行内部检查。对于导入的数据,会在导入时进行确认。当数据输入元件编辑器后,它就会实时检查有效字符、长度、允许赋值和语法。符号封装检查确保元件能够在完整的PCB设计流程中运作。封装确认程序让用户能够将原理图符号开发时指定的引脚号与PCB封装对比。这种在线检查可以确保原理图组件与封装的同步。此外,批量确认提供了自动的设计流程确认,能够大大降低库管理员的负担。

Allegro PCB Librarian 提供了一个标准规则集以及一个开发工具包,用于创建用户定义的规则。使用这些规则与内置的元件确认系统,库管理员可以推进元件的高级规则检查。这可以减少代价高昂的设计迭代,确保元件一开始就正确无误。