市场需要产品提供更多功能,在此推动下,厂商纷纷选择先进封装来适应复杂的设计。为了有效地设计这些复杂的封装,需要一个成熟的实现工具来处理电气和物理方面的约束。Cadence® IC封装设计技术能够高效、灵活且可靠地实现密集的先进封装设计,深受全球众多客户的信赖。集成的信号和电源完整性分析确保了在整个设计周期内可以一并解决电气和物理挑战。使用Cadence集成电路封装设计技术,设计师可以满足日益紧张的工期要求,确保设计一次成功。

Cadence IC封装设计技术

集成电路(IC)封装是“硅片-封装-电路板”设计流程中的一个关键环节。Cadence Allegro®平台为PCB和复杂封装的设计和实现提供了完整、可扩展的技术。借助Cadence的IC封装设计技术,设计师能够优化复杂的单裸片和多裸片引线键合以及倒装芯片设计,降低成本并提高性能,同时满足较短的项目工期要求。

这种约束驱动的行业标准技术实现了从单芯片到复杂系这种约束驱动的行业标准技术实现了从单芯片到复杂系统的系统规划、基于先进封测厂(OSAT)和晶圆代工厂( Foundry)的封装设计。

Cadence IC封装设计技术可用于实现高效的引线键合设计技术、约束感知基板互连设计以及详细的互连提取、建模和信号完整性/供电分析。

Cadence IC封装布局技术有几种不同的产品和许可等级包括:

Allegro Package Designer Plus(有许可)

SIP Layout Option(有许可)

OrbitIO™ Interconnect Designer(有许可)

Silicon Layout Option(有许可)

RF Layout Option(有许可)

Symphony™ Team Design Option(有许可)

System Connectivity Manager (有许可)

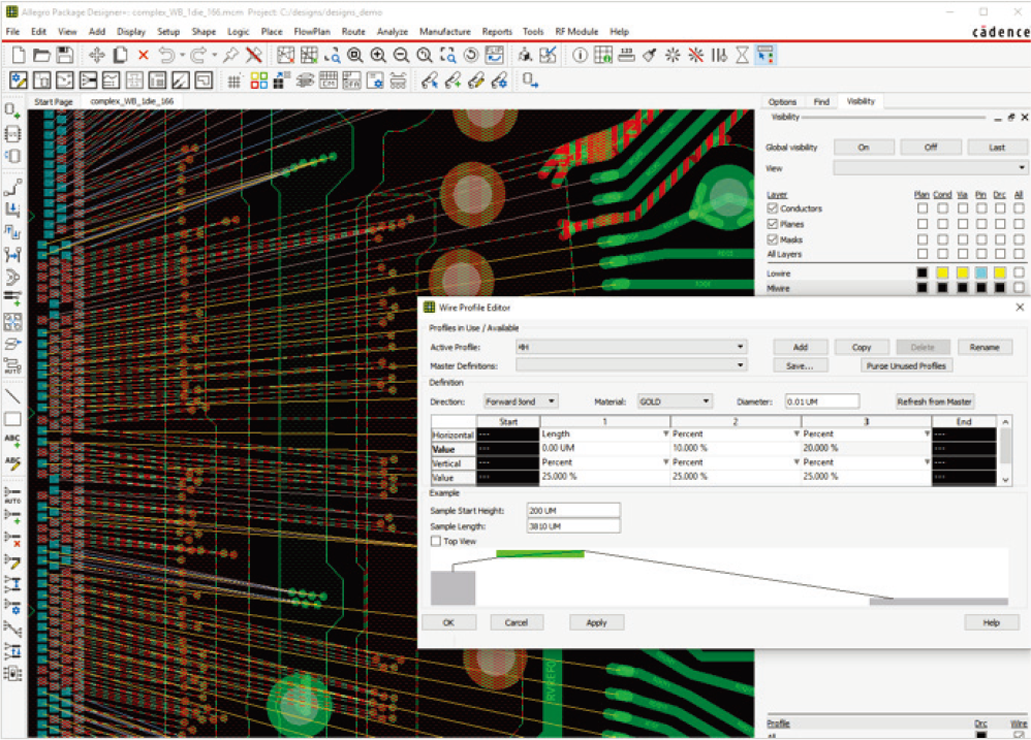

图 1:约束驱动的交互式引线键合包括跨多个引线层的推挤式设计。

3D 引线轮廓查看器/编辑器能够创建和支持多个引线轮廓。

参考轮廓库有助于实现可制造的设计和精确仿真。

核心优势

- 技术文件使用模型简化了设计设置过程,可自动执行

- 从前到后的原理图和无原理图流程提供了业界最灵活的连接管理模型

- 即时生成库,简化数据输入

- 智能定义引线键合、倒装芯片、堆叠和嵌入式裸片配置,确保自动建构校正布局

- 先进的键合体(bond-shell)生成功能,甚至可以自动生成最复杂的多晶粒、堆叠引线键合布局

- 径向、全角度推挤式布线解决了 BGA/LGA 基板设计的独特布线挑战

- BGA/LGA无误特定的 DRC/DFM/DFA检查,设计一次即保证准确

- 3D可视化和DRC 检查,比2D解决方案更准确地验证设计

- 与Cadence Innovus™和Virtuoso® IC设计工具的集成流程,可简化 IC 和封装的协同设计

- 与 Cadence Sigrity™、Clarity™ 和 Celsius™ 求解器紧密集成,从而快速准确地进行封装电气和热仿真验证

- 提供板布局,减少整体设计时间Symphony Team Design 选件,用于多用户同时编辑基板布局,减少整体设计时间

- Silicon Layout Option 扩展了Allegro Package Designer Plus的功能,用于实现硅基板的布局设计和掩膜级验证

- 全球拥有超过400家客户

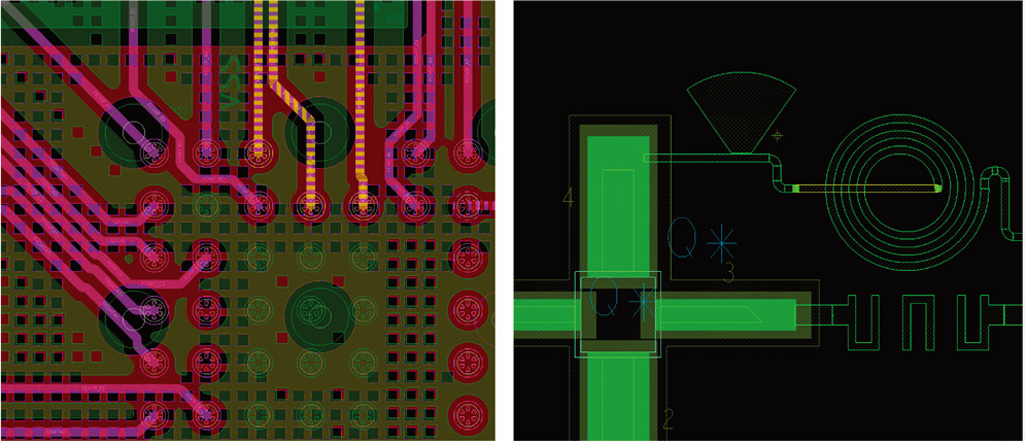

图 2:通过产品选件(SIP230 Silicon Layout 和 SIP231 RF Layout),

可以获得更多的硅基技术和射频封装功能。

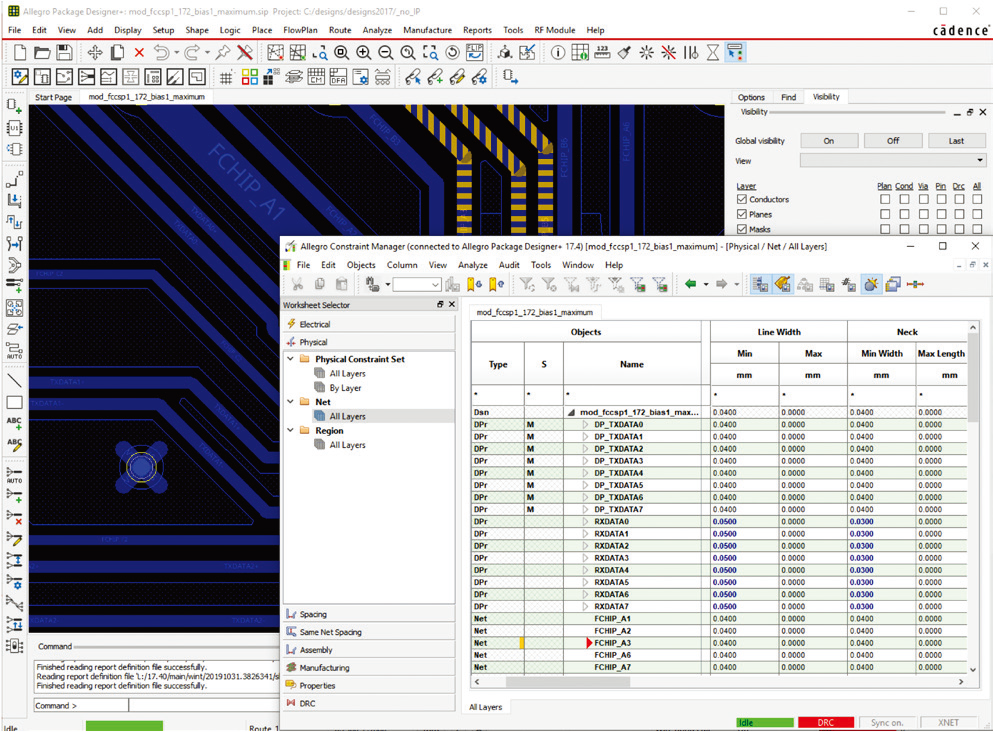

图 3:全面的基板物理虚拟原型设计功能,使工程师能够评估物理

设计变化对信号完整性和信号性能的影响。

布局功能

约束驱动的物理布局

Allegro Package Designer Plus提供当今先进封装设计所需的全部功能。完整的在线设计规则检查(DRC) 支持层压板、陶瓷和硅基板技术的复杂、独特要求。还支持多腔体、复杂形状以及交互式和自动引线键合。

流程管理器(Flow Manager)易于使用,可引导用户完成每项任务,并自动创建IC封装构件,包括导入和创建裸片、封装、布线、电镀条和回蚀刻。支持单个和多个裸片、裸片堆叠和双面裸片;使用裸片和基板向导,用户可以自由选择ASCII标准格式(Die Text、DEF、AIF)、裸片摘要或表格驱动的用户界面(如”text in”向导),并自动定义这些库元素。

复杂的基板建模和规则检查

可以根据一套完整的物理和电气设计规则(约束)验证设计的准确性。物理约束是在用户定义的技术文件中制定的物理设计准则,用于确保设计的可制造性。电气约束是信号延迟、时序和关键网络的失真规范。DesignTrue可制造性设计检查旨在确保设计符合制造商的要求。在整个设计过程中,用户可以根据这些约束条件对设计进行动态检查,确保设计符合制造和电气规范。用户可以通过设计规则检查标记以及在基于电子表格的约束管理器中标记违规行为得到即时反馈。

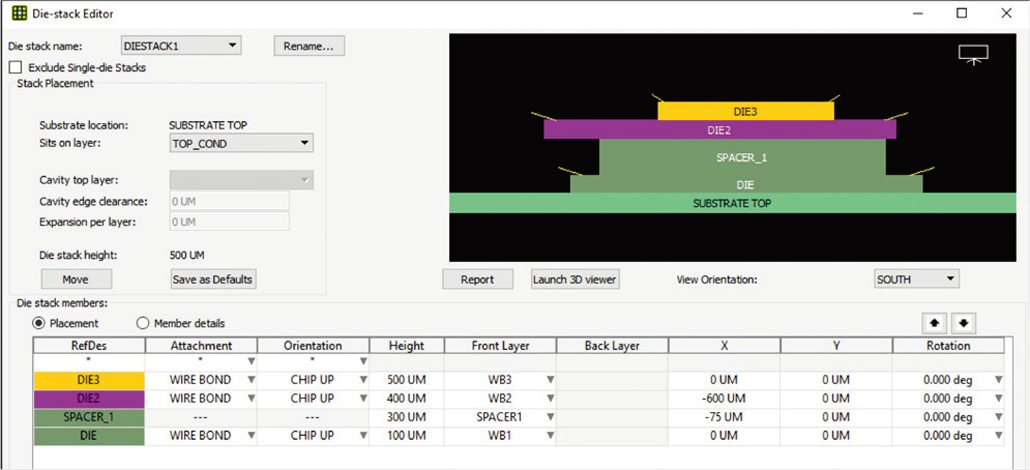

图 4:Die Stack Editor包括间隔层和中介层。

裸片的两边均可连接。可用于管理复杂的堆栈-裸片结构。