基于Option模块化的选项配置,Allegro Design Authoring提供了一种可扩展的解决方案来适应不断变化的需求。Allegro Design Authoring(Base)提供了一个强大、简单易用的原理图创建环境,允许创建平面的或者层次的原理图。其企业级的原理图编辑器无缝地集成Allegro PSpice Simulator,Allegro Sigrity 仿真以及Allegro PCB Designer,针对即将开展的数字、模拟、射频和混合信号设计开启基于约束驱动的PCB设计流程。

多种风格选项允许为您的设计提供快速连通性,而不需要创建连接符号或者符号连接引脚或者端口。嵌入式电子表格的设计方式类似于界面,可以更容易的进行设计输入,这比传统的设计元件引脚较多的符号或背板设计方法提高至少5x到20x的速度。High-Speed选项通过集成高速约束的层次的连通性,电子约束复用,允许创建正确的设计意图。从概念到制造,这使得一个约束-驱动的PCB实施流程到确保一个更短的、可预计的和完成PCB设计周期。其它配置包含一个Team Design选项,一个FPGA System Planner选项,一个FPGA ASIC Prototyping选项和一个Design Publisher选项。

技术优势

- 缩短创建设计意图的时间

- 可同步进行原理图和Layout设计

- 通过验证,约束-驱动流程来减少设计课程

- 减少驱动数字、模拟和预Layout信号完整性仿真器的单个原理图的返工

- 通过可扩展的基础软件加option的配置来减少整体成本

Schematic Editing

Allegro Design Authoring通过协同设计的方法来使工作流程效率最大化,设计可以分割成一页或者一个模块,每个设计师可以指定一页或多页或者模块,任意数量的设计师可以同时工作在相同设计的不同部分,并且互不干扰。各设计阶段可以在Allegro PCB Editor中继续Layout之前合并设计,这种并行设计的方法使得Allegro Design Authoring成为极其富有成效的大型设计。设计师可以并行的进行PCB Layout和原理图设计。在Allegro Design Authoring和Allegro PCB Editor中改变模式可以周期性地合并和同步。

Allegro Design Authoring中的原理图编辑器允许创建平面的或者层次设计而不需要进入“Hierarchical”或“Occurrence”模式,它提供了一个Cross-referencer来注释原理图允许平面原理图上简单的信号追踪。原理图编辑器还允许快速放置多个分立器件,例如,放置512个电阻到一个512位的bus,只需要在这个bus上放置一个电阻,然后,设定512个这样的器件需要被放置,这样原理图编辑器可以自动以512位总线上连到这个这个电阻,这大大减少需要放置和显示在设计中的图形器件的数量。

Allegro Design Authoring点到点的连线方式可以很容易的连接端口到2个不同的器件,节约时间来创建原理图。同样,自动插入一个2引脚器件在一个现有的网络自动生成相关的输入和输出引脚来遵循相关的网络名称,缩短创建基本原理图的时间。

无论你是使用几百个页面的平坦式设计或是多个层次化设计,全局导航允许设计师点击几下鼠标即可指向设计的任何网络或器件,全局查找和替换窗口允许查找和代替器件或者属性,这些可以直接在Allegro PCB Editor或者Allegro PCB SI中高亮。

无论你是使用几百个页面的平坦式设计或是多个层次化设计,全局导航允许设计师点击几下鼠标即可指向设计的任何网络或器件,全局查找和替换窗口允许查找和代替器件或者属性,这些可以直接在Allegro PCB Editor或者Allegro PCB SI中高亮。

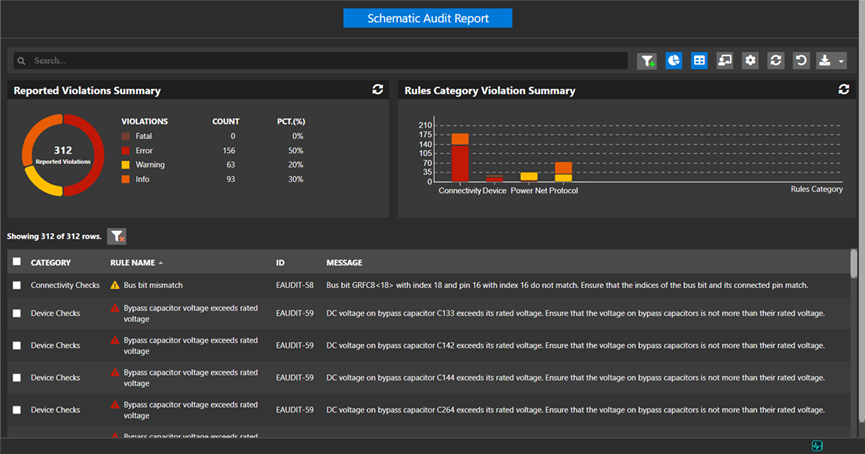

Customizable Rules Checking

Allegro Design Authoring具有消除多个设计迭代的规则检查器,它是一个真正全面的验证工具。它允许执行电气和设计规则检查来验证草图和准确图形的属性名、语法和值。规则检查器还包括支持后期的加工,扇入扇出错误,加载错误,功耗需求和成本要求。规则检查器检查逻辑和物理设计之间的校准。此外,还允许您定义自定义规则,以确保符合公司或者项目指定的设计要求。规则检查器可以用于原理图、器件和物理网表,它有一个规则定义的开发和调试环境,可以以批处理的方式运行,促进企业版软件环境的部署。

Design Reuse with Module Design

大多数的设计起源于其它设计或者复用现有设计的关键部分。Allegro Design Authoring为复用提供了多样的选择,所以您可以选择更有效的方法来设计。旧的设计,模块或者整个设计的页码都可以重用,这样可以减少返工和错误。调用Import Sheet对话框” 可以从一个设计复制单页或者多页到另一个设计,或者只复制粘贴设计之间的特殊的电路图,可以复用电气约束作为模块的一部分,或通过使用电气约束集(ECSets)。进一步的技术允许创建“复用”模块并放置在库文件中,像一个器件一样可用于其它设计中。每个模块的连通性、约束和Layout也都可以复用。同一个模块可以多次使用到相同的设计中而不需要重命名和复制。