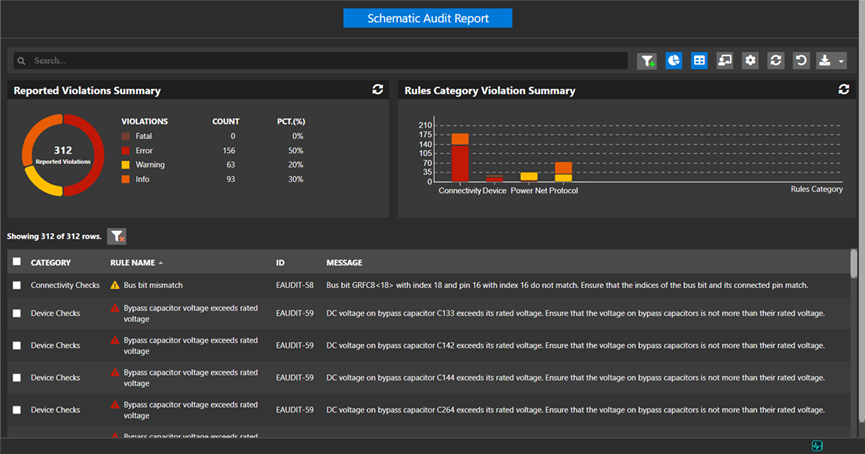

- 通过尽早发现布线前、后的潜在问题,降低设计成本,缩短设计时间

- 通过验证AC、DC 和电源纹波分析来确保可靠的电源分配

- 在整个PCB电路板/封装接口上优化 PDN

- 使用基于模块的原理图编辑器,轻松解决系统级功耗分析问题

帮助您快速验证电源分配网络 (PDN) 的充足性、有效性和稳定性,Cadence® Sigrity™ Advanced PI 可使电源完整性 (PI) 专家跨越多个电路板和封装,从每个接收器的每个电源进行 PDN 仿真验证。

Cadence Allegro® PowerTree™ 技术可使您在物理设计开始之前进行分析,并验证在逻辑设计阶段中定义的物料清单。随着物理实现的进展,您可以复用 PowerTree 设置,从而让各个设计阶段中的 DC 和 AC 电源完整性分析成为一键式流程。

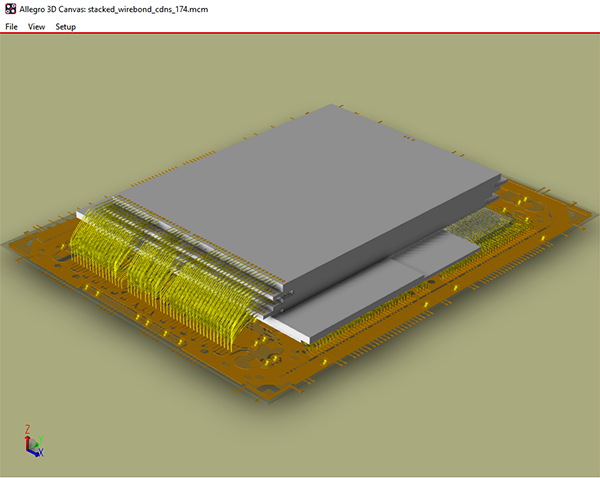

图 1:精确仿真各种有问题的实际结构,例如开孔开槽、过孔区域、焊接金线和颈缩

兼顾热影响的 DC 分析

Sigrity PowerDC™ 技术为 IC 封装和 PCB 设计过程的签核环节提供有效的 DC 分析,包括电/热协同仿真,以最大程度地提高准确性。Sigrity PowerDC 技术可快速精确地定位 IR 压降过大的情况,以及电流密度过大的区域和温度过高的热点区域,最大程度地降低设计失效的风险。

AC分析

Sigrity OptimizePI™ 技术可对PCB电路板和 IC 封装进行完整的AC分析。该技术支持在布线前、后进行研究,快速定位最佳的去耦电容选择和摆放位置,从而尽可能地以最低成本来满足您的 PDN 需求。根据目标阻抗约束条件检查 PDN 阻抗曲线,确保设计符合 PDN 规范。

电源纹波分析

Sigrity SPEED2000™ 技术中的电源地噪声耦合仿真分析流程可用于对 I/O 电源进行直接的时域电源/地噪声仿真。Sigrity Advanced PI 提供了一种针对 PCB 或 IC 封装的直接时域电源完整性仿真方法,而无需提取 S 参数模型后再使用在 SPICE 仿真中。该方法提供了稳定的仿真结果,而且比其他方式更为节省时间。

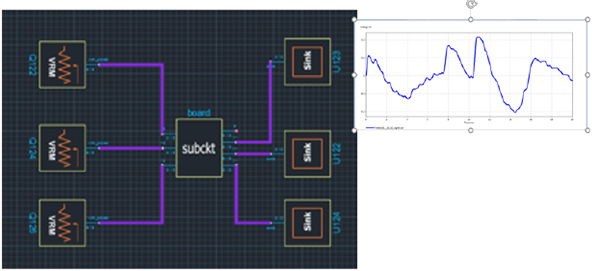

Sigrity Topology Explorer

通用的拓扑探索功能,可用于探索多个系统设计中的电源拓扑。您可以通过连接多个芯片、封装和电路板的电源端口,来创建并仿真完整的“电源——接收器”连接。通过电压调节器模块 (VRM) 模型,可以使用 Sigrity PowerSI™ 或 Cadence Clarity™ 3D Solver 为每种结构创建的 PDN 模型来添加激励。从电源到接收端的每个关键点处, PDN电压可以通过直观的时域视图呈现出来。您可以确定 PDN 的任何部分是否存在导致系统规范范围内的供电不足问题。

图 2:Sigrity Topology Explorer 界面直观,您可以轻松跨

多个电路板以及芯片和封装连接 PDN 互连模型,并查看对电源稳定性的影响

主要功能

- 使用在原理图设计阶段提取的 PowerTree 数据(电源/接收器定义)自动设置 DC 仿真

- 识别难以发现的高电阻布线颈缩区域,并在数千个过孔中找到对应热应力下失效的过孔

- 确定能否在不增加 DC 或热可靠性风险的前提下减少平面层

- 降低新设计和后期产品的 PDN 成本

- PDN 性能可视化直观、可交互