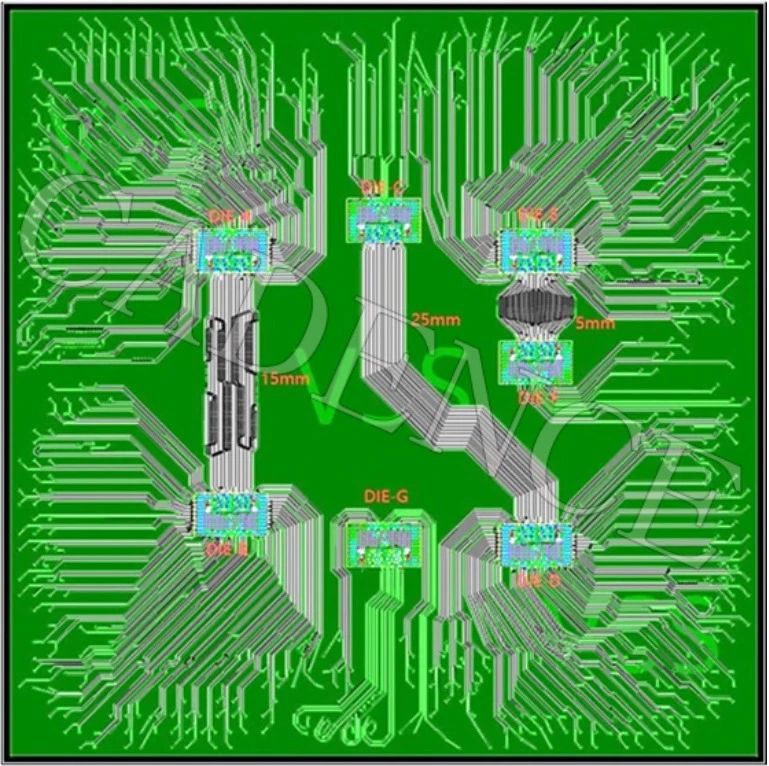

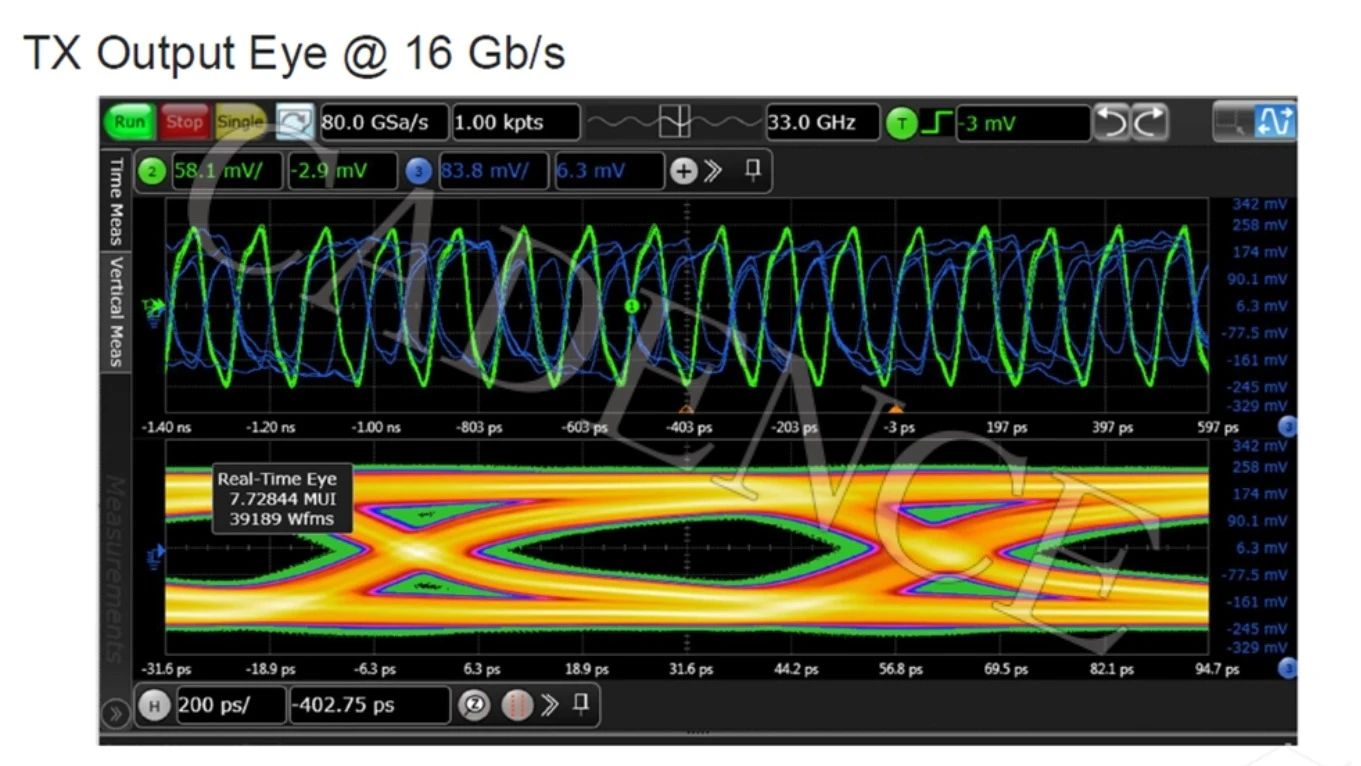

首次流片即成功的芯片具有不同距离的芯片间连接功能,使 Cadence 的设计人员能够收集有价值的信息,并向这些解决方案的最终用户展示我们的 IP 质量。该设计证明了我们对广泛测试和分析的承诺,而所有三个通道链路的开放数据眼图证明了 Cadence 拥有设计满足并超越规范的高性能 IP 的能力。

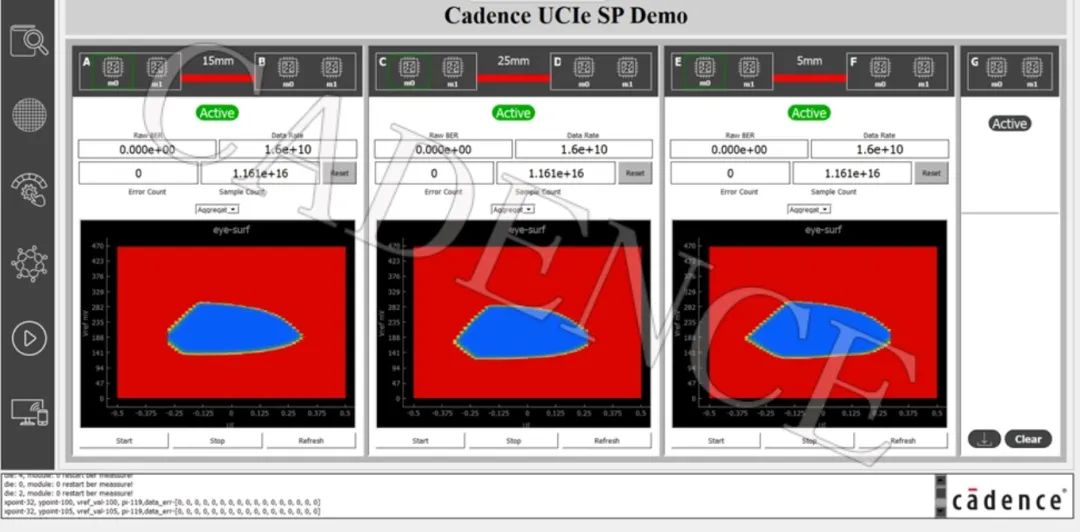

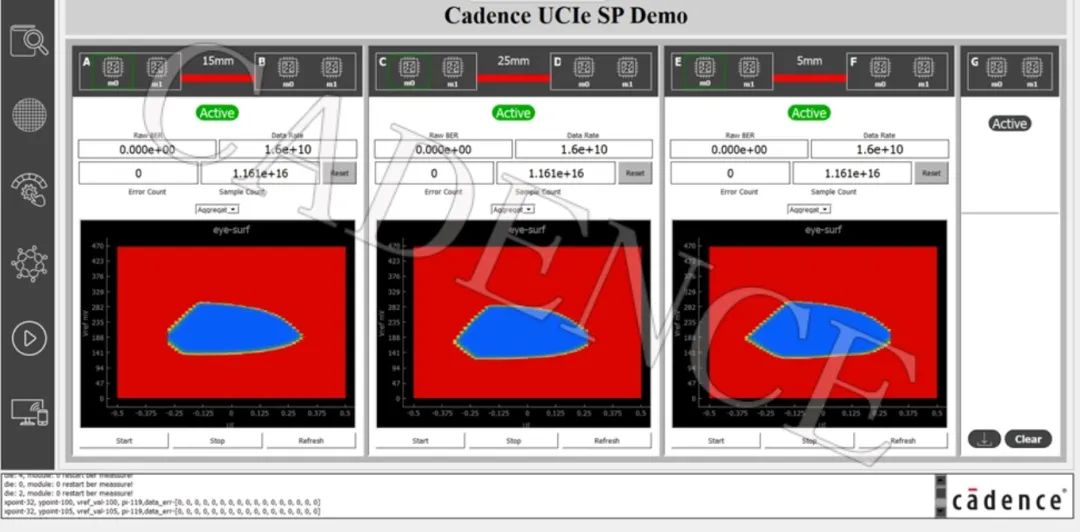

测量显示出优异的特性。各操作频率(16GT/s、12GT/s、8GT/s 和 4GT/s)下的眼图都很清晰,并且链路训练和启动顺利进行。该启动包括完整的链路训练和自校准,无需任何手动覆盖校准循环或“调整”,展示了完全有能力的自训练 PHY。Cadence 演示界面的直观布局使访问者能够轻松理解数据并促进有意义的讨论。

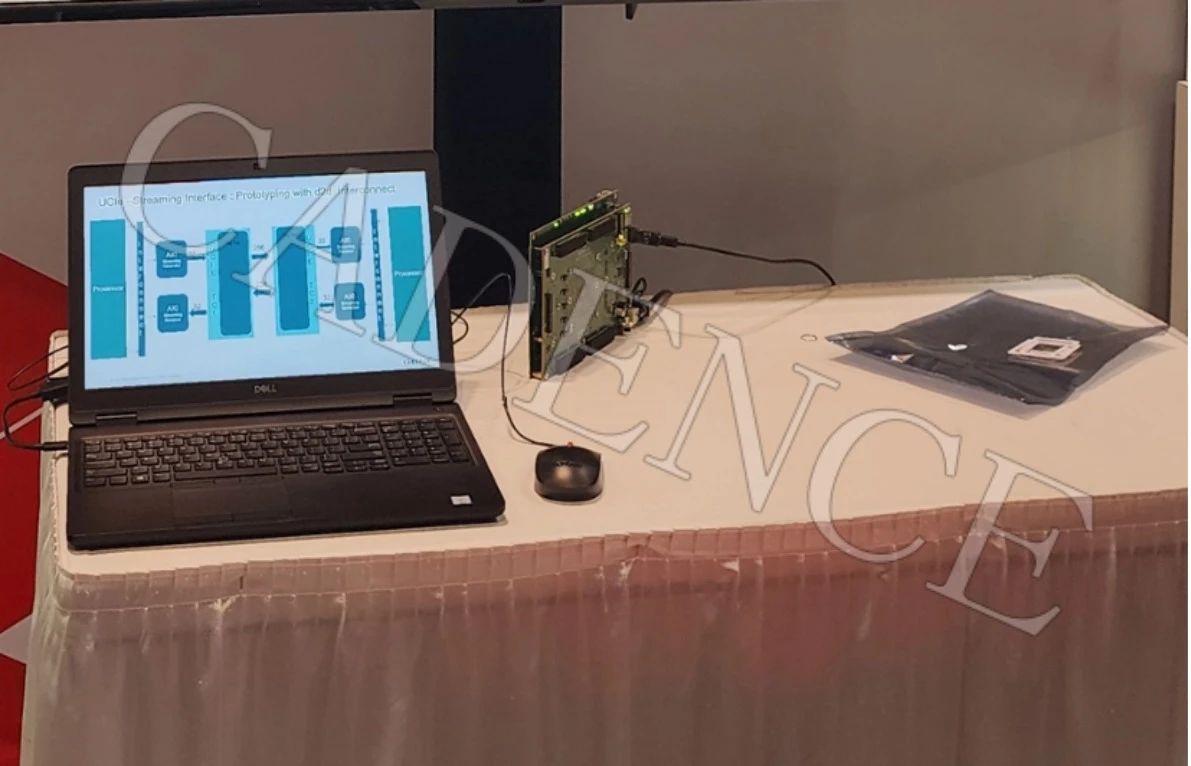

硅样品显示了物理 PHY,而 FPGA 原型演示则显示了控制器和逻辑 PHY。使用 256 位并行接口,它可以构建 16 位 UCIe 接口原型,允许用户在接口两侧构建堆栈,甚至在 UCIe SerDes 和封装互连完成之前也是如此。此项联合开发能帮助客户缩短上市时间,并允许用户在设计周期的早期优化其系统以与 UCIe IP 一起使用。在演示中,原型经历了重置、链路训练状态机(LTSM),之后是任务模式流量,并可选择注入和观察错误。

本篇文章来自于cadence楷登