25.1 版本核心更新亮点如下:

- 适用于先进封装设计的高性能、多层布线器

- 支持倒装、芯-芯互连布线,兼容晶圆厂设计约束

- Allegro X APD Professional(专业版)及Expert(专家版)授权使用

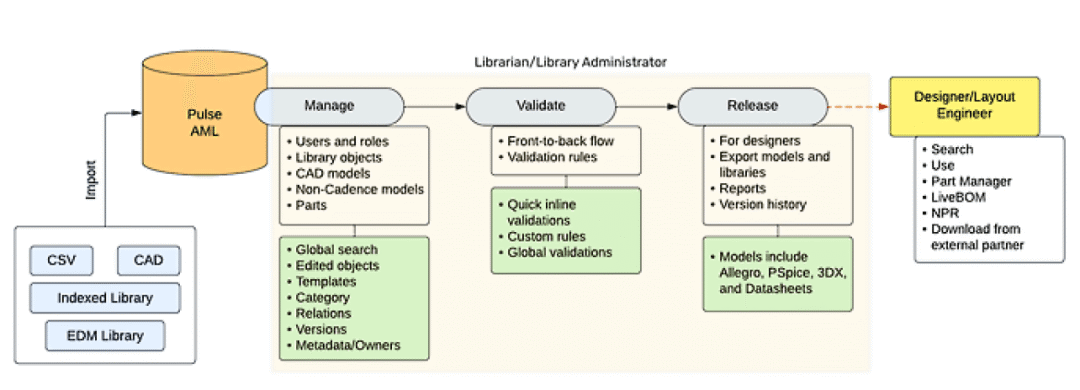

- 与 Pulse 平台深度集成的集中化库管理系统

- 核心功能:版本控制、基于角色的权限管理、生命周期管理、产品生命周期管理 / 企业资源规划(PLM/ERP)系统集成、本地 / 离线使用支持

Allegro X PCB Editor (APD)功能增强

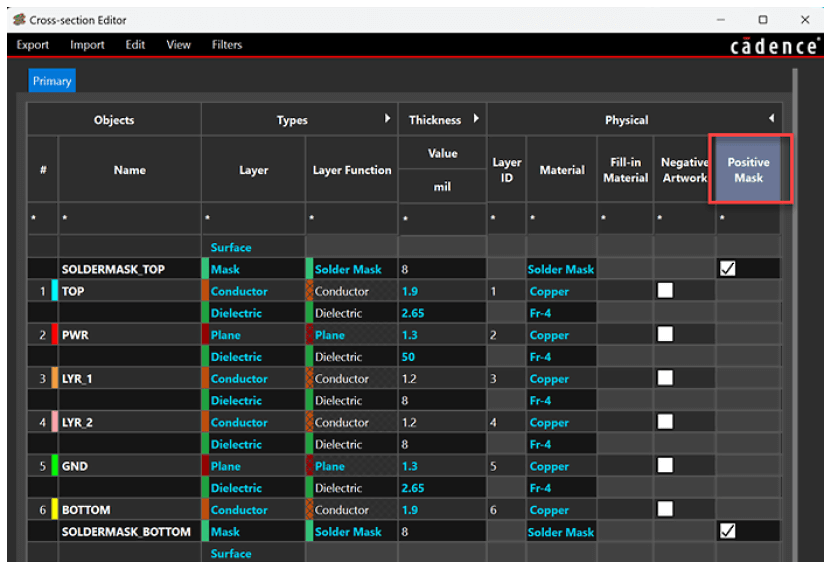

- 正片Mask支持:简化掩模层的可视化操作

- OpenType字体支持:设计输出全流程适配现代字体格式

- 约束面板:支持可停靠操作界面,便捷完成约束的分配与查看

- 差分对自动配置:大幅简化差分对的创建流程

- 智能搜索:可对设计属性 / 偏好设置实现预测性搜索

- 一键式生产数据导出功能:通过统一对话框实现制造、装配与测试相关文件的导出。

- 密度感知型除气设计:保障电路板金属密度均匀性

- 拓扑工作台:强化基于拓扑的约束管理能力

- 3DX 画布功能增强:实现实时 3D 可视化、交叉探测与智能视角切换

- 引脚延迟(Pin Delay)导入功能增强:支持自动识别、有效性校验及选择性导入。

- 快速仿真截取功能:可提取版图截面用于独立仿真。

- 基于区域的金属填充功能:支持按区域 / 图层分配自定义填充图案。

- 金属密度扫描功能增强:新增多项检测项及扫描模式

- 性能优化升级:提升设计规则检查(DRC)、布线、图形处理及三维(3D)视图的运行速度。

- SKILL 语言功能增强:新增及更新多项目自动化与定制化功能。

- 基于文件夹式检查点机制,备份与恢复速度提升至原先的 3 倍。

- 版图编辑功能提升:以增强型编辑工具替代布局规划环节。

- 系统级设计功能:支持多板、多页面的逻辑板设计

- 导航链接报表功能:支持生成网络、引脚及器件的交叉引用报表。

- SnapMagic 集成功能:支持访问外部元器件数据库

- 电应力分析功能:可通过流程管理器对选定集成电路(IC)执行电过应力测试(EOS)。

- 电源拓扑分析功能:提供布局前/布局后独立分析面板。

- 本地库支持功能:可实现带完整格式的离线符号创建。

- 自定义验证规则功能:支持为所有对象类型配置用户自定义规则

- 多封装符号支持功能:可便捷管理各类封装派生。

- 库 CAD 数据导出:支持导出逻辑数据与物理数据。

- 提升大型设计的处理速度,降低内存占用率。

- 可从元器件管理器交叉探测至原理图中的对应元器件

- 针对带有用户覆盖的、从库中导入的属性值的任意器件实例执行同步操作。

- 支持对处于同步状态的器件执行替换操作。

- 可为单个电源轨(组)定义并使用多种容值的电容器件

- 电源与地网络全局查找检索功能(22.1/23.1 增量服务版本)

- 支持基于电压属性 / 数值进行精准检索

- 具备属性删除、显示控制功能

- 多页面批量删除功能(22.1/23.1 增量服务版本)

- 以只读模式查看原理图,支持全功能导航与搜索

- 独立轻量安装包,部署更便捷

- System Capture 功能可完美适配 Pulse 受控库流程

- 集成式元器件数据与逻辑符号制作,支持版本的创建与全生命周期管理

- 封装焊盘的制作与管理

- 功能叠加层设计

- 表格驱动式设计

- 多页面系统级设计

- 基于原理图模板的审计核查

- 支持创建器件分类

- 去耦电容向导功能优化

- 电源树分析

- 设计中热分析

- 工作流辅助式热分析

- 支持执行假设分析,功能包括:

- 切换电源来源,可选用户定义、额定值或应力推导值

- 灵活调整元器件在电路板上的布局

- 支持以表格形式查看元器件的最终温度和功耗数据

- 支持查看各图层的热视图

- 分析模型管理器(AMM)集成

- 拓扑提取 ——TopXP 工具集成

- 动态物料清单(Live BOM)及全局搜索中嵌入元器件清单

- 分析数据汇总功能

- 附件版本全生命周期控制

- 支持零信任网络访问(ZTNA)网页代理部署(开放式授权协议 / OAuth)

- 用户管理组件(Keycloak)版本升级

- Java 运行环境版本升级

- 生产发布(PFM)预验证功能

- 产品生命周期管理(PLM)功能 / 支持矩阵

- 专属逻辑库制作环境,支持原理图模型设计

- 支持符号模板 —— 可快速创建各类图形与符号

- 配备验证框架,支持原理图符号、逻辑与物理设计的兼容性校验

- 支持导入 CSV 格式引脚清单

- 计划支持其他数据格式导入(未来迭代)

- 完备的计算机辅助设计(CAD)库开发与管理平台

- 一体化的制作与数据管理环境

- 支持模板、权限控制、版本管理等结构化库制作能力

- 为完整元器件及关联设计对象提供专属验证框架

- 支持多格式数据交换与报告生成

- 提取 CAD 物理模型的元数据,并将其设为可检索参数

3DX 画布中的板级映射

- 支持封装、器件或机械模型的映射配置

- 为模型浏览、删除、模型颜色设置单独列项,操作更便捷

- 搜索功能 —— 默认前后自动匹配通配符

- 点击列标题,可对模型进行正序 / 倒序字母排序

- 优化模型浏览过程中的精准搜索体验

- 支持映射文件的导入与导出

- 方向键实现视角平移

- 下划线键(_)与等号键(=)实现视角放大 / 缩小

- 按住 Shift 键 + 方向键实现视角旋转

- 新增该格式的导出功能,为英伟达元宇宙(nVidia Omniverse)平台必备导出格式

- 二维画布中旧版的 STEP 封装映射功能已下线,统一使用 3DX 画布映射工具

- 支持冻结铜皮的增量更新,可选择性更新动态挖空区域

- 支持对相邻图层铜皮进行挖空处理

- 过孔残桩优化 —— 按层过渡次数精准管控

- 玻纤布纹理识别:设计规则检查(DRC)可自动标记出超过方均根(RSS)长度、可能布设在玻纤布空隙上的布线

- 支持差分焊盘间的差分对布线

- 支持位号嵌入式显示

- 增强型名称嵌入式显示效果,视觉更清晰

- 可参数化设置的光绘菲林记录

- 优化线宽 / 线距切换及区域进入时的差分对汇聚效果,减少人工修正工作量

- 基于焊盘几何形状重新设计差分对焊盘入口,在符合制造规范的前提下,大幅提升差分对耦合度

- 支持暂时忽略电气时序规则完成布线平滑处理,在时序调谐前缩短连线长度

- 核心设计原则:在满足电气时序规则的同时,保留图层空间,避免整体接口长度增加

1、设计加速工具

- 从元器件管理器交叉探测至原理图中的对应元器件

- 实现库中用户自定义覆盖的注入属性值,与任意元器件实例同步

- 支持对已完成同步的元器件执行替换操作

去耦 / 旁路电容设计

- 可为单个电源轨(组)定义并使用多种容值的电容器件

- 电源与地的全局查找和搜索功能(22.1/23.1 版本紧急服务发布)

- 支持基于电压属性 / 数值进行精准检索

- 具备属性删除、显示控制功能

- 多页面批量删除功能(22.1/23.1 版本紧急服务发布)

免费 System Capture 查看器(无需授权)

- 以只读模式查看原理图,支持全功能导航与搜索

- 独立轻量安装包,部署更便捷

- System Capture 功能可完美适配 Pulse 受控库流程

- 集成式元器件数据与逻辑符号制作,支持版本的创建与全生命周期管理

- 封装焊盘的制作与管理

- 功能叠加层设计

- 表格驱动式设计

- 多页面系统级设计

- 基于原理图模板的审计核查

- 支持创建器件分类

- 去耦电容向导功能优化

- 电源树分析

- 设计中热分析

- 工作流辅助式热分析

- 支持执行假设分析,功能包括:

- 切换电源来源,可选用户定义、额定值或应力推导值

- 灵活调整元器件在电路板上的布局

- 支持以表格形式查看元器件的最终温度和功耗数据

- 支持查看各图层的热视图

- 分析模型管理器(AMM)集成

- 拓扑提取 ——TopXP 工具集成

- 动态物料清单(Live BOM)及全局搜索中嵌入元器件清单

- 分析数据汇总功能

- 附件版本全生命周期控制

- 支持零信任网络访问(ZTNA)网页代理部署(开放式授权协议 / OAuth)

- 用户管理组件(Keycloak)版本升级

- Java 运行环境版本升级

- 生产发布(PFM)预验证功能

- 产品生命周期管理(PLM)功能 / 支持矩阵

- 专属逻辑库制作环境,支持原理图模型设计

- 支持符号模板 —— 可快速创建各类图形与符号

- 配备验证框架,支持原理图符号、逻辑与物理设计的兼容性校验

- 支持导入 CSV 格式引脚清单

- 计划支持其他数据格式导入(未来迭代)

- 完备的计算机辅助设计(CAD)库开发与管理平台

- 一体化的制作与数据管理环境

- 支持模板、权限控制、版本管理等结构化库制作能力

- 为完整元器件及关联设计对象提供专属验证框架

- 支持多格式数据交换与报告生成

- 提取 CAD 物理模型的元数据,并将其设为可检索参数

2、PCB 布局设计

- 支持封装、器件或机械模型的映射配置

- 为模型浏览、删除、模型颜色设置单独列项,操作更便捷

- 搜索功能 —— 默认前后自动匹配通配符

- 点击列标题,可对模型进行正序 / 倒序字母排序

- 优化模型浏览过程中的精准搜索体验

- 支持映射文件的导入与导出

- 方向键实现视角平移

- 下划线键(_)与等号键(=)实现视角放大 / 缩小

- 按住 Shift 键 + 方向键实现视角旋转

- 新增该格式的导出功能,为英伟达元宇宙(nVidia Omniverse)平台必备导出格式

- 二维画布中旧版的 STEP 封装映射功能已下线,统一使用 3DX 画布映射工具

- 支持冻结铜皮的增量更新,可选择性更新动态挖空区域

- 支持对相邻图层铜皮进行挖空处理

- 过孔残桩优化 —— 按层过渡次数精准管控

- 玻纤布纹理识别:设计规则检查(DRC)可自动标记出超过方均根(RSS)长度、可能布设在玻纤布空隙上的布线

- 支持差分焊盘间的差分对布线

- 支持位号嵌入式显示

- 增强型名称嵌入式显示效果,视觉更清晰

- 可参数化设置的光绘菲林记录

- 优化线宽 / 线距切换及区域进入时的差分对汇聚效果,减少人工修正工作量

- 基于焊盘几何形状重新设计差分对焊盘入口,在符合制造规范的前提下,大幅提升差分对耦合度

- 支持暂时忽略电气时序规则完成布线平滑处理,在时序调谐前缩短连线长度

- 核心设计原则:在满足电气时序规则的同时,保留图层空间,避免整体接口长度增加