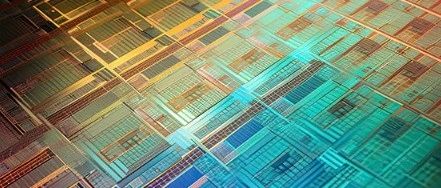

Cadence 签核解决方案助力 Samsung Foundry 的 5G 网络 SoC 设计取得新突破

优势 1 Samsung Foundry 使用 Cadence Tempus Timing Solution 和 Quantus Extraction Solution 成功实现 SF5A 设计签核,并取得了更好的 PPA 结果 2 首次部署 Cadence 签核解决方案后,Samsung Foundry 实现了两倍的生产力提升,加速了设计收敛 中国上海,2023 年 12 月 4 日——楷登电子