IR2110是International Rectifier Company 利用自身独有的高压集成电路及无门锁CMOS 技术,开发的大功率MOSFET和IGBT专用栅极驱动集成电路,已在电源变换、马达调速等功率驱动领域中获得了广泛的应用。该电路芯片体积小(DIP-14、SOIC-16),集成度高(可驱动同一桥臂两路),响应快( ton /tof = 120/94 n s ),偏值电压高(< 600 V ),驱动能力强,内设欠压封锁,而且其成本低,易于调试,并设有外部保护封锁端口。尤其是上管驱动采用外部自举电容上电,使得驱动电源路数目较其他IC驱动大大减小。对于发射机的4 管构成的全桥电路,采用2片IR2110驱动2个桥臂,仅需要一路10~20V电源,从而大大减小了控制变压器的体积和电源数目, 降低了产品成本, 提高了系统的可靠性。

本文通过实例演示,向大家介绍如何使用PSpice对IR2110的驱动电路进行仿真。

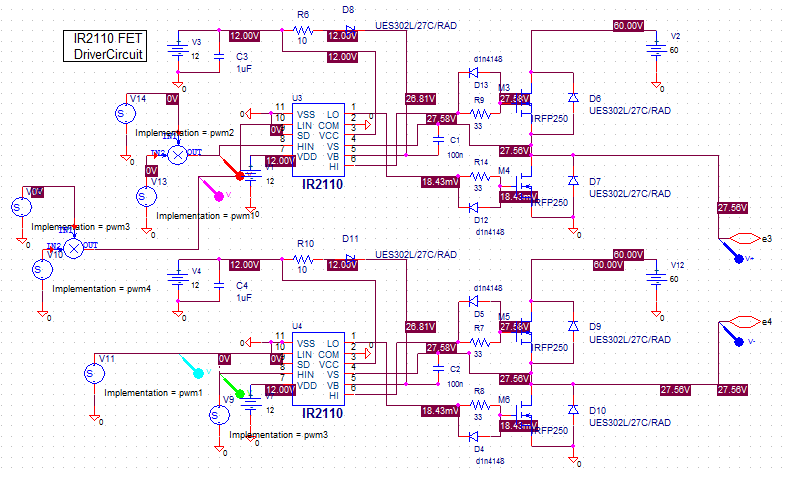

仿真原理图

图1 电路建模与原理图设计

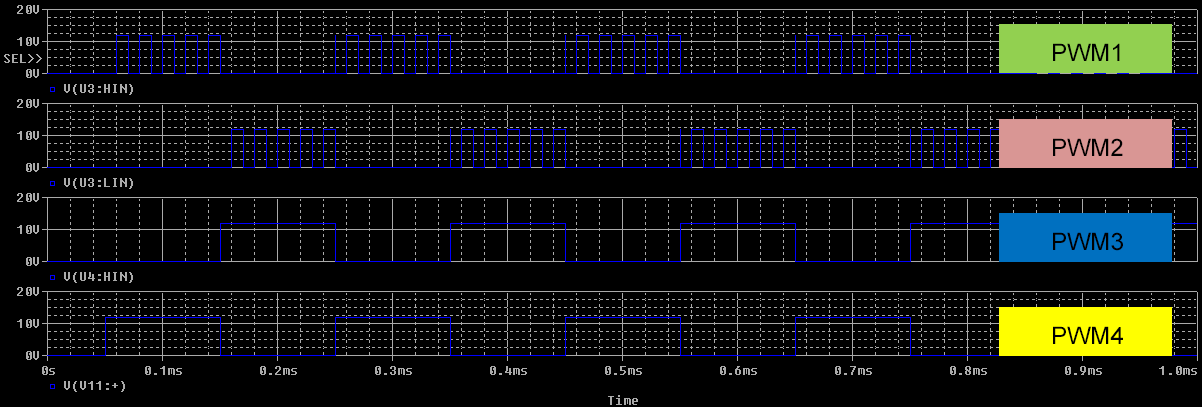

- 激励波形(PWM1~PW4波形如下图)

图2 输入激励波形图

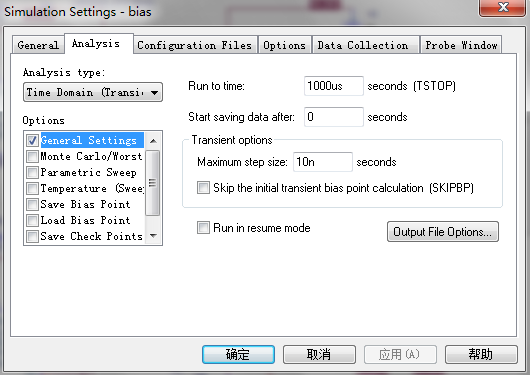

- 仿真设置

仿真运行时间设置为1000us,步进10ns

图3 瞬态仿真设置

输入波形文件编辑:

.STIMULUS pwm1 PULSE( 0 12 10u 10n 10n 100u 300u )

.STIMULUS pwm2 PULSE( 0 1 20u 10n 10n 10u 20u )

.STIMULUS pwm3 PULSE( 0 12 110u 10n 10n 100u 300u )

.STIMULUS pwm4 PULSE( 0 1 120u 10n 10n 10u 20u )

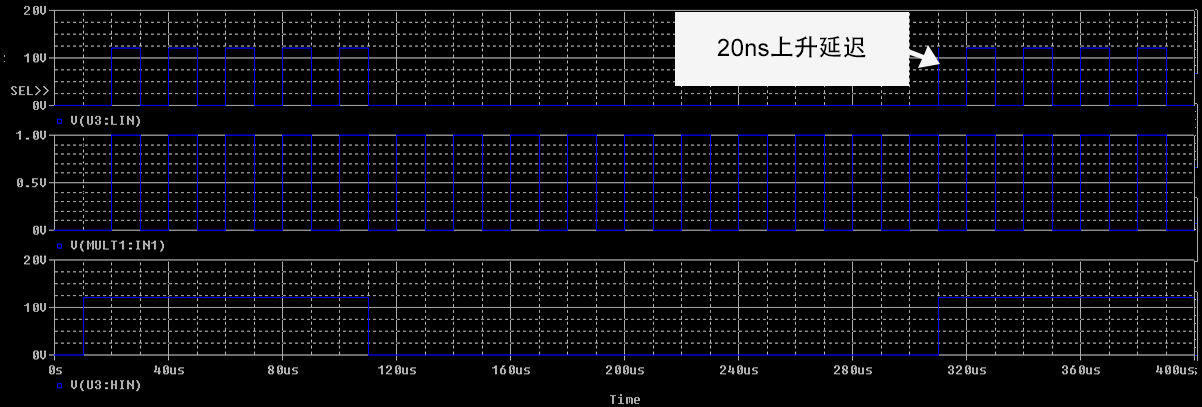

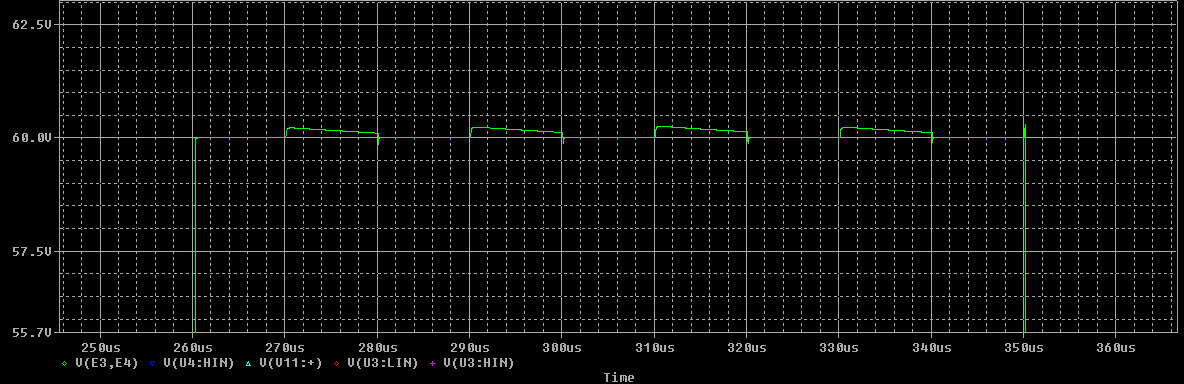

由于IR2110输入LIN端波形需要进行重新编辑,因此,在模拟乘法器运算时会出现一定时间的波形延迟,导致超过250us,即一个周期之后,运算后的激励波形由于上升沿延迟导致出现小毛刺,目前做忽略处理,如下图所示:

图4 输入端波形示意

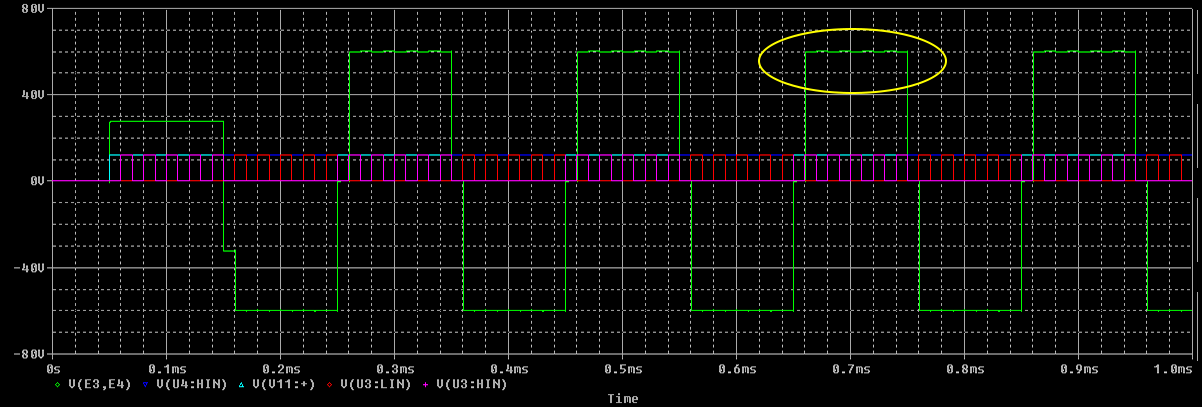

- 空载E3,E4两端波形

图5 空载时E3、E4两端波形

- 带载仿真

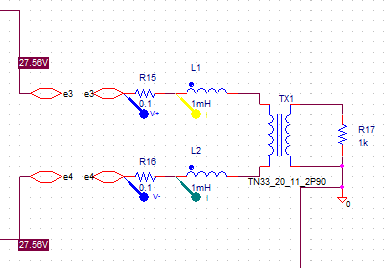

驱动器两端接口E3、E4接入理想非线性变压器输入端,外部引入线圈初级感抗2mH,电阻0.2欧姆。

图6 负载转换通路

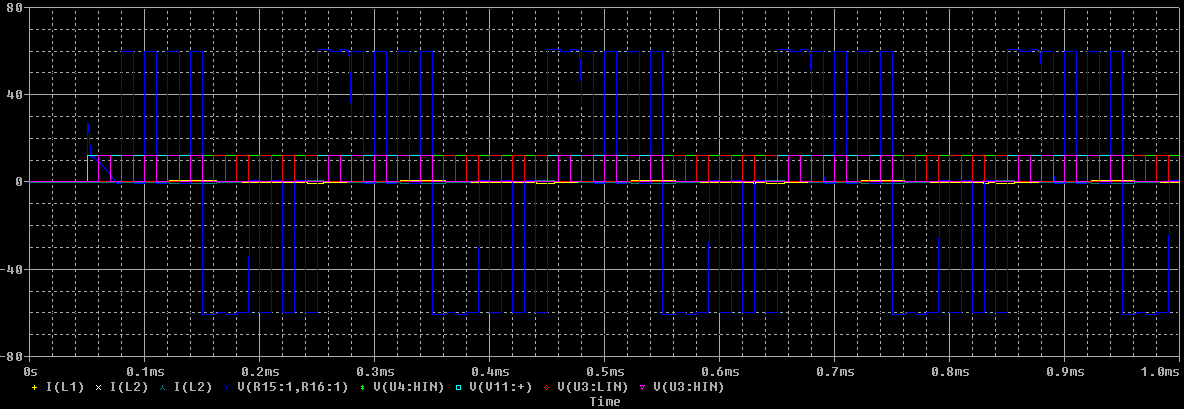

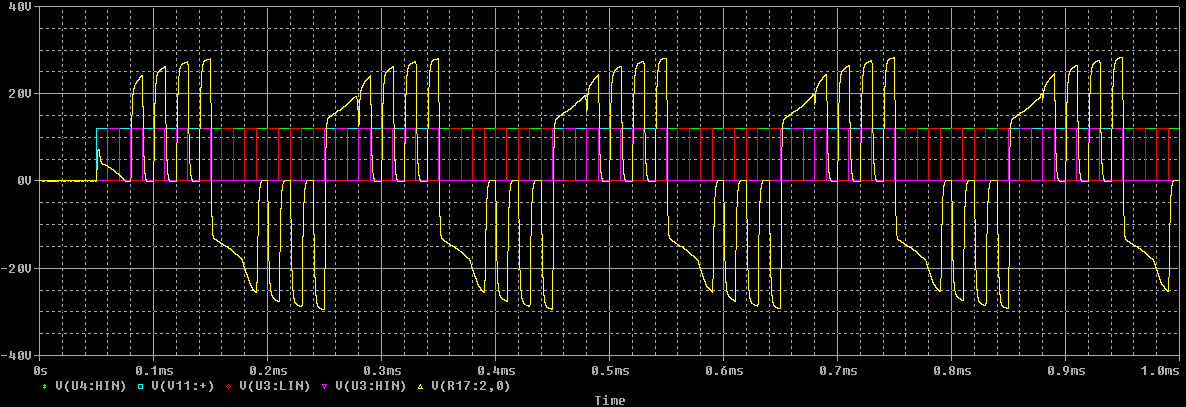

图7 变压器初级线圈两端电压波形(蓝色)

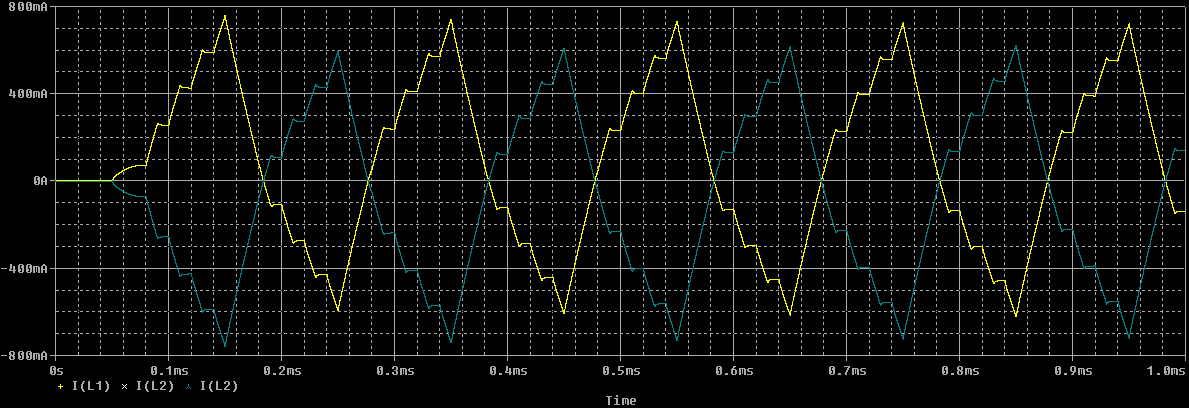

图8 变压器输入两端电流波形

图9 变压器次级线圈两端电压波形(黄色)

总结

通过电路仿真,可以充分了解电路工作过程中每个节点的工作状态,在设计初期完成电路的运行状态分析,可以通过修改电路元件的参数完成电路调试功能,优化电路。仿真过程中,工程师需要充分了解电路的工作特性,并将其应用于仿真设置和参数调整中,这能给电路验证提供很好帮助。

Cadence PSpice的电路仿真,能帮助工程师节省大量的设计时间:查找问题、优化设计。想要更深入地了解或试用Pspice,请联系我们。