技术专题|串行模数转换器PSpice仿真分析(一)

在pspice的仿真中,经常需要使用模数转换,往常,一般忽略模数转换部分,只对其它部分进行仿真。其实,在pspice中,也提供了模数转换模型库,可以在电路中对AD/DA转换进行仿真。

在pspice提供的仿真库中,有一个dataconv库,里面就包含了AD/DA模型。其位置位于“安装路径”\SPB_17.4\tools\capture\library\pspice下。

这里,我重点介绍其中的ADCSER器件。ADCSER是指串行输出的AD转换器,紧接着ADCSER后面的数字,是串行数据的位数,如ADCSER2是指2位的串行输出AD转换器,ADCSER24是指24位的串行输出AD转换器。位数越多,转换的精度就越高。

首先,我们对4位串行输出AD转换器进行仿真。

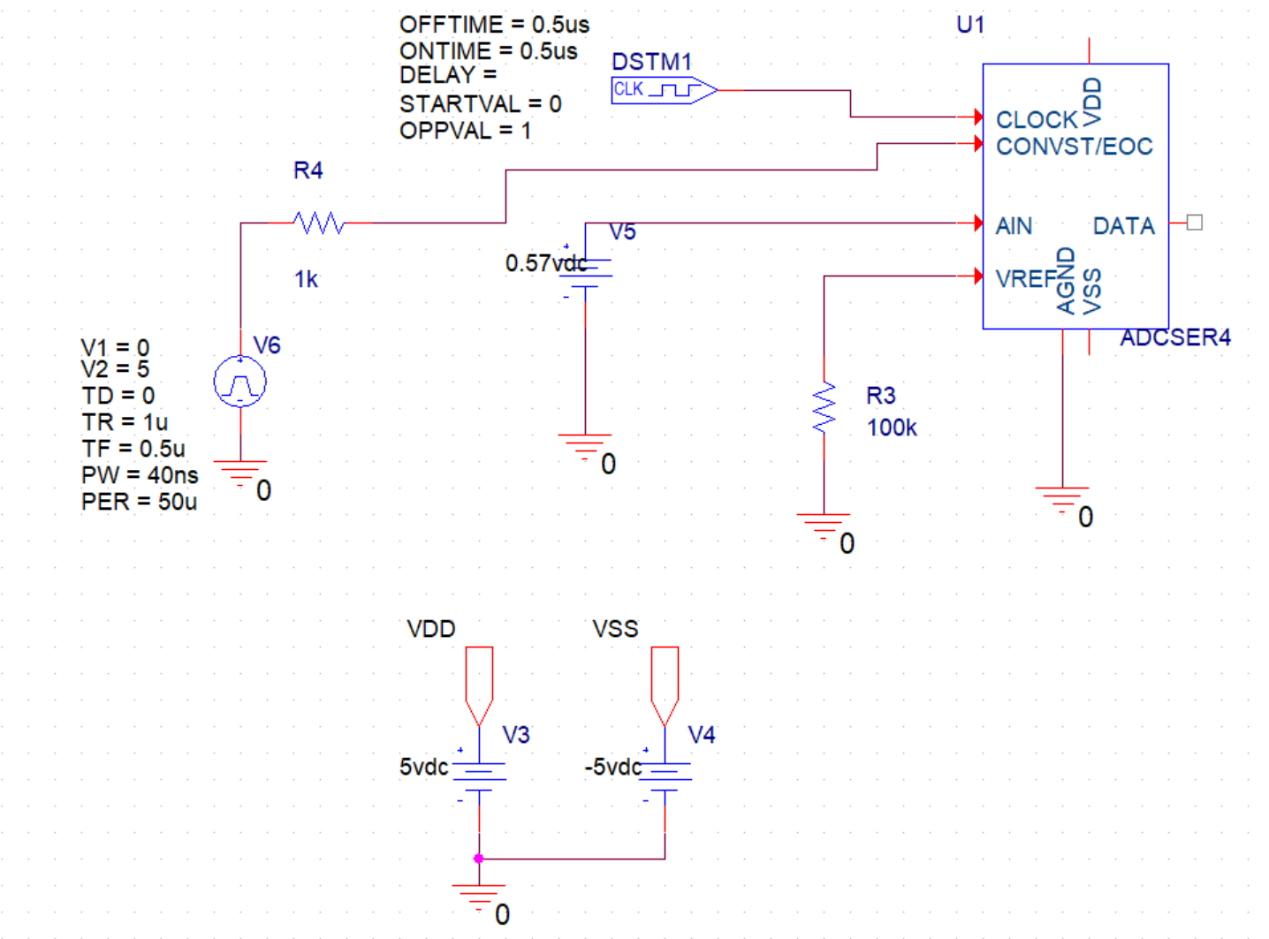

在Capture中创建pspice仿真项目——ADC_DEMO.opj,原理图如下:

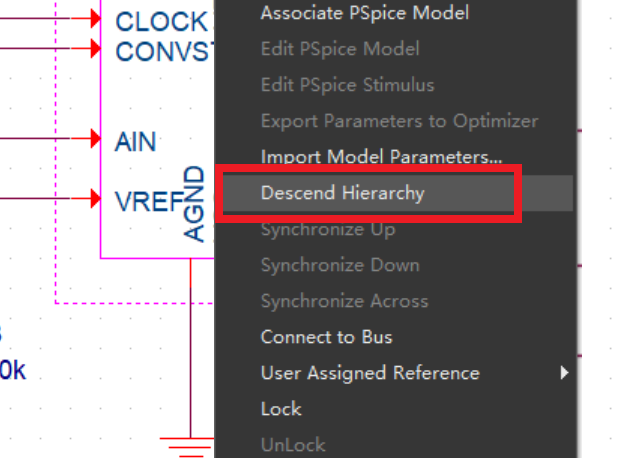

选中模数转换器,点击鼠标右键,选择Desend Hierarchy,可以进入查看模数转换器的内部模型。

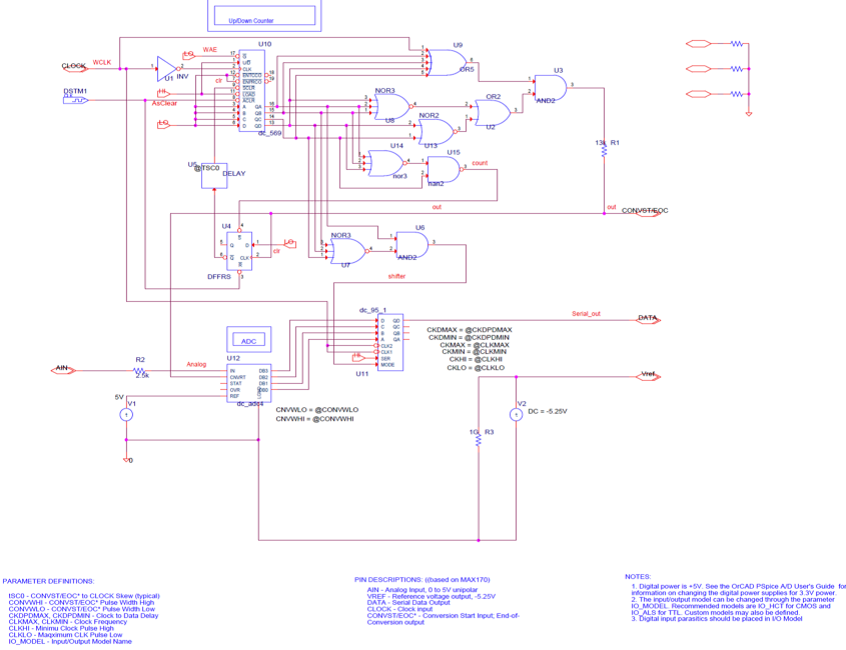

从内部原理图中,不难看出,pspice中提供的ADCSER,是把模拟数据先转换成并行的数字数据,再用D寄存器串行输出。

其中:

AIN – Analog Input, 0 to 5V unipolar(0-5V的模拟输入信号)

VREF – Reference voltage output, -5.25V(参考电压,输出)

DATA – Serial Data Output(串行数据输出)

CLOCK – Clock input(时钟信号输入,要求小于5Meg,大于178.571K)

CONVST/EOC* – Conversion Start Input; End-of-Conversion output(使能信号——开始转换,转换结束)

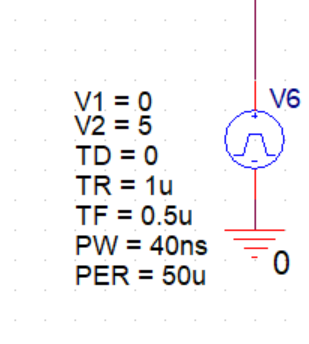

在这个实验中,我们把CLK信号定义为1Meg,Ain采用直流信号输入,CONVST/EOC——使用脉冲信号,周期为50us。

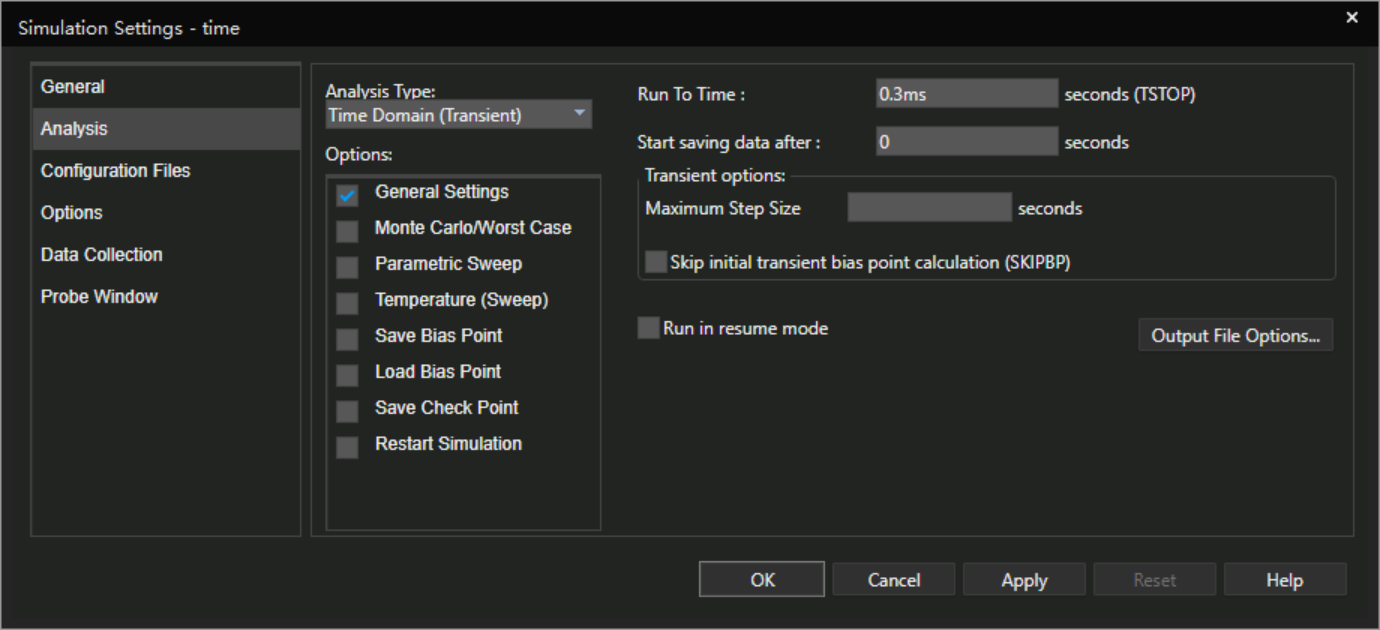

创建仿真分析文件,进行时域仿真:

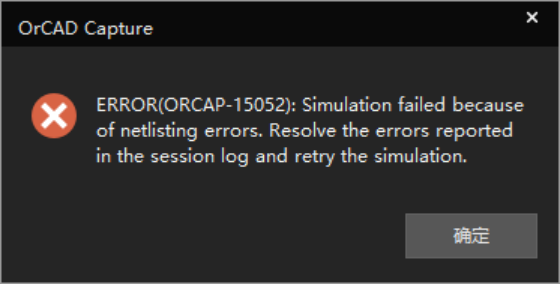

仿真时间定为0.3ms,启动仿真。此时capture弹出一个错误窗口,根据提示,查看session log。

错误提示窗口

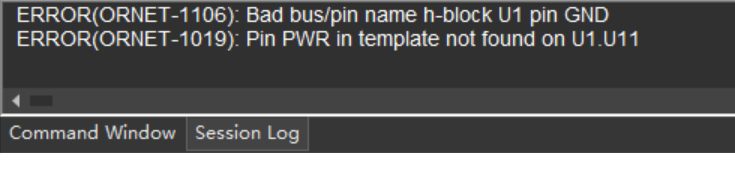

Session Log窗口

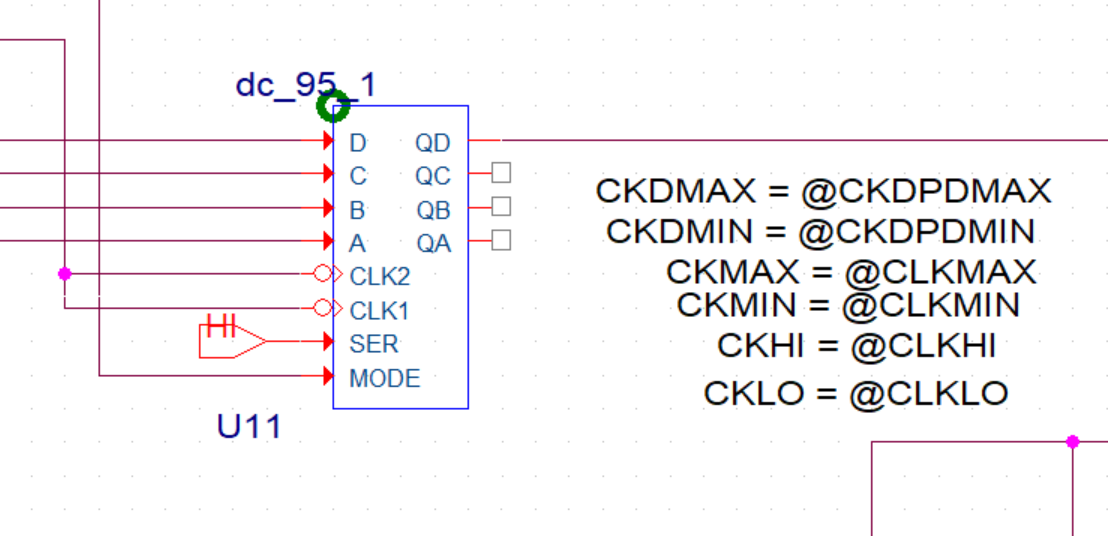

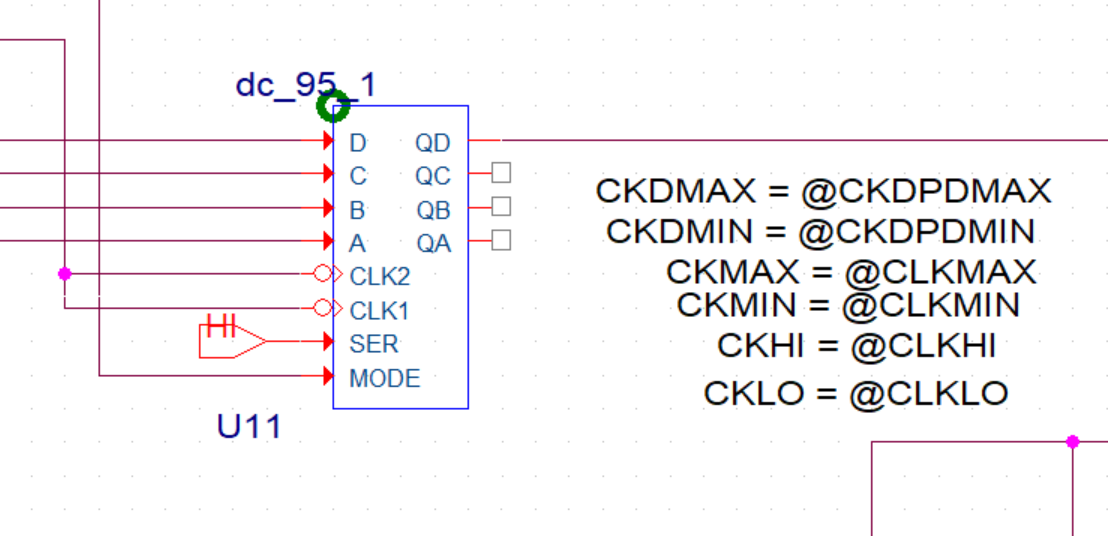

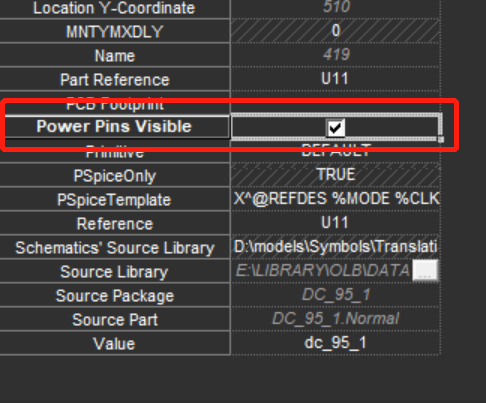

其中有个error:ERROR(ORNET-1019): Pin PWR in template not found on U1.U11,意思是U1.U11的template中管脚PWR错误。进入U1 的Desend Hierarchy,找到U11,如图所示,没有看到名为PWR的Pin,猜测PWR应该是电源管脚,进一步双击U11,进入原件属性,把Power Pins Visible选中,使得元器件的电源管脚显示出来,发现U11的电源pin是VCC和GND。

再次进入U11的属性,找到PspiceTemplate,其内容如下:

X^@REFDES %MODE %CLK1 %CLK2 %SER %A %B %C %D %QA %QB %QC %QD %PWR %GND @MODEL PARAMS:\n+ IO_LEVEL=@IO_LEVEL MNTYMXDLY=@MNTYMXDLY \n+ CLKHI=@CKHI CLKLO=@CKLO CLKMAX=@CKMAX CLKMIN=@CKMIN CKDPDMIN=@CKDMIN CKDPDMAX=@CKDMAX

其中,“%”开头的是管脚的名称,其中有%PWR,而原理图中的U11没有PWR管脚,而是VCC管脚。(猜测:这是Cadence直接从早期pspice导入的模型,导致出现偏差)。

修正方法:直接把“%PWR”修改为“%VCC”,然后保存。再次启动仿真。

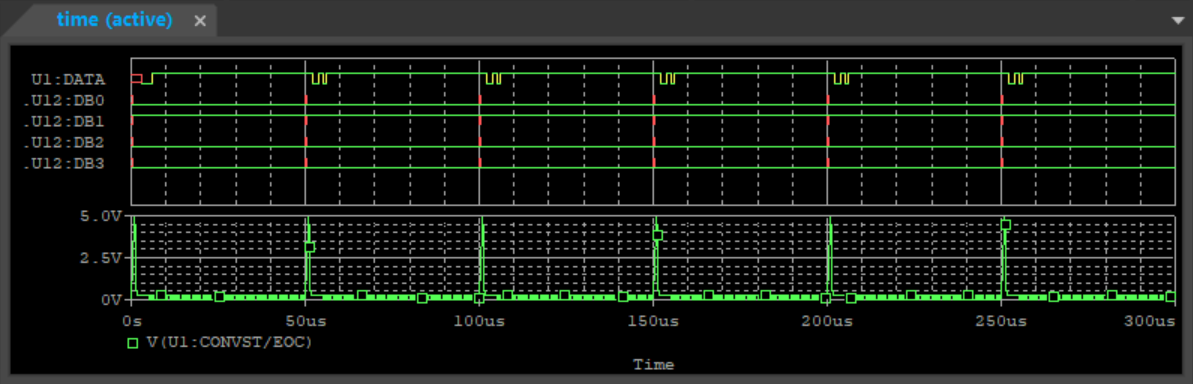

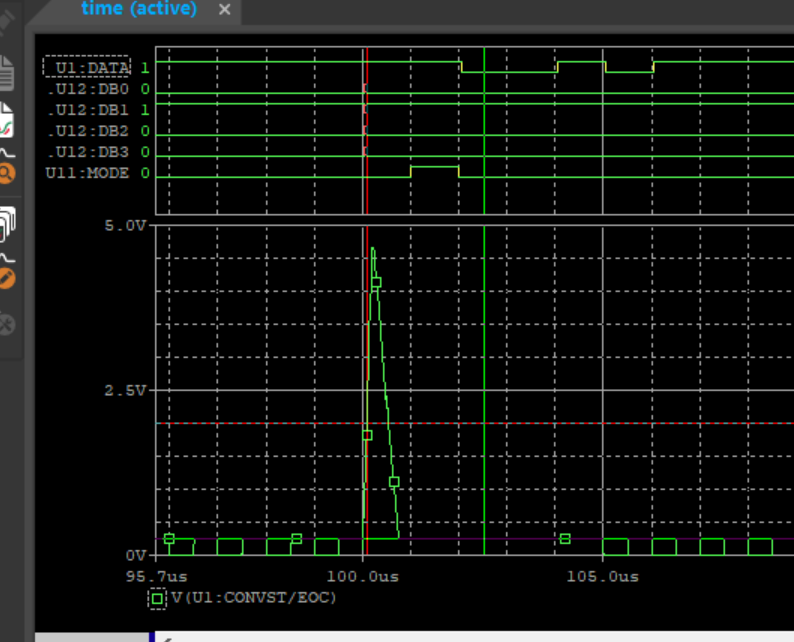

查看U1.U12的DB0~DB3的并行转换结果,与DATA的输出,图形如下:

可以看出,开始转换控制信号送给AD后,AD开始转换并串行输出。

对波形进行放大,可以得出以下结论:

- 模数转换的串行DATA输出,是从高位到低位,串行输出的;

- 每个时钟周期输出1位;

- 从使能信号有效后的第二个时钟周期开始串行输出。