Allegro PCB 设计中布线优化

本文要点 作为一名资深的电子设计工程师,在 Allegro中将走线优化好、散热调整好、阻抗控制精准,能够为后期调试和改板省下不少心力,好处就不用多说了!✨上期我们介绍了如何利用约束管理器去约束我们的走线;本期我们将教会大家如何更快更精准的优化我们的布线。? 应用场景 1. 两条甚至多条高速线(例如:时钟、差分对、高速数据线)长距离紧挨着走线时,它们之间会通过电场和磁场产生能量,就需要在布平行线的时

本文要点 作为一名资深的电子设计工程师,在 Allegro中将走线优化好、散热调整好、阻抗控制精准,能够为后期调试和改板省下不少心力,好处就不用多说了!✨上期我们介绍了如何利用约束管理器去约束我们的走线;本期我们将教会大家如何更快更精准的优化我们的布线。? 应用场景 1. 两条甚至多条高速线(例如:时钟、差分对、高速数据线)长距离紧挨着走线时,它们之间会通过电场和磁场产生能量,就需要在布平行线的时

本文要点 在进行时序等长布线操作的时候,在布线操作的时候不管你是走蛇形线还是走折线,约束管理器会自动帮你计算长度、标偏差,通过精确控制走线长度,来实现信号的时序匹配。约束设计就是一套精准的导航系统,能够在走线的时候清楚的知道目标在哪里,允许的误差是多少、最小间距等。 上期我们介绍了如何使用cadence Allegro的规则“约束”孔,实现一键式快速生成孔;本期我们将教会大家如何利用约束管理器去约

PCB上的过孔放置是一个巨大的工程量,可能是给大电流铺路,可能是给芯片底下散热,或者是屏蔽用的“铜墙铁壁”。传统方式的手动一个个放,调间距,对齐?稍微改个尺寸或位置,好家伙,全得重来!想想就头皮发麻?,打工人的时间不是这么浪费的!Allegro X Designer中的约束驱动过孔阵列功能,简直就是咱打工人的福音!?上期我们介绍了如何使用约束管理器设置差分对的约束条件,同样是约束;本期我们将教会大

本文要点 在 PCB、集成电路和线缆组件中,最常被提及的串扰现象是接收端器件观测到的远端串扰。 带阻滤波器与带通滤波器作用相反:它们能滤除特定频率范围内的干扰信号。 带阻滤波器的传递函数可通过计算得出,也可以使用 SPICE 仿真器获得。 还记得那些需要插到墙面上的老式电话机吗?在电话系统数字化之前,通电话时偶尔能听到其他人交谈的微弱回声。这种杂音是因电话线缆中不同导线间的信号混合在一起而产生的,

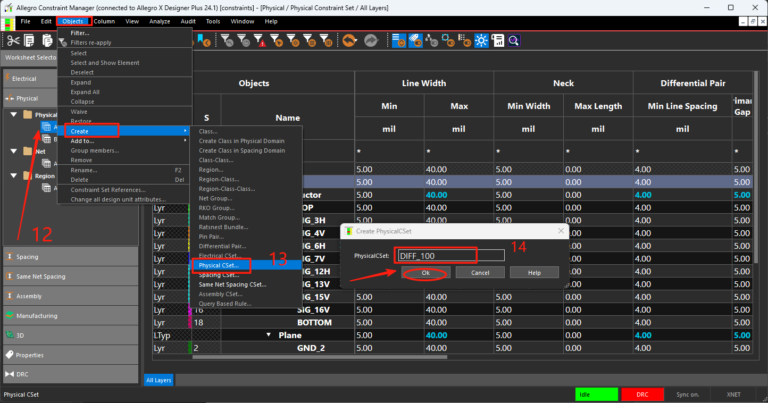

本文要点 你是否经常在Layout设计中抓瞎?,拿着板子无从下手,拿着鼠标深夜狂按?;DDR等长没做好导致系统不稳定,PCIe没设相位容差造成链路训练失败……这些都是血泪教训,关键时刻需要靠约束管理器救命!Allegro约束管理器搞差分对,简直是把高速设计的「地狱模式」切换成「新手村」!✨ 上期我们介绍了盲/埋孔的使用,本期我们将教会大家如何使用Cadence的约束管理器,用最少的时间一键速通La

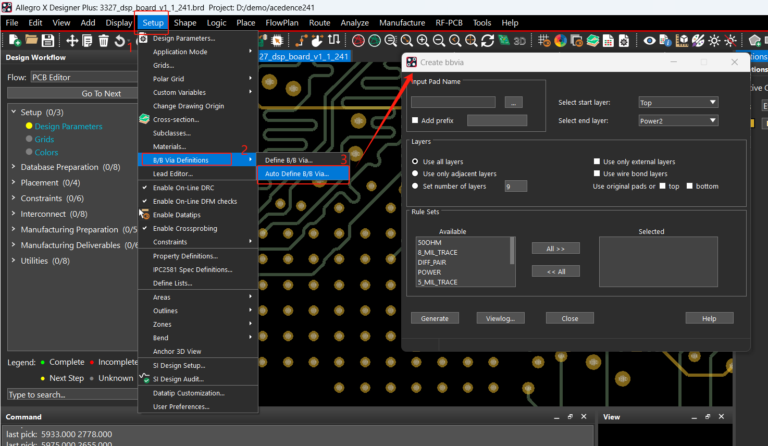

前言 巴掌大的板子里密密麻麻的布线,传统的通孔像早高峰上的立交桥的“大柱子”杵在那里,走线全凭运气,绕路、打结、信号互相干仗…改版改到怀疑人生?,面积还死活压不下去,使用Allegro X Designer Plus 的B/B Via,瞬间“格局打开”,布线开挂,效率飞起。✨ 上期我们介绍了如何创建了B/B Via焊盘,本期我们将教会大家如何使用 Allegro X Designer

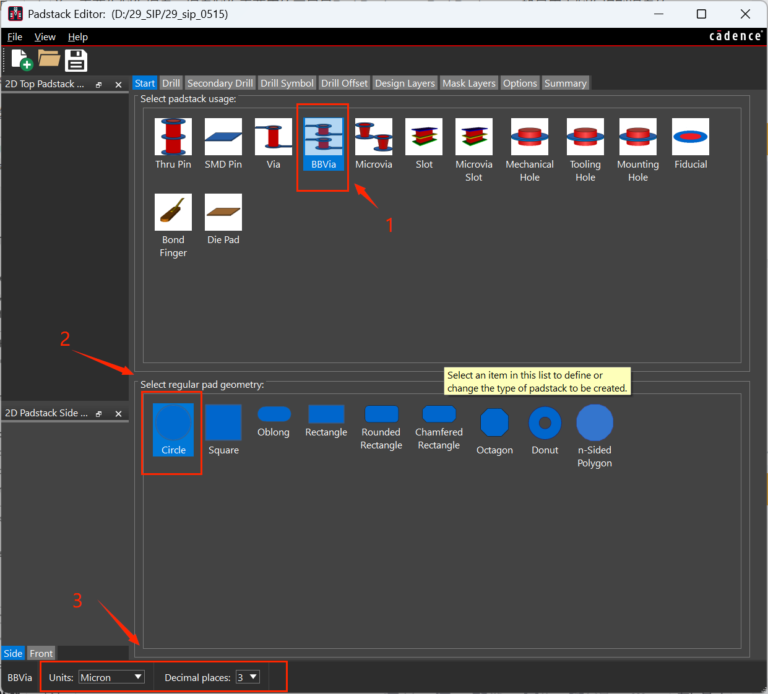

大家好!今天我们来介绍高密PCB设计中通常会使用到的类型BB Via制作流程。BBVia:BBVia是通过多层PCB板中的表面覆铜孔层、内部覆铜孔层或内部掩铜层连接的盲孔和埋孔结构。 应用场景 1、走线需要从顶层(或底层)直接连接到中间某一层(而非贯穿到底层)时,需要使用BB Via,它能有效减少过孔占用表层空间。 2、BB Via的孔径通常较小(如0.1mm以下),且不穿透全部层,适合在有限空间

本文要点 PCB 边缘连接器是实现高速数据传输和模块化组装的首选系统集成解决方案。 在电路板边缘和连接器之间的适当匹配中,需要采用斜切工艺来保护连接器引脚。 边缘连接器的选型取决于连接板的组装要求和制造约束条件。 PCB 边缘连接器采用多条并行数据线实现高数据吞吐量。 在系统集成中,各器件的形状和尺寸不一:设计人员可以根据电路板的制造需求调整连接器,而在所有连接器中,PCB 边缘连接器最为突出。边

在描述高速运行的数字系统时,噪声容限是最重要的参数之一。通常情况下,噪声容限定义了 I/O 引脚上或接口中可接受的噪声水平。在数字电子技术领域,噪声容限是指 I/O 引脚上出现但不会导致接收逻辑状态出错的噪声水平。这个值在时域中经常调用,用于测量比特误码率。 如果您正在设计高速 PCB 并需要执行串扰检查,首先应明确评估成功的具体标准。从数字器件的 CMOS 噪声容限值入手是个不错的选择,因为这些

许多电子系统和产品并不只使用 1 个 PCB,而是可能包含多个电路板、单个电路板和多个外部模块,或者通过电缆与外部设备连接。在多板系统中,两个电路板之间可能会出现逻辑错误,但如果没有全面审查设计,可能到电路板原型制作结束后,也无法发现这些错误。幸运的是,您可以采取一些简单的解决方案和设计选择,避免电路板之间出现这些逻辑连接错误。 什么是电路板之间的逻辑连接错误? 逻辑错误是指两块 PCB 之间的网

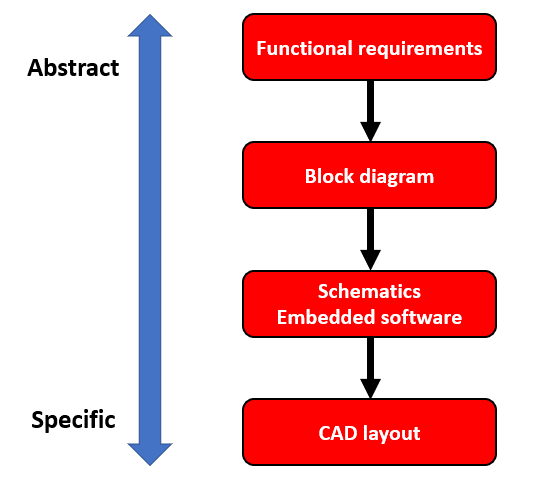

如果您是一位电子产品设计师,并且对软件开发有所了解,或许已经感受到了新产品技术发展的迅猛态势。在工业、商业和消费领域等各个领域的新产品,都开始使用嵌入式系统。这些产品不仅采用先进的 PCB 设计,还需搭配定制软件。要让这些新产品成功上市,应采用怎样的最佳开发流程呢? 硬件设计师正在借鉴软件开发团队的经验,在开发初期实施系统级设计。了解系统建模和抽象层次在硬件和软件设计中的作用,不仅可以促进跨职能开