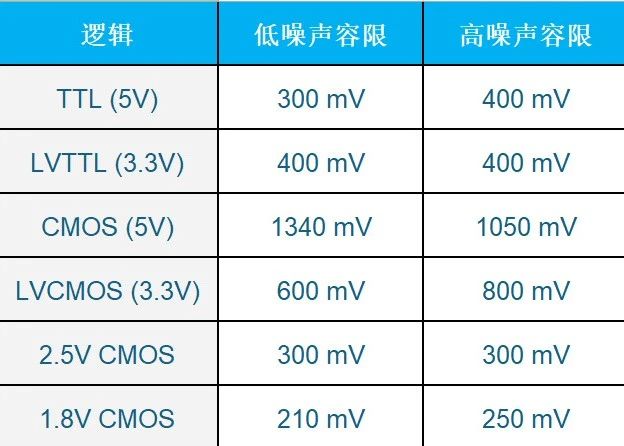

如果您正在设计高速 PCB 并需要执行串扰检查,首先应明确评估成功的具体标准。从数字器件的 CMOS 噪声容限值入手是个不错的选择,因为这些器件很可能是采用 CMOS 工艺制造的。

核心电压已降至 1.8V 以下(例如 1.2V、1.0V 和 0.8V),这些器件的噪声容限也随着核心电压的降低而下降。大多数采用 CMOS 工艺制造的常见数字 ASIC 和微控制器都在 LVCMOS 核心电压水平下运行。

- 地弹

- 串扰

- 电源轨噪声

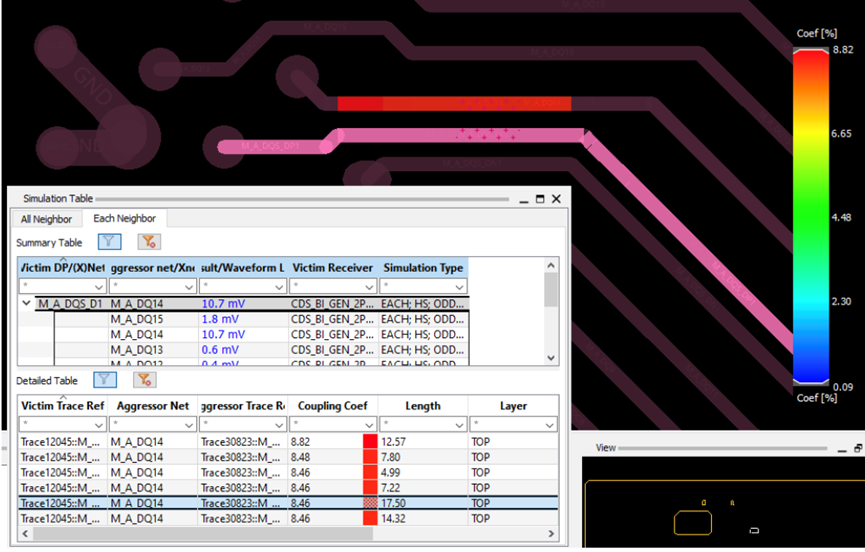

例如,下图中的串扰仿真示例显示串扰比率(受害者峰值电压与攻击者峰值电压)为 8.46%。当攻击者的峰值信号水平为 1.8V 时,峰值串扰为 152 mV,略低于此示例接口的噪声容限。

上述问题中的最后一项(即电源轨噪声的 I/O 噪声)较难理解,因为电源轨噪声并不会以 1:1 的比例传输至 I/O 输出。这是由 CMOS 缓冲电路的性质所决定的,其中涉及半导体裸片上的诸多晶体管和无源元件。正因如此,业界开发了兼顾电源影响的 SI 仿真工具,以更精确地分析电源轨噪声对 SI 的影响。目前,I/O 上的噪声必须作为注入电源轨噪声的函数进行测量。这种测量方法较为复杂,无法直接适用于所有 PCB 堆叠。

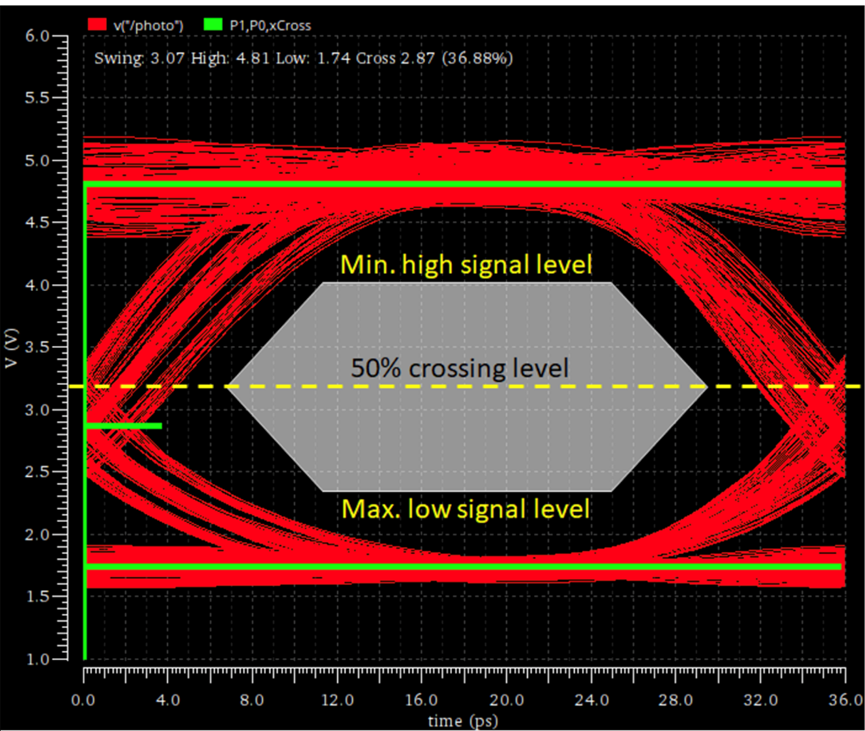

高级信号完整性仿真器允许用户指定眼图模板,以便根据仿真数据计算比特误码率。这些仿真器可以直接处理 PCB 布局数据,并确定串扰、ISI 和抖动的合理准确估计值。虽然噪声容限是这些仿真的一项输入参数,但无需手动检查眼图中的每条轨迹,即可判断通道的合规性。

如需加快 CMOS 接口噪声容限的分析速度,可以使用 Cadence 的系统分析工具组合评估高速数字系统。新一代 Sigrity X 可以与 Clarity 3D Solver 配合工作,并与 Allegro X PCB Designer 和 Allegro X Advanced Package Designer 工具紧密集成。这一全新特性可以帮助 PCB 和 IC 封装设计师将端到端、multi-fabric 和多电路板系统(从发射端到接收端或从电源到耗电端)相结合,确保 SI/PI 成功签核。

本篇文章来自于cadence楷登

关于 Cadence