摩尔定律(Moore’s Law)的放缓以及先进工艺节点成本的不断攀升,正推动着先进封装技术的发展, 进而催生了采用硅基板的芯片堆叠技术,并将其应用于各类场景中。随着芯片堆叠技术的出现,堆叠体各组件及整个系统的复杂性显著增加,新的三维(3D)实现与系统规划挑战也随之浮现 —— 设计过程中需额外考量整个堆叠系统在机械、电气及热学方面的特性。若要实现高效运行的三维集成电路(3D-IC) 堆叠体,关键在于开展系统级规划与实现工作,并结合闭环嵌入式系统级分析。Cadence 完整 3D-IC 平 台(Integrity 3D-IC Platform’s)作为行业内首个全面且综合的三维集成电路设计规划、实现与分析平台, 能够以完整的系统视角,针对芯粒(chiplets)开展系统驱动型的性能、功耗与面积(PPA)优化,并为三维集成电路应用场景下的中介层、封装及印制电路板(PCB)提供协同设计支持。

概述

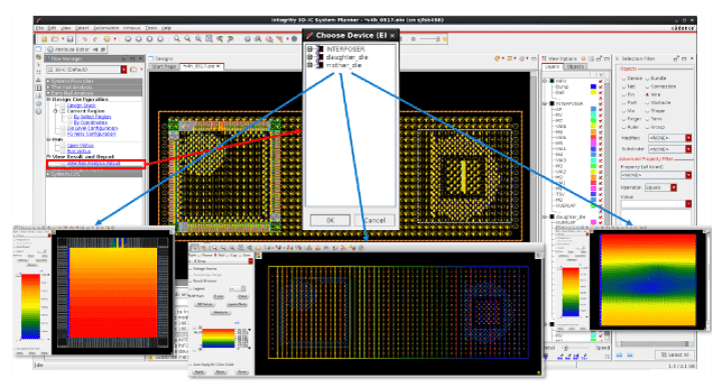

Integrity 3D- IC 设计与分析平台(图 1),该平台基于 Cadence 领先的 Innovus Implementation System 基础设施构建,可帮助系统级设计人员对采用各类封装形 式(2.5D 或 3D)的任意堆叠管芯系统进行规划、实施与分析。该平台提供了行业内首个集成化的综合系统级与片上系统(SoC)级解决方案,不仅支持系统分析技术,还能与 Cadence 的 Virtuoso 平台、 Allegro 模拟电路实施环境及封装实施环境实现协同设计。

Integrity 3D-IC Platform’s 提供了一个集成化流程管理器,可在设计流程早期配置系统级分析功能,涵盖热分析、功耗分析、管芯间静态时序分析及物理验证;该管理器不仅能助力实现单个管芯层面的高效收敛,更可确保整个系统层面的高效收敛。

主要特性与优势

➢ 全新单控制中枢式大容量三维设计规划与实施平台,该平台可支持代工厂所赋能的各类三维集成电路(3D-IC)堆叠结构。

➢ 与 Virtuoso 和 Allegro 环境联动的强大跨平台协同设计能力

➢ 简洁高效的流程管理器,可用于开展早期功耗 – 热分析、跨管芯静态时序分析及管芯间物理验证

➢ 借助系统规划器实现的、面向系统级设计的独特分层规划与优化能力

➢ 通过基于 TCL(工具命令语言)的实时直接集成,与 Innovus 实施系统(Innovus Implementation)联动,实现完整的堆叠管理、芯片到封装的信号映射,以及先进的凸点 (bump)与硅通孔(TSV)规划。

➢ 强大的从 2D 到 3D 探索流程,该流程适用于同构堆叠管芯探索,可支持 “逻辑上集成存储” (memory-on-logic)与 “逻辑上集成逻辑”(logic-on-logic)两种探索场景。

➢ 高效的磁盘数据库,用于实现每层(tier)的分层多级表示。

借助系统规划器(System Planner)与 Innovus 实施系统(Innovus Implementation)开展设计 规划与实施

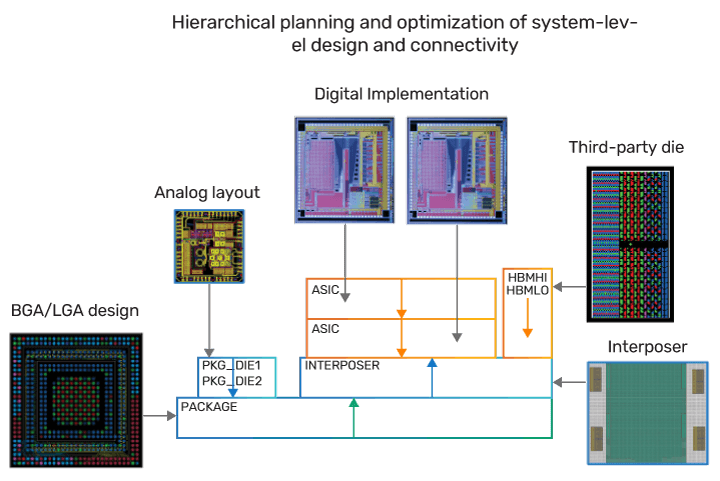

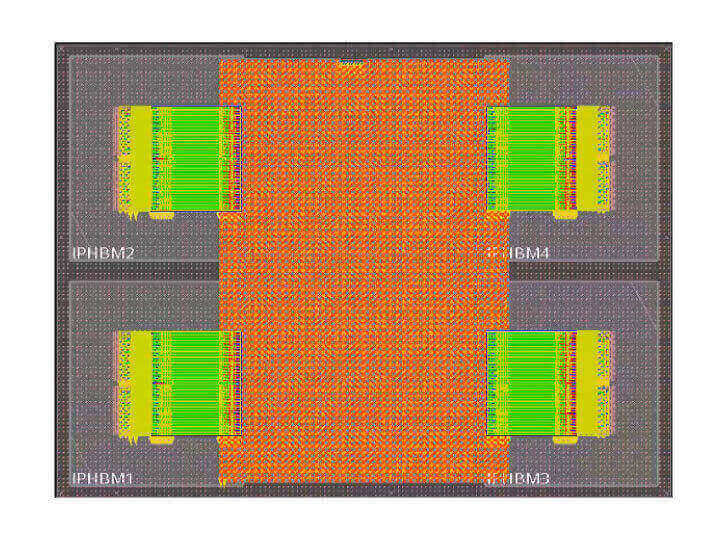

Integrity 3D-IC Platform’s 的系统规划器可帮助设计人员搭建并集成三维(3D) 设计中的所有堆叠器件,包括数字管芯、模拟管芯、封装以及印制电路板(PCB)。与布局视图包含的海量设计数据不同,系统规划器为三维集成电路(3D-IC)系统提供了轻量化视图,重点关注管芯间堆叠 配置、布局规划、管芯间接口设计及优化。布局实施基于完整的 Innovus 数据库运行,具备数字集成电 路(IC)设计人员所需的全部布局、布线及优化功能,同时提供了设计三维系统的数字管芯或中介层时 所需的三维分区功能。

此外,完整 3D-IC 平台(Integrity 3D-IC Platform’s)还提供多管芯布局视图,设计人员可在单一图 形用户界面(GUI)中查看采用不同工艺节点的多个管芯,并显示系统分析结果,以便调试和定位跨管芯 设计问题。完整 3D-IC 平台(Integrity 3D-IC Platform’s)赋予设计人员灵活切换系统规划器与布局实施 功能的能力,实现无缝衔接(图 2)。当管芯布局规划、凸点(bump)、硅通孔(TSV)、输入输出焊 盘(I/O pad)及硬核宏(hard macro)发生变更时,设计数据可在规划器中进行推送或拉取,确保所有 堆叠器件间的数据始终保持同步。

图 2:系统级设计与互连的分层规划及优化

完整 3D-IC 数据库

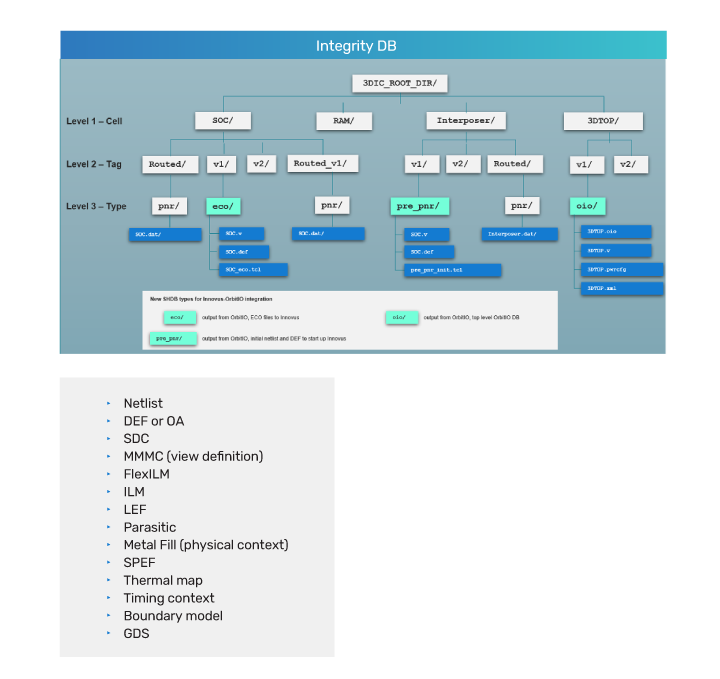

完整 3D-IC(Integrity 3D- IC) 开发的核心是一个通用分层多技术数据库,该数据库可将系统、封装、 基板与集成电路(IC)的多个堆叠层(tier)连接起来。该数据库能够支持读取属于不同工艺节点的多个技术文件。每个三维集成电路(3D-IC)器件的设计数据均在这个单一数据库目录下进行存储和整理。数据库内置的 TCL(工具命令语言)命令,可便捷地实现设计数据库与分析结果的读取、写入、更新、显示及叠加操作。作为 Innovus 实施系统(Innovus Implementation)分层数据库的自然延伸,完整 3D-IC (Integrity 3D- IC) 数据库(图 3)还支持处理本身属于分层设计的数字管芯。

图 3:Integrity 3D-IC 设计数据库元素

数字芯粒与模拟 / 射频(RF)及封装的协同设计

对于模拟或射频(RF)设计而言,其主要的实施平台是 Virtuoso 环境。完整 3D-IC(Integrity 3DIC) 通过系统规划器与 Virtuoso 环境建立接口。在 Virtuoso 环境中完成的设计,其凸点(bump)数据 可被传输并读取到完整 3D-IC 平台(Integrity 3D- IC Platform)中的其他管芯,从而为第二个管芯上的连接凸点确定最佳位置。Cadence 支持 OpenAccess 数据库,该数据库为 Innovus 与 Virtuoso 平台之间的互操作提供了原生统一的数据库。借助 OpenAccess 已有的数据交换能力,进一步实现了 Virtuoso 与完整 3D-IC (Integrity 3D- IC)环境之间的设计数据交换。

集成电路封装:硅 – 封装 – 电路板设计流程中的关键环节。Allegro 环境为印制电路板(PCB)和复杂封装的设计与实施提供了完整且具备可扩展性的技术支持。Cadence 的集成电路封装设计技术能够帮 助设计人员针对复杂的单管芯与多管芯引线键合(wire bond)及倒装焊(flip-chip)设计,在成本和性能方面进行优化,同时满足紧迫的项目时间要求。来自 Allegro 环境的集成电路封装数据库可直接导入至 完整 3D-IC 平台(Integrity 3D- IC Platform),用于实现与中介层(interposer)和基板(substrate)的 凸点(bump)连接。这使得封装协同设计得以实现 —— 设计人员可在单一环境中统筹考虑整个系统, 从而显著简化封装设计环节。

原生三维实施流程

完整 3D-IC (Integrity 3D- IC)提供一系列原生三维堆叠子流程。通过将二维网表拆解为多层级三维堆叠结构,用户能够进一步探索三维堆叠管芯系统相较于平面二维单管芯设计在 PPA(功耗、性能、面 积)方面的优势。

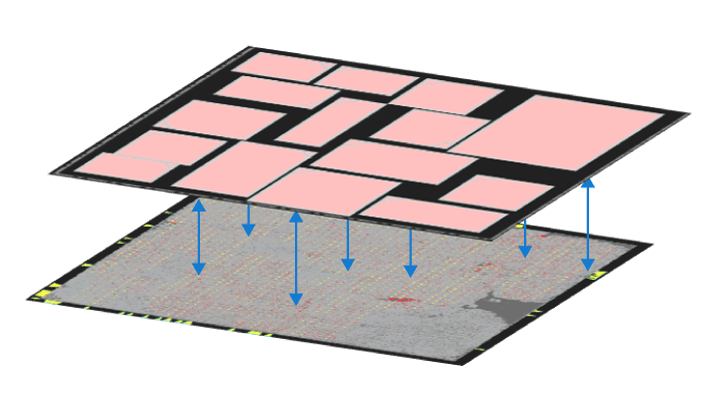

众所周知,受摩尔定律中 “存储墙” 限制(即片上存储的容量与速度无法跟上处理器设计中晶体管 数量的增长速率)的影响,将存储管芯堆叠在逻辑管芯上方成为一种主流的三维堆叠方案,可有效降低存储延迟。完整 3D-IC (Integrity 3D- IC)借助 Innovus 实施系统中独特的混合布局技术,从二维设计中分离出存储宏单元(memory macros),并自动将其分区实现为两个同构堆叠层(tier)— 上层为存储 管芯,下层为包含标准单元逻辑(standard cell logic)的逻辑管芯(图 4)。由于部分逻辑(如测试逻辑) 可能需要与存储单元位于同一管芯,该流程还支持用户控制:通过选择性地将宏单元和逻辑分区分配至不同堆叠层,满足个性化设计需求。此流程依托三维混合布局(3D mixed placement)、虚拟凸点分配 (shadow bump assignment)以及设计物理展开技术,实现时序感知(timing-aware)的全布局堆叠设 计。完成上述步骤后,用户可继续执行标准的实施流程(如时钟树综合(CTS)、优化、布线及布线后 步骤),如同常规布局布线流程一般,最终完成三维设计实施。

图 4:“逻辑上集成存储” 流程的同构三维堆叠

硅中介层专用布线技术

Cadence 的 NanoRoute 高级数字布线器是行业领先的统一布线与互连优化解决方案, 可帮助您在数字设计实施过程中快速实现时序、面积、信号完整性及可制造性的协同收敛(图 5)。 NanoRoute 工具能够应对模块级与全芯片级的各类布线挑战:它兼具基于网格布线器的性能优势与离网布线的灵活性,同时会结合三维效应对时序、面积、功耗、可制造性及良率的影响,评估并优化互连拓扑结构,从而支持在先进工艺或主流工艺技术节点上实现高性能设计的实施。

图 5:芯片级数字设计实施示例

图 5:芯片级数字设计实施示例

这确保了一条顺畅的设计流片与量产芯片交付路径,同时还能评估并优化信号完整性、可制造性感 知、布线和时序这些相互关联的目标,以实现更快的设计收敛 —— 而这一切都不会偏离设计初衷。

自动布线解决方案可借助专用命令实现全自动中介层布线,从而采用总线布线模式连接宏单元凸点 (macro bumps)。该自动布线解决方案的优势包括:

➢ 接近 100% 的高屏蔽率

➢ 极快的运行时间(以分钟为单位)

➢ 均匀分布的线长

➢ 最少过孔数量

Flow Manager for Early Analysis Flows

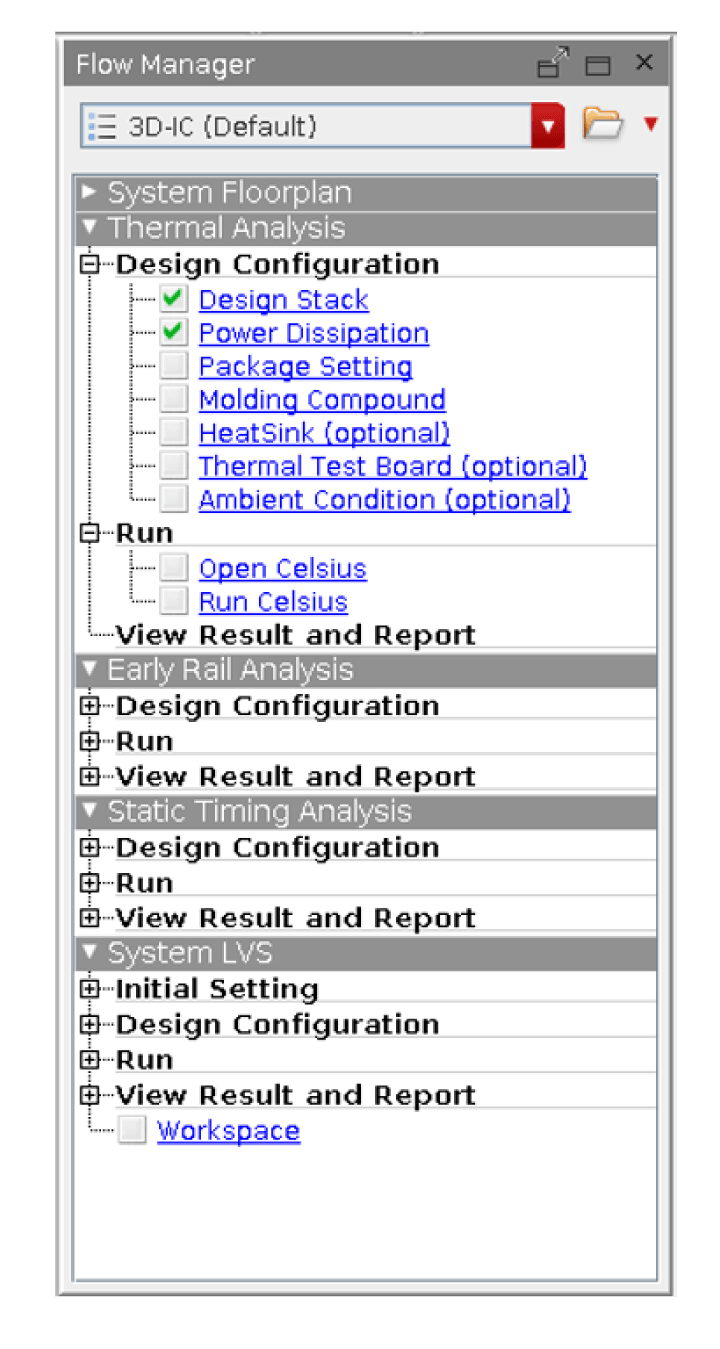

在构建三维(3D)系统时,早期签核分析是获取系统级反馈并在架构选择阶段进行设计修改的关键。 除了静态时序与功耗、电迁移、IR 压降分析及物理验证等标准分析外,堆叠芯片(stacked die)系统还需额外的签核检查,包括热分析以及针对翘曲问题的机械应力分析。Integrity 3D-IC(三维集成电路)提供了一款流程管理器,可引导用户完成与第三维度相关的各类分析设置。当系统布局规划完成且设计落 地后,该流程管理器中会呈现一份分析清单(见图 6)。

图 6:流程管理器

通过 Celsius 热求解器进行的热分析流程

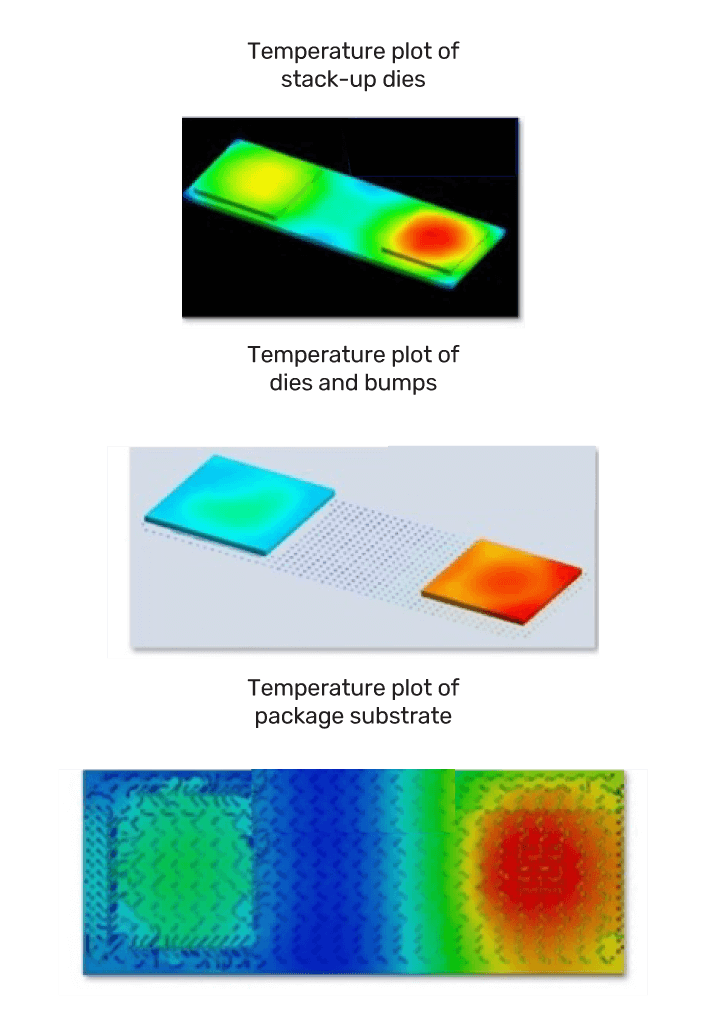

三维集成电路(3D-IC)设计的性能取决于其系统内各组件的热行为及温度分布。Cadence Celsius 热求解器环境支持热分析的各个方面,能够快速、准确地识别集成电路(IC)封装和印刷电路板(PCB) 中的热问题,包括堆叠芯片系统(见图 7)。该求解器包含一个功能强大的有限元分析(FEA)场求解器, 可用于分析复杂固体结构中的瞬态和稳态热传导;同时采用计算流体动力学(CFD)引擎,用于对流和辐射传热分析。其中,三维有限元分析(FEA)场求解器能为任意三维结构提供精准的热传导分析和电气仿真,例如带有凸点或键合线的复杂封装、连接器,以及连接器与印刷电路板(PCB)的过渡区域等结构。

图 7:热分析示例

使用 Voltus 解决方案进行的早期电源轨分析

为每个芯片供电并实现芯片间电流传输的电源传输网络(PDN),是三维集成电路(3D-IC)最重要 的组成部分之一。三维集成电路设计的性能在很大程度上取决于多芯片间的电源分配 / 分布情况及 IR 压 降效应。Integrity 3D-IC 具备对三维集成电路设计进行早期电源轨分析(ERA)的能力,可提供包含详细 设计信息与优化连接方案的多芯片堆叠数据(见图 8)。该工具采用了 Cadence Voltus 集成电路电源完 整性解决方案的核心功能 ——Voltus 是一款独立、支持云部署、覆盖全芯片和单元级的电源签核工具, 能对芯片的电源传输网络(PDN)或电源网格提供精准、快速且高容量的分析与优化技术。它还与 Cadence 的 Sigrity XtractIM 和 Sigrity PowerDC 技术深度集成,可实现芯片 – 封装 – 电路板的全流程电 源签核协同分析,支持 2.5D 硅中介层与 3D-IC 技术场景。

图 8:电源分配与分布设计

图 8:电源分配与分布设计

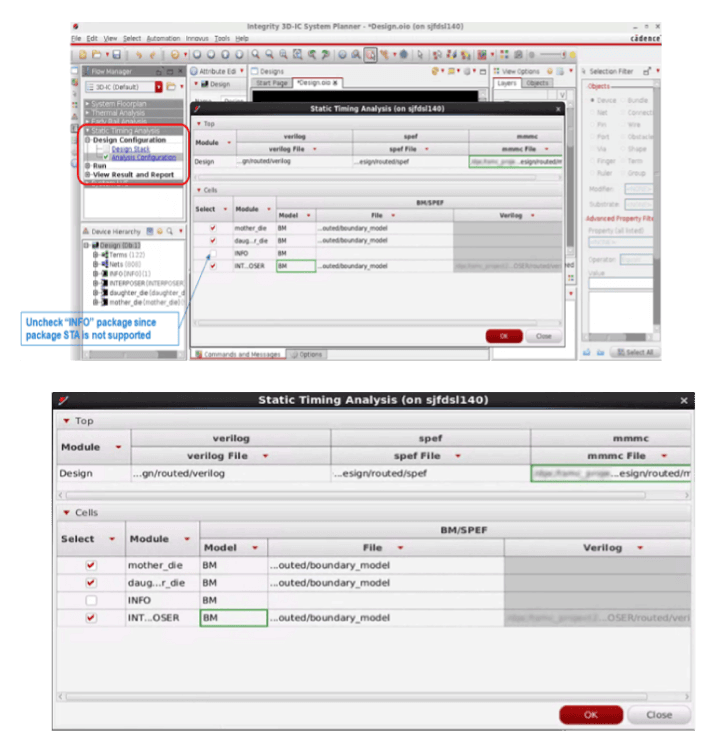

通过 Tempus 解决方案实现的多芯片静态时序分析流程

在采用多芯粒(chiplet)的设计中,对每颗芯片单独完成时序收敛,并对跨芯片的所有同步路径进 行时序分析至关重要。芯片直接堆叠虽能缩短互连长度,但也增加了三维堆叠结构(如硅通孔和微凸点) 的建模复杂度。Cadence 的 Quantus 提取解决方案已完成更新,可对所有三维结构进行建模,并利用标准 ICT 工艺文件和跨流程工艺文件生成多个标准寄生参数提取格式文件(SPEF)。当各芯片的单独规格 文件提取完成后,Cadence 的 Tempus 时序签核解决方案可凭借独特的分布式处理与云处理能力,提供 快速的多芯片静态时序分析(STA)功能(见图 9)。该 Tempus 解决方案能够将边界模型抽象用于芯 片内接口,并且原生支持对芯片间互连进行延迟计算。此外,堆叠芯片设计还需考虑各类工艺 RC 角点, 以确保全面覆盖工艺偏差,从而实现精准的时序分析。Tempus 解决方案采用专门技术用于芯片间路径 分析,并通过智能角点剪枝减少签核角点数量。经过精简的设计数据库与降低的角点复杂度,既能保证 分析结果的准确性,又不会牺牲设计性能,同时还能加快设计的时序收敛进程。

图 9:静态时序分析

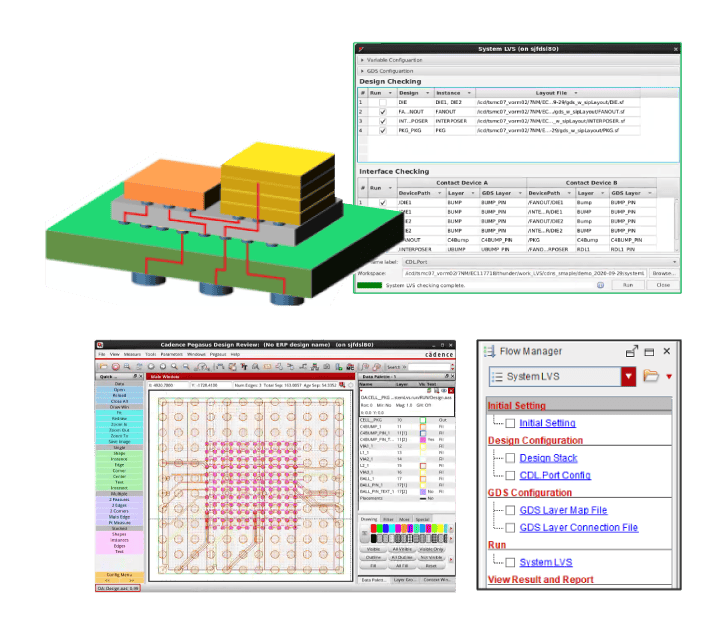

使用 Pegasus 物理验证进行的芯片间连接性与设 计规则检查(DRC)

在采用芯片堆叠或中介层的多芯粒系统中,存在关键的芯片间连接性检查与设计规则检查(DRC), 这些检查是设计收敛过程中必须完成的环节。Integrity 3D-IC 集成了 Cadence Pegasus 物理验证系统的灵活云部署平台,该平台能够在系统级实现无需规则文件(rule-deck free)的多芯粒连接性物理验证 (见图 10)。

图 10:物理验证示例

Pegasus 物理验证工具可通过图形用户界面(GUI)驱动的交互界面,利用自动生成的数据检查凸点对准情况与系统级连接性,且内置交互式 GDS 查看器。Integrity 3D-IC 与 Pegasus 物理验证工具之间的原生集成,确保了三维设计流程中物理验证的准确性,且无需依赖第三方工具。

Cadence 服务与支持

➢ Cadence 应用工程师可通过电话、电子邮件或互联网解答您的技术问题,还能提供技术支持与 定制化培训服务。

➢ 由 Cadence 认证讲师授课的课程超过 70 门,这些讲师会将自身的实际工程经验融入课堂教学。

➢ 30 多门互联网学习系列(iLS)在线课程为您提供灵活选择,您可通过互联网在自己的电脑上 完成培训。

➢ Cadence 在线支持(Cadence Online Support)为您提供全天候(24×7)在线服务,您可随时 访问包含最新解决方案、技术文档、快速应用套件(Rapid Adoption Kits)、软件下载等资源 的知识库。 \

➢ 如需了解更多信息,请访问支持(support)与培训(training)相关页面。