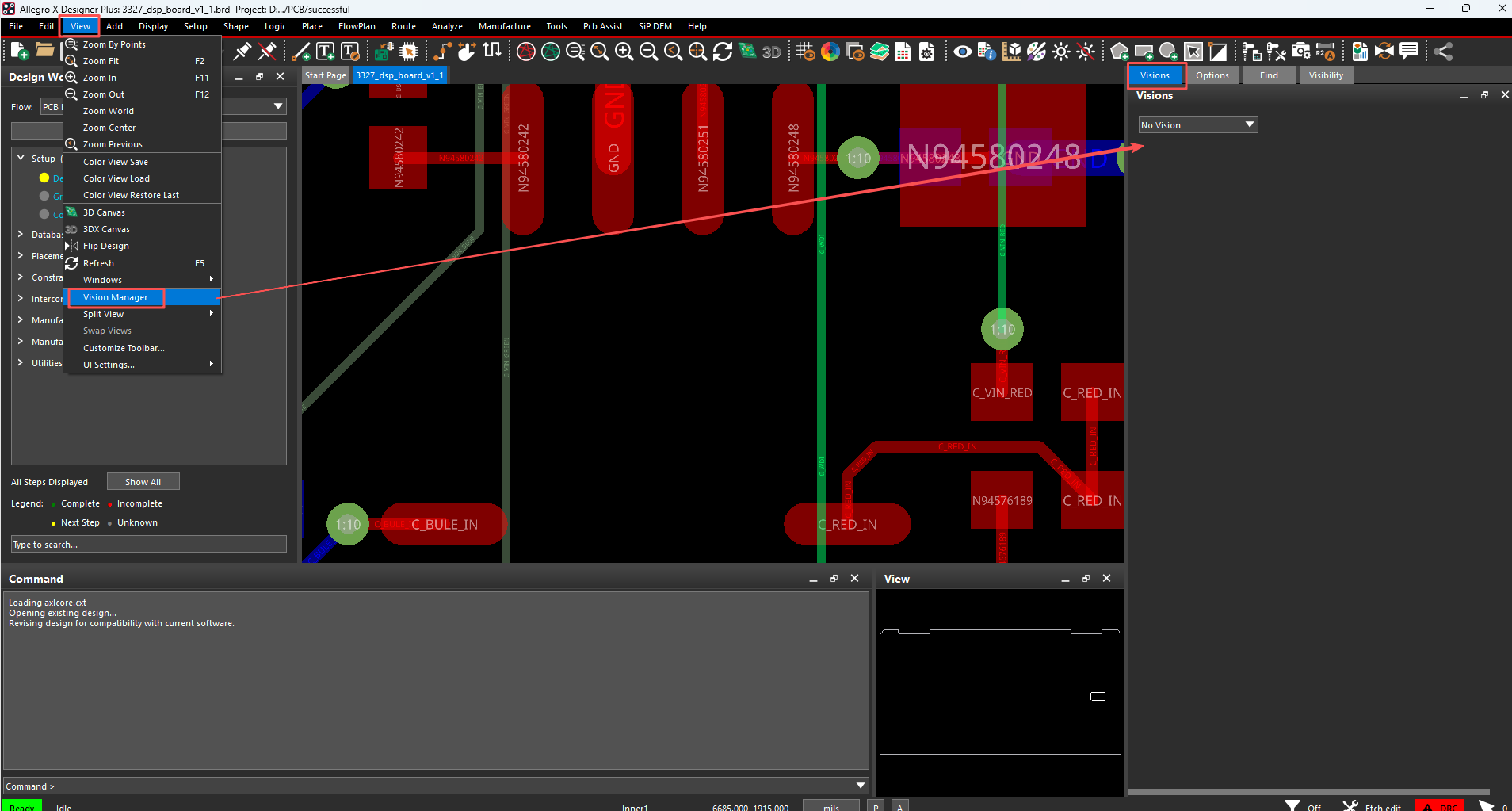

2.点击View-Vision Manager,打开Visions窗口界面。

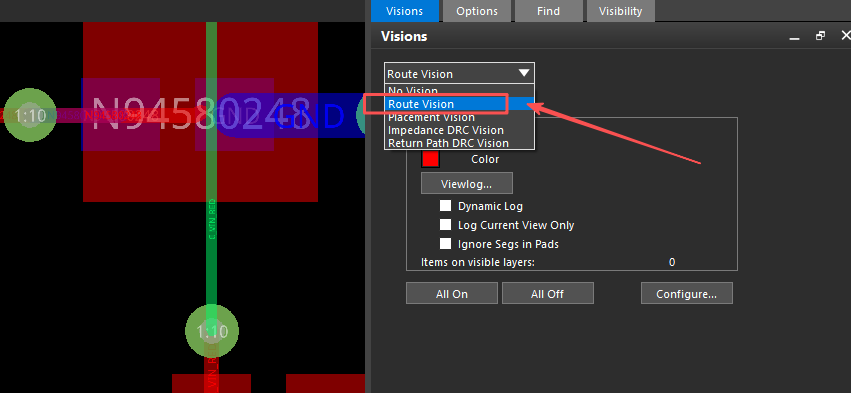

3.在Vision窗口界面下拉选择Route Vision,启用布线配置。

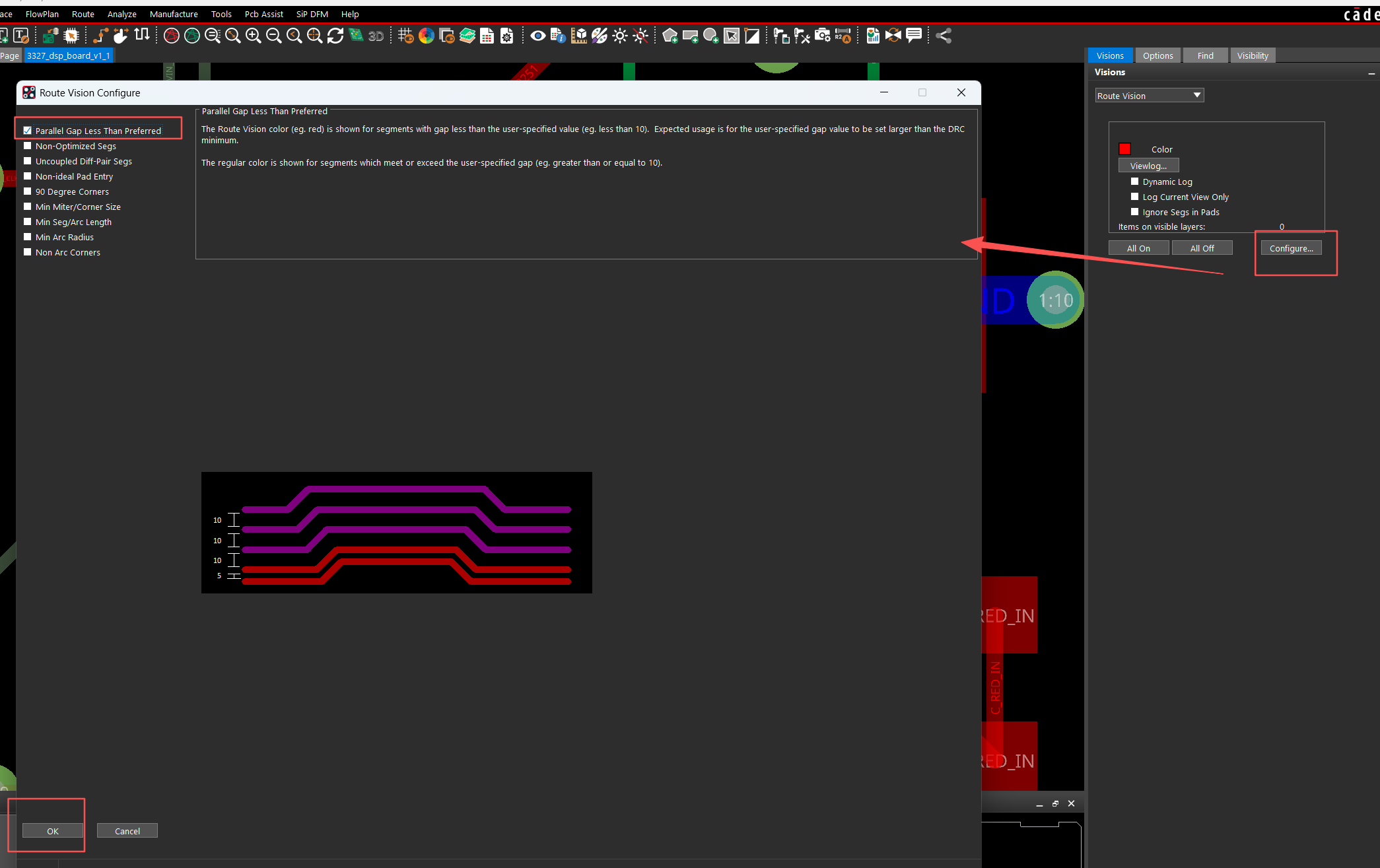

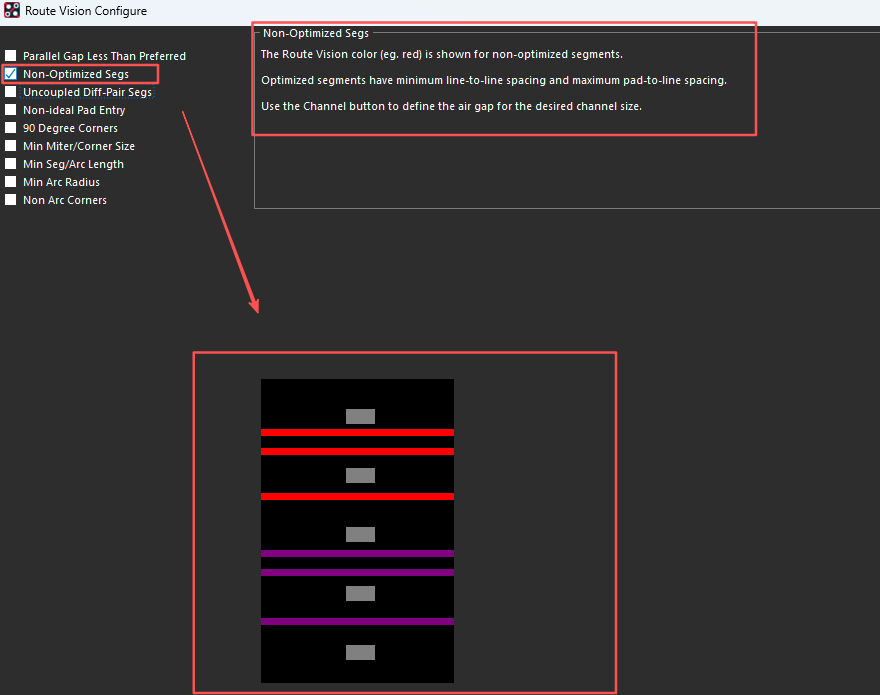

4.点击Configure进行配置,仅勾选(平行间隙小于标准值),当鼠标悬停在勾选对话框时,在界面下方会展示该选项的说明以及相关的图表。

5.选择ok进行配置。

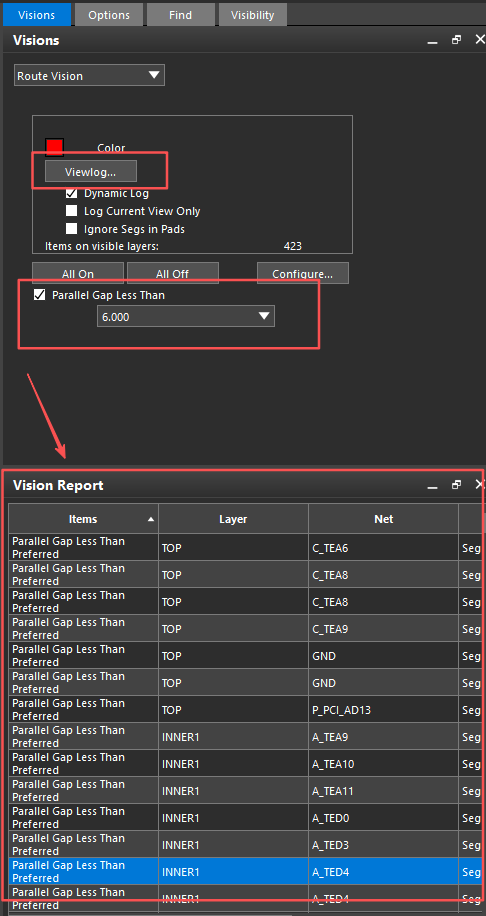

6.回到Visions界面,勾选Dynamic Log,可查看不满足布线要求的值

7.勾选Parallel Gap Less Than并设置平行线之间的标准值为6mil。

8.点击Viewlog,接着在下方的Vision Report界面就可以查看平行线之间的距离小于标准值的层以及网络的报告,双击报告中的某一项内容,allegro会自动定位到未满足距离要求的走线上。

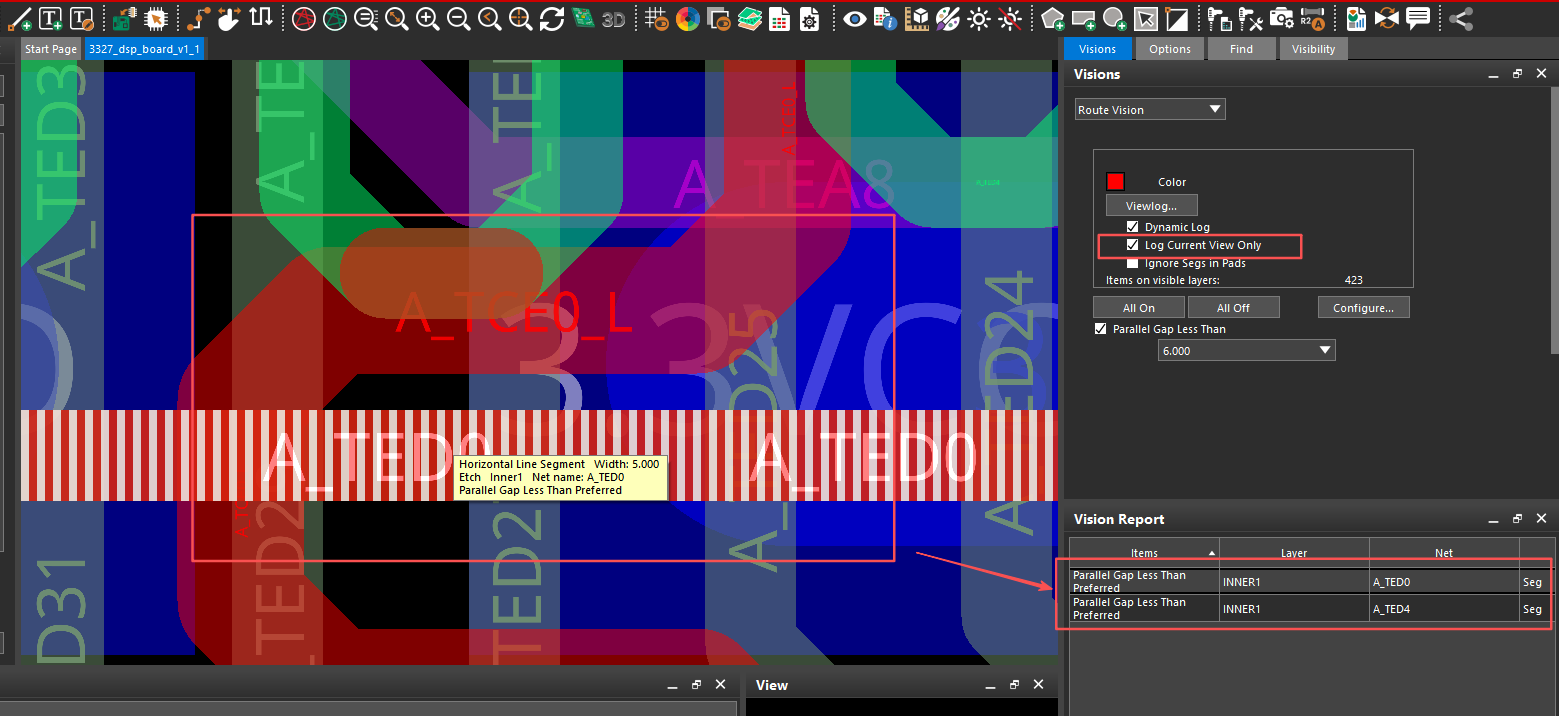

9.在Visions界面勾选Log Current View Only,当在Allegro的布线界面进行缩放操作时,Vision Report会迅速缩减为仅包含在视图中显示的区域的项目,更好的对布线进行局部优化;当我们在视图中对于布线进行优化完成后,走线将由红色恢复为正常走线颜色,同时动态日志也会自动更新。

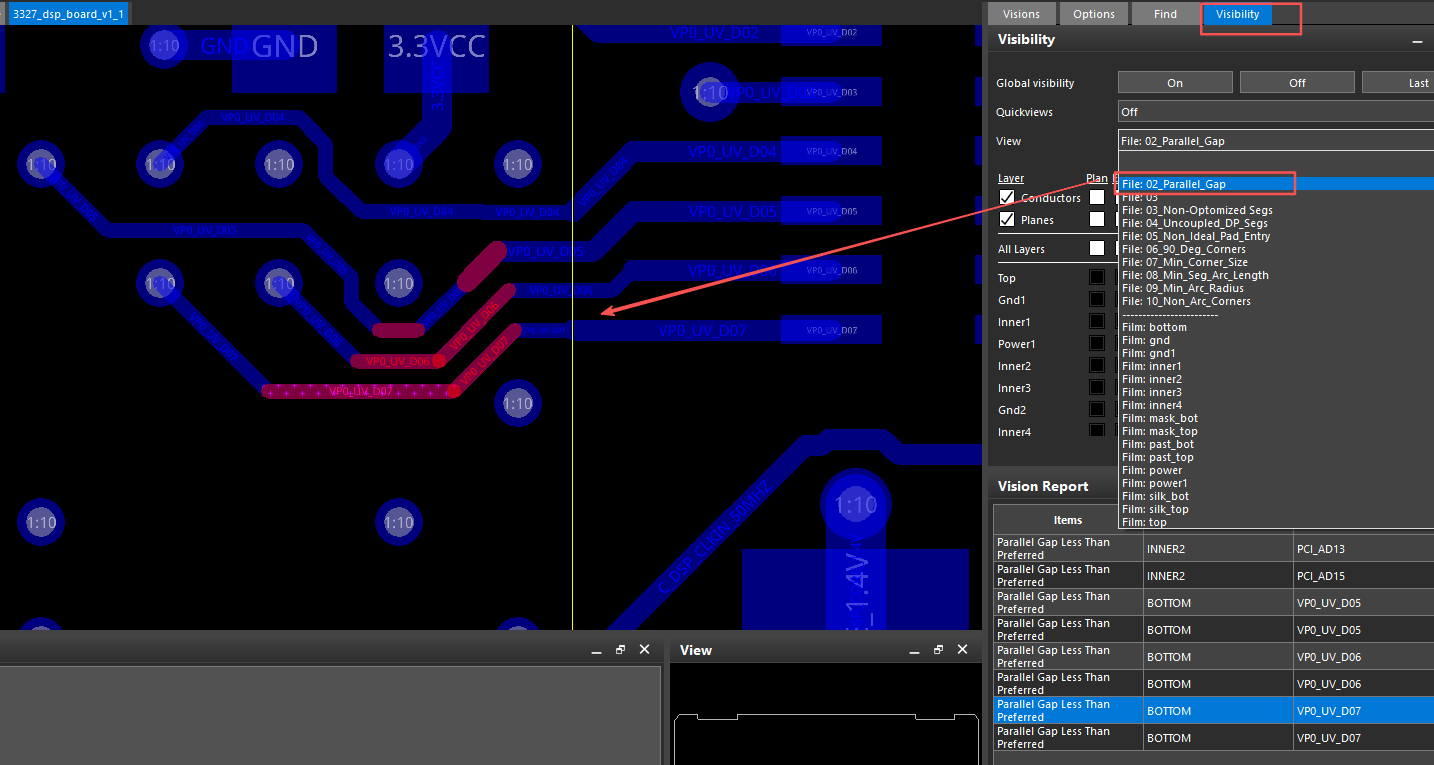

10.也可以来到Visibilityjiamian ,在view对话框下拉选择File:02_Parallel_Gap,也可以实现快速定位。

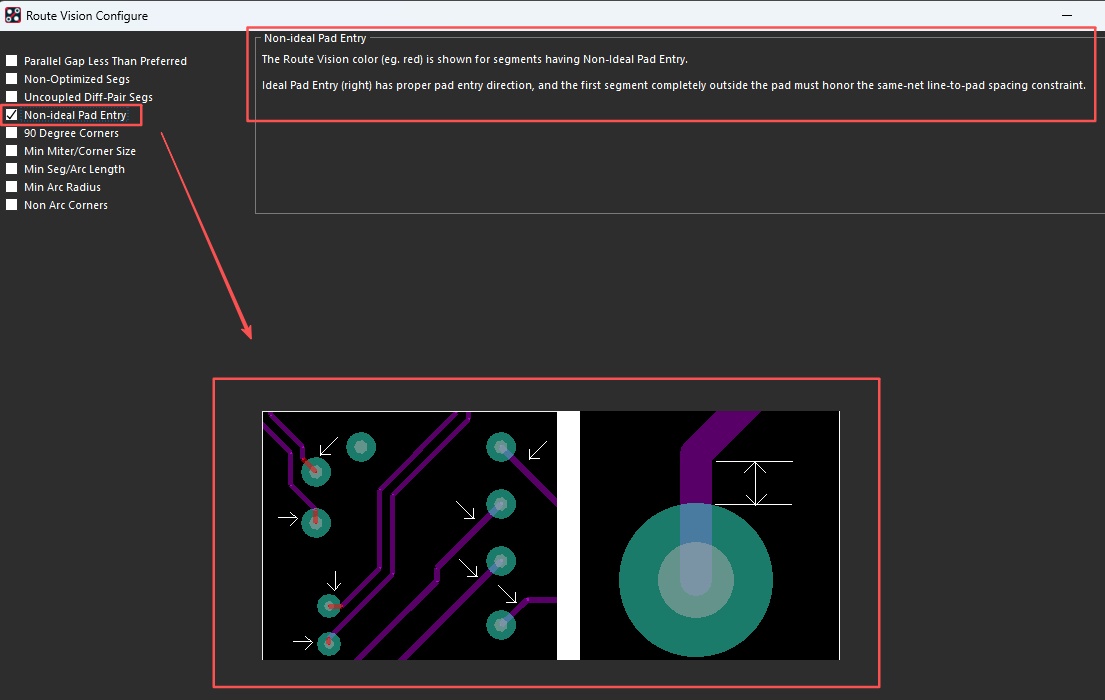

3.Non-ideal Pad Entry:检查同一网线与引脚之间的间距,以确保在转弯前各段能正确地从引脚处伸出。

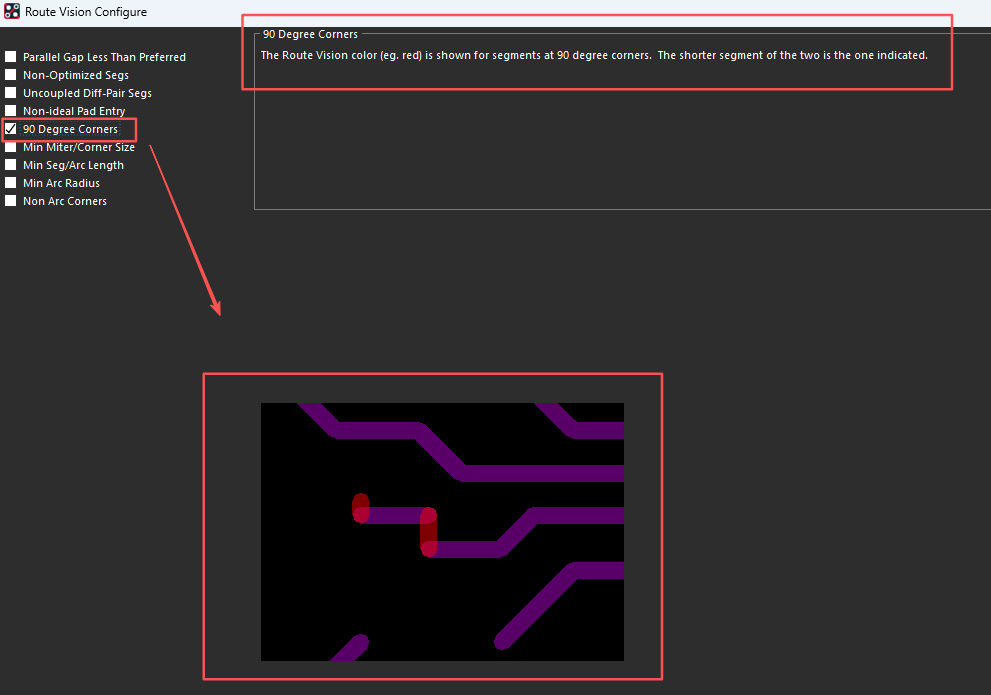

4.90 Degree Corners:识别出那些在设计中通常不被接受的90度拐角。

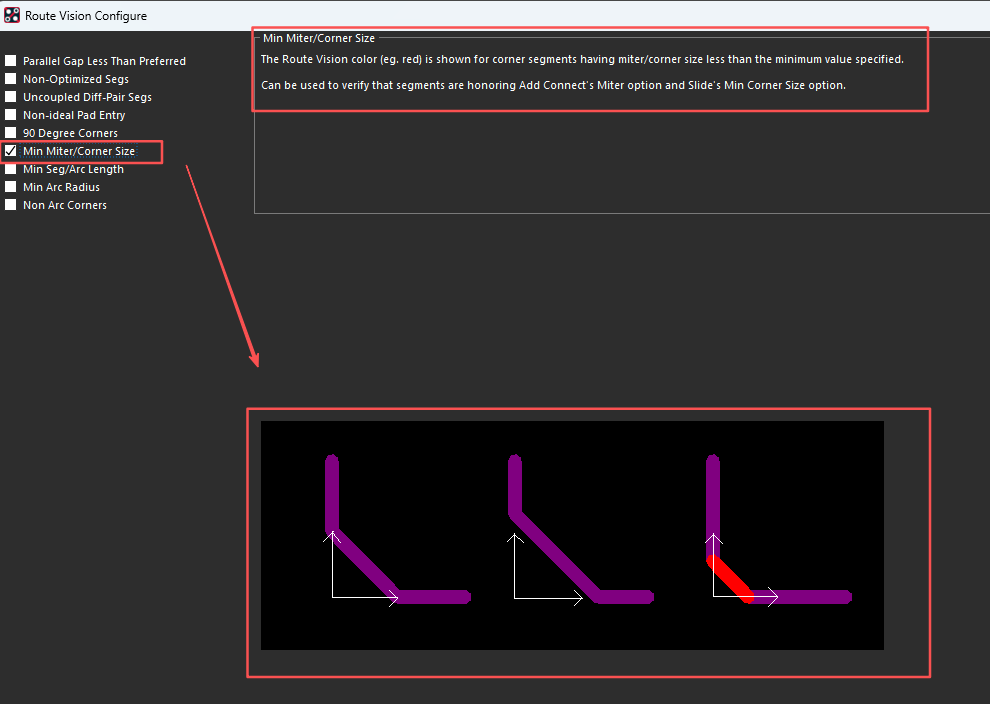

5.Min Miter/Corner Size:用于确定低于设定参数的转角位置,验证走线中的斜坡/管脚是否满足要求。

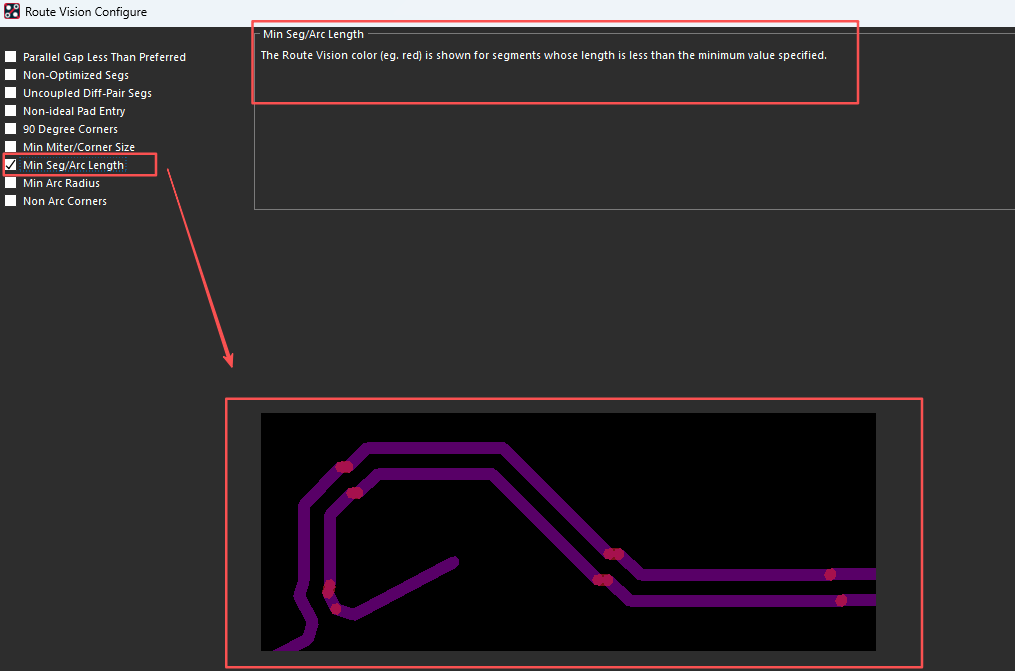

6.Min Seg/Arc Length:突出显示低于设定参数的分段或弧形部分。

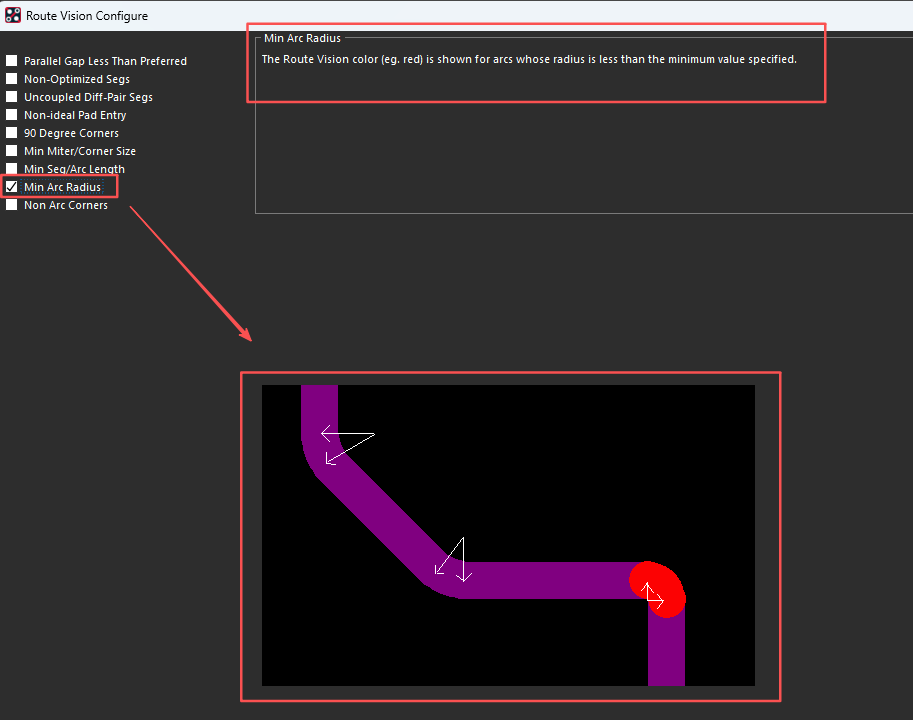

7.Min Arc Radius:找出任何低于设定参数的弧线。

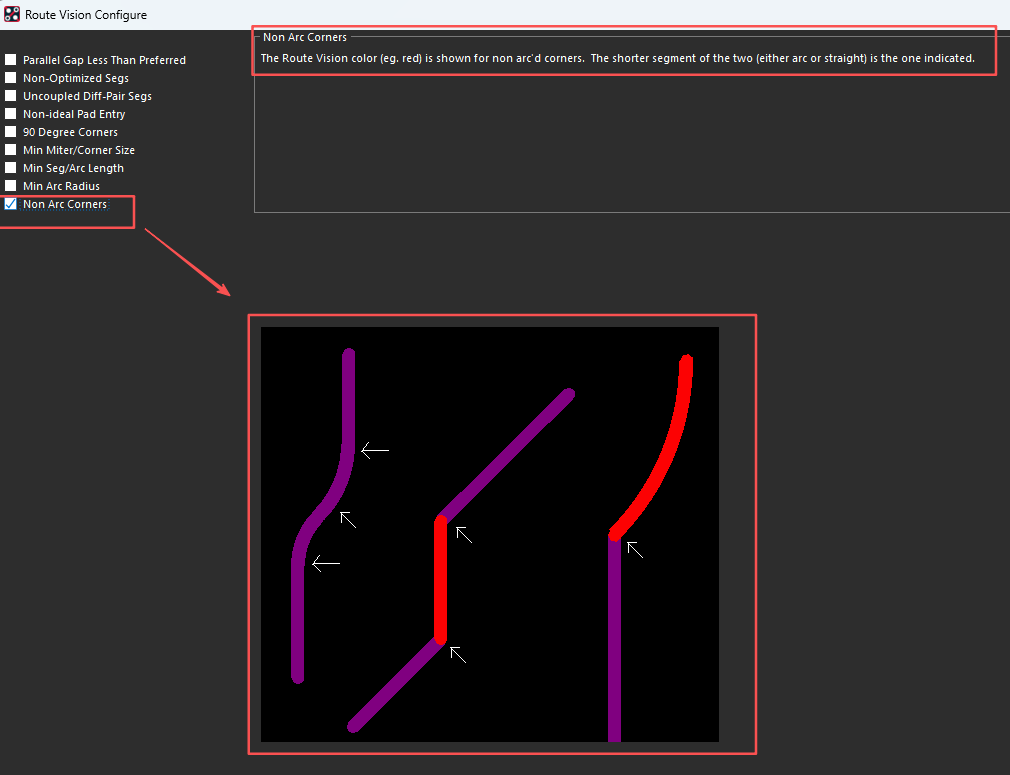

8.Non Arc Corners:用于查找任何非弧形的拐角或弧形部分。

Allegro X Design Platform

Cadence Allegro X Design Platform 是一个强大且统一的系统设计解决方案,为协作式的团队工作环境提供支持,满足前沿、现代的电子设计需求。无论是错综复杂、技术要求严格的系统,还是普通的电路要求,该平台都可以轻松应对。它提供了一个集成的生态系统,包括原理图设计、PCB layout 和设计同步分析(In-Design Analysis,IDA),由集中管理的可视化设计数据提供支持,有效避免了不必要的设计冲突和错误。