上期我们介绍了如何使用cadence Allegro的规则“约束”孔,实现一键式快速生成孔;本期我们将教会大家如何利用约束管理器去约束我们的走线。?

2.对于高速差分信号,每一对差分线必须保证严格的等长,否则信号质量会急剧恶化。

3.多通道高速串行链路之间最好也做一定的等长约束,避免不同的数据包信号到达时间相差太远,影响性能。精准地使用等长约束,才是资深打工人的体现,既能保证板子一次成功,又不会把自己累死在无关紧要的细节上!?

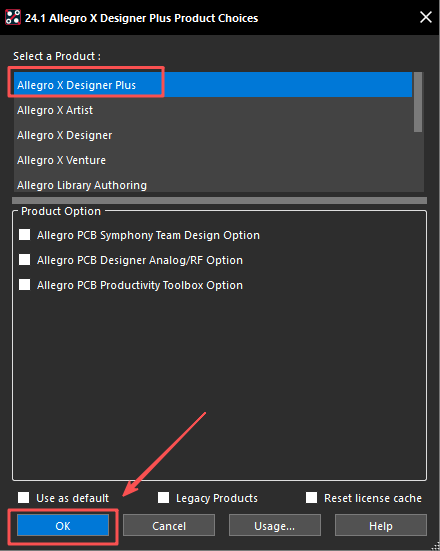

2、cadence软件配置:Allegro X Designer Plus 24.1-2024 P001 [9/4/2024] Windows SPB 64-bit EditionEdition

走线约束设置

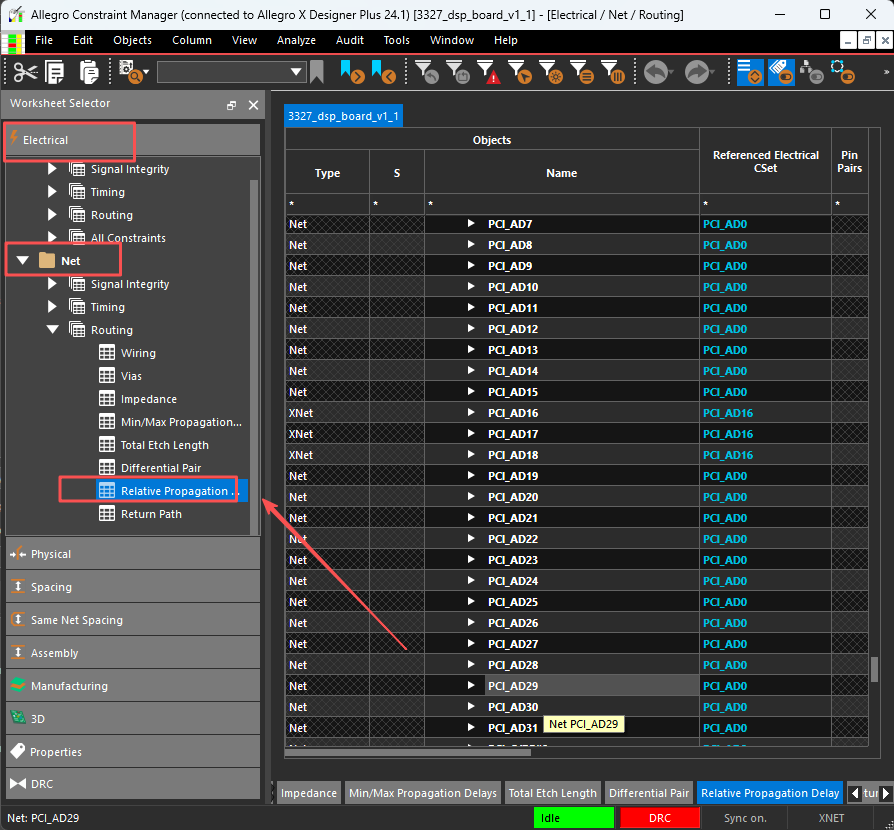

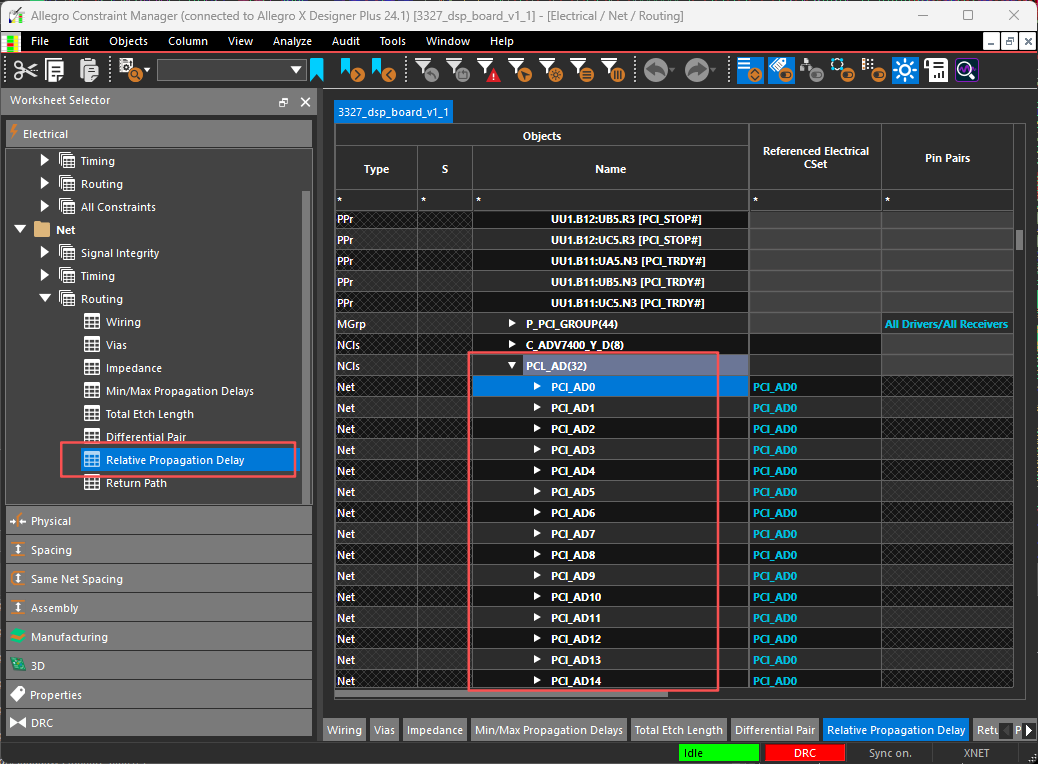

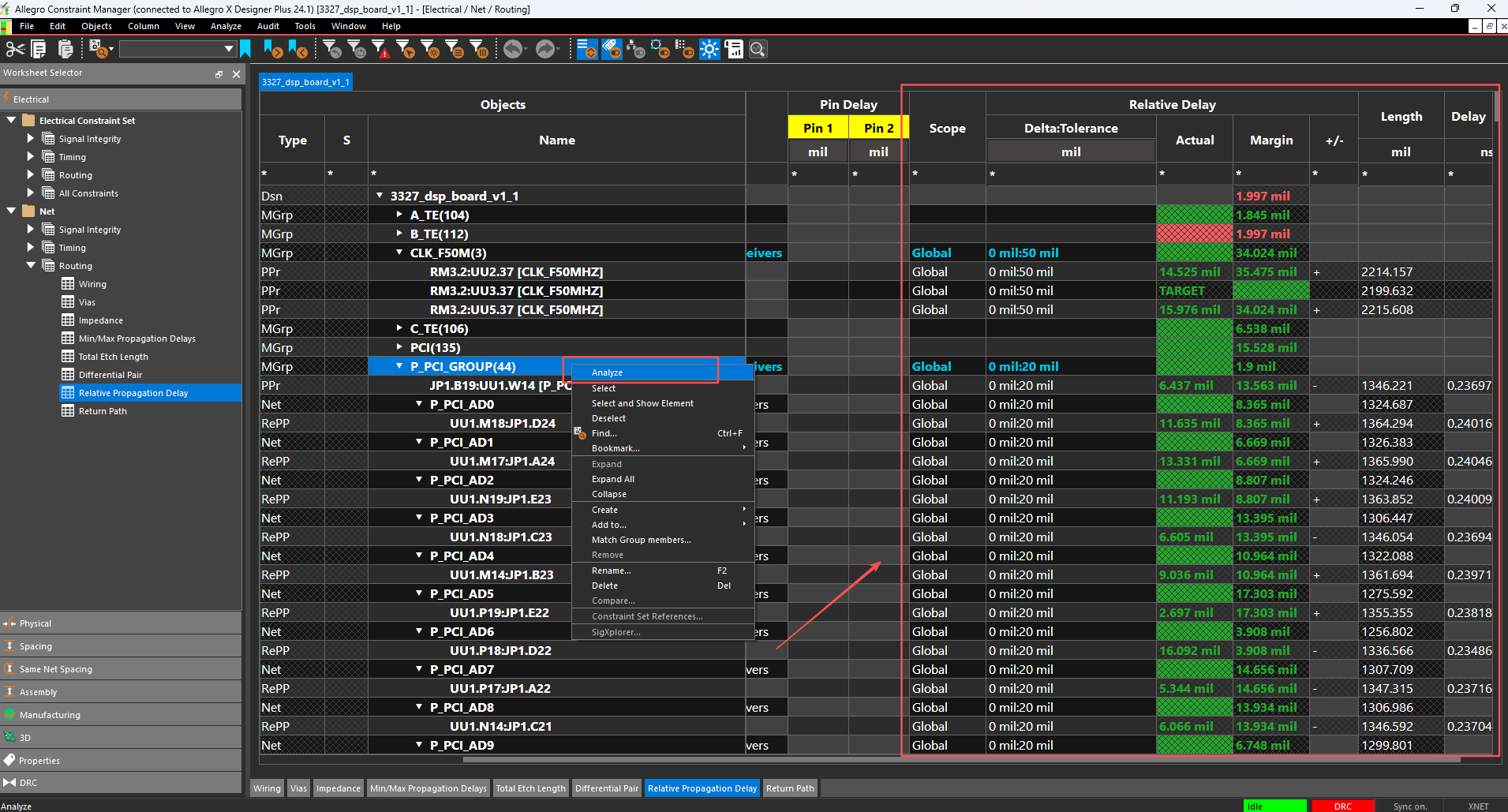

2.打开规则约束管理器,点击选择Setup-Constraints-Electrical,在窗口中选择Net-Routing-Relative Propagation Delay,查看走线约束。

3.网络组(NCls)对象包含32个成员,可在顶级的网络组对象中创建并应用约束,通过此方式创建的约束可应用到网络组的所有成员中。展开可查看该网络组的所有的网络名称。

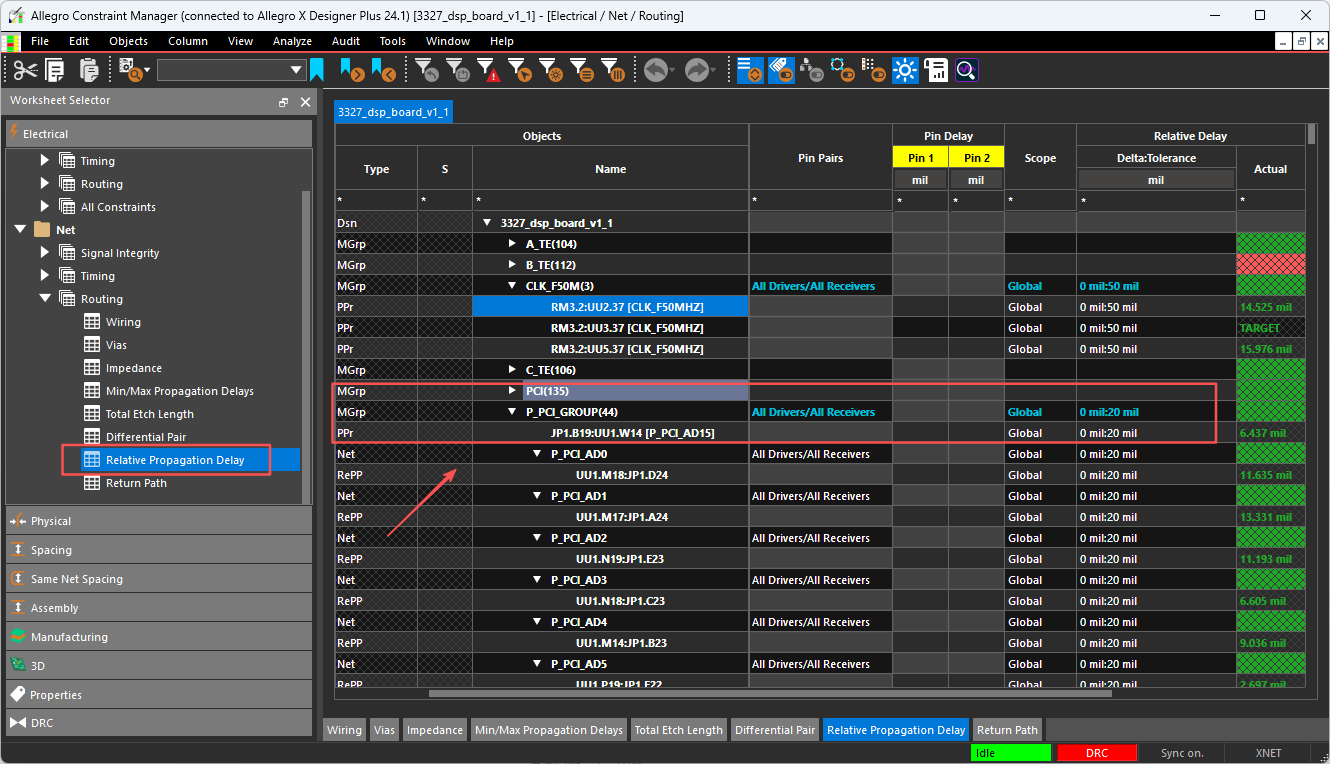

4.下图为一个相对等长规则约束,它包含了一个驱动引脚(UU1.M18)和一个接收引脚(JP1.D24).其中Scope=Global表示此约束适用于所有对象;Delta:Tolerance=0mil:20mil表示所有类似引脚对都需要按照目标引脚对的长度进行布线,误差范围控制在+/-20mil之内。

5.规则约束管理器通过内置的场求解器来管理和分析电气规则。鼠标右键点击一个网络组选择Analyze。在相对延迟中的红色数值代表该网络与指定的长度偏差超过了20mil;绿色数值则代表为安全范围内的值。

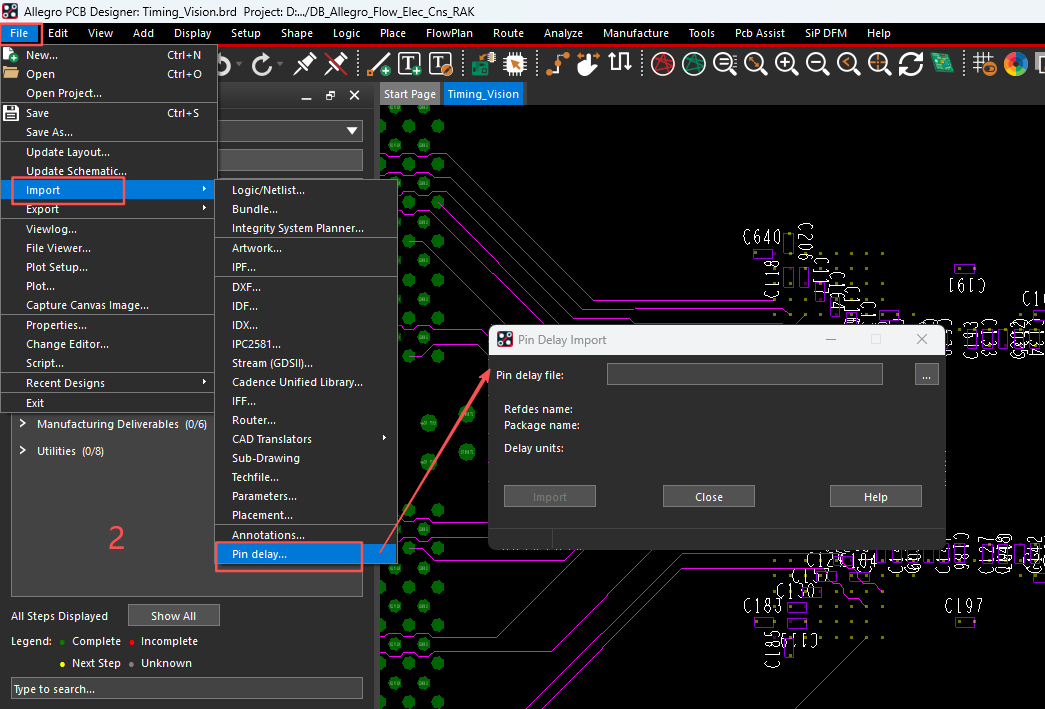

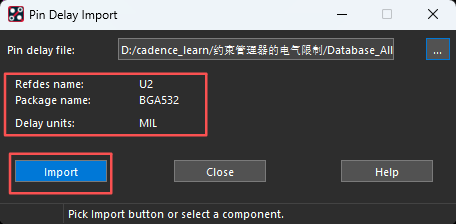

2.选择菜单栏的File-Import-Pin Delay。打开Pin Delay Import界面。

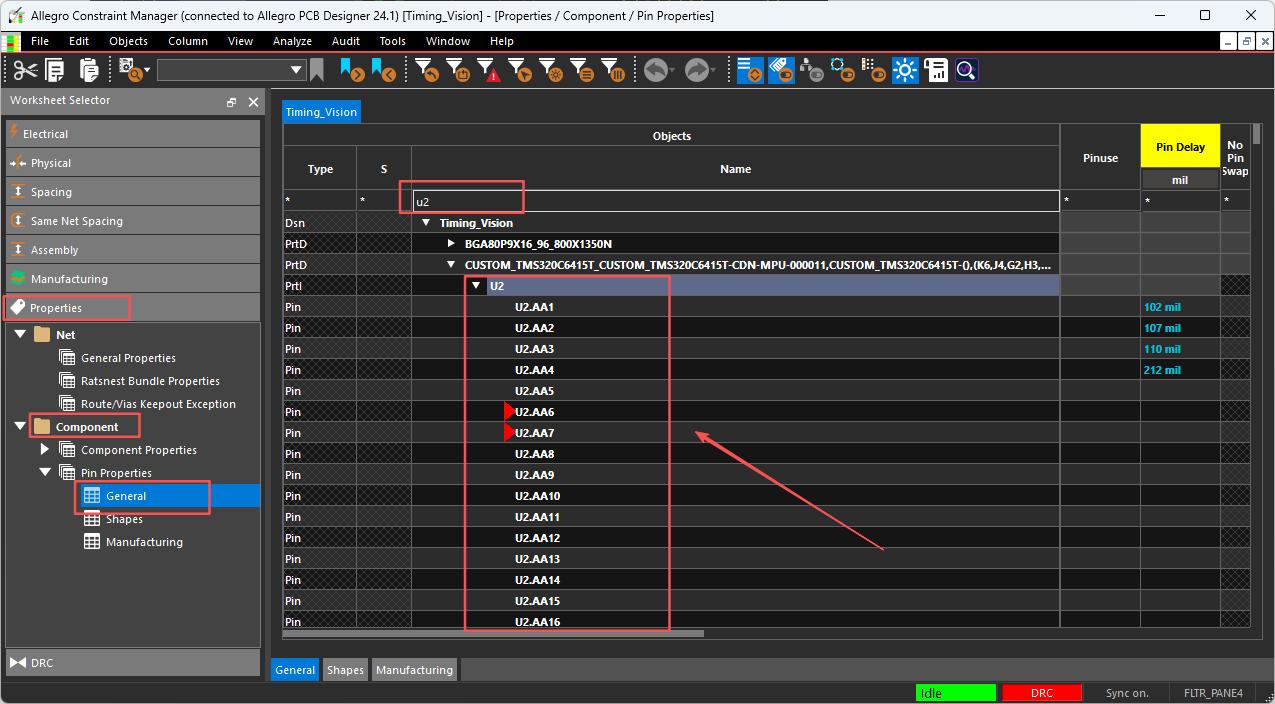

5.在Objects输入位号u2进行筛选,展开筛选结果,可以看到Pin Delay已按表格进行了映射,在表格中也支持手动修改Pin 延迟值。

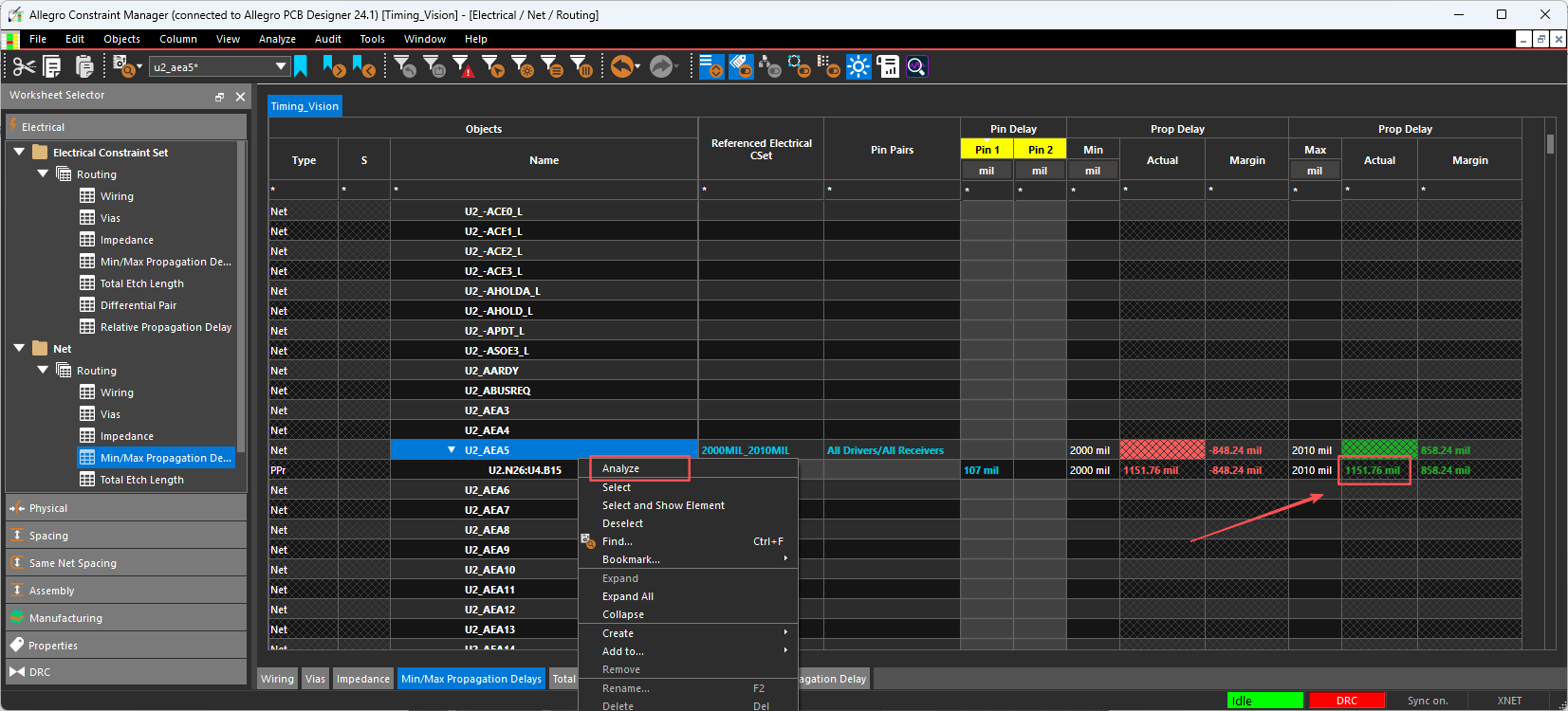

6.接着,我们可以查看增加了Pin Delay对于网络延迟的影响,首先查看未添加引脚延迟时的实际传播延迟为:1151.76mil。

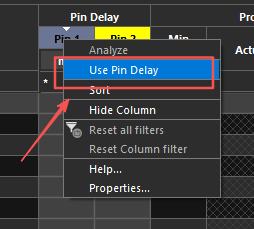

7.接着使用引脚延迟,点击引脚延迟数值107mil,再Pin1显示的颜色变为灰色时,鼠标右键点击Pin1选择Use Pin Delay,将引脚延迟也添加到传播延迟中。

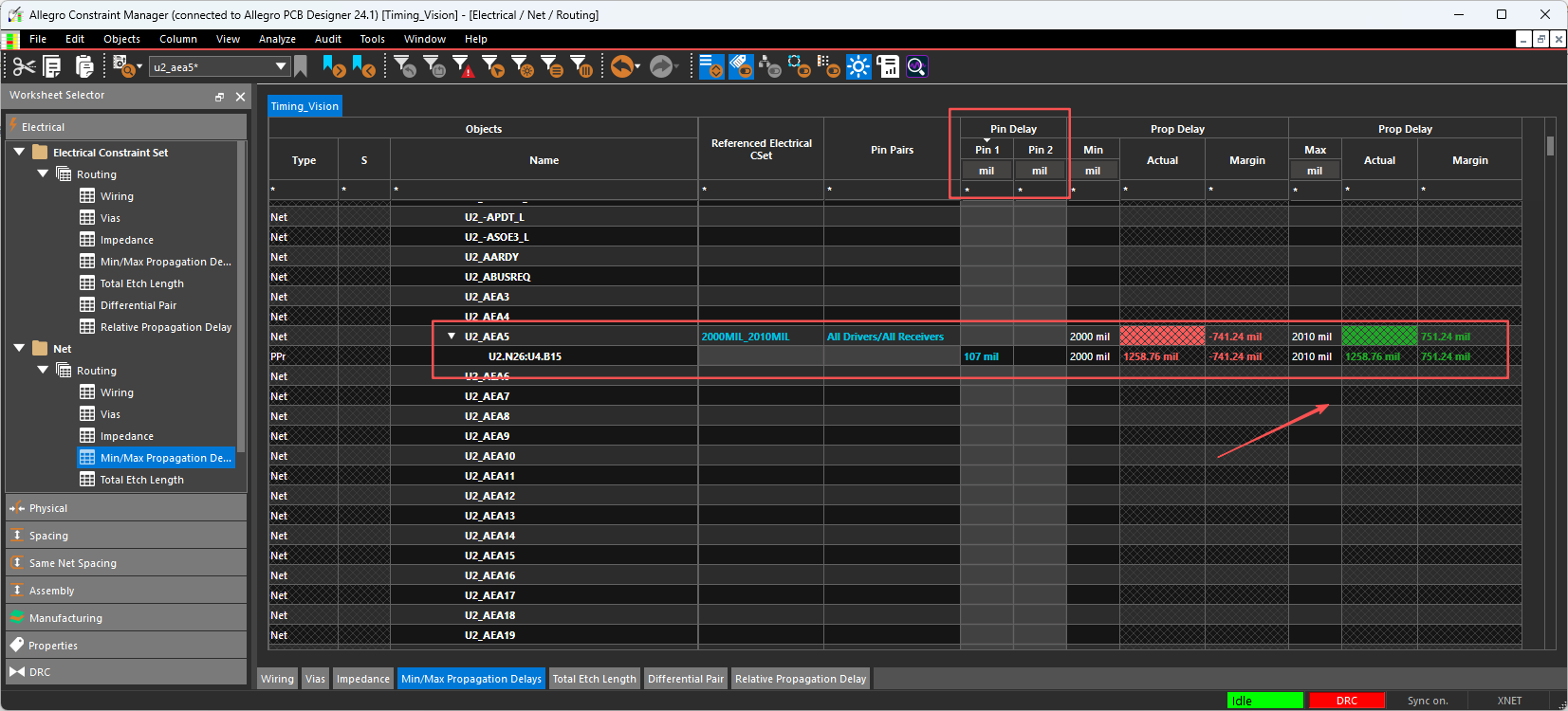

8.此时的Pin Delay无颜色标识,增加了引脚延迟后的实际传播延迟值为:1258.76mil。最大实际延迟以绿色显示,表明该值小于2010mil的约束值。

本期主要介绍了Allegro中的走线的约束以及引脚延迟的具体约束方法,下一期我们将为大家呈现PCB走线的优化,让大家布线更加美观!期待大家的在看与分享~?