业界首发!Cadence 宣布推出性能领先的 22Gbps GDDR6 IP 并在 TSMC N5 工艺上通过硅验证

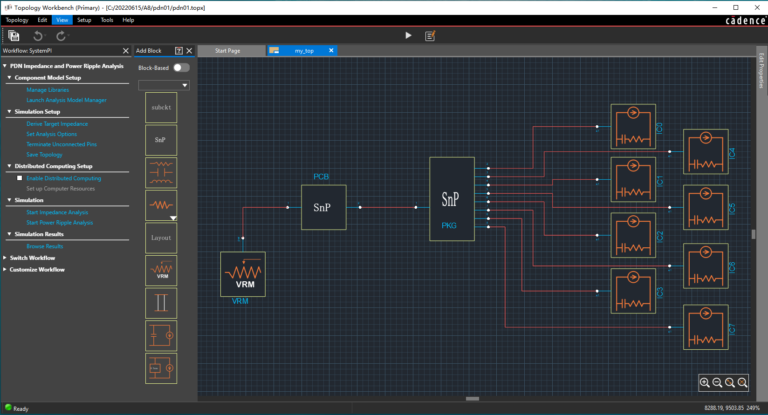

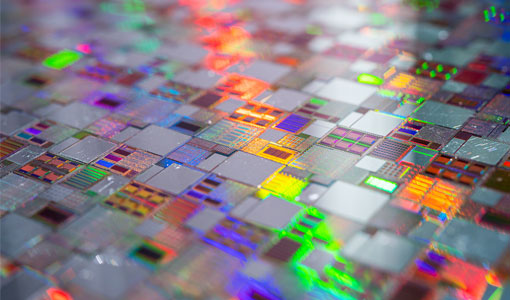

楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布,Cadence® GDDR6 IP 在 TSMC N5 工艺节点上顺利通过硅验证,性能超越 Cadence 上一代 16Gbps 设计。GDDR6 IP 包括 Cadence PHY 和控制器 Design IP 以及验证 IP(VIP),专门针对超高带宽的存储器应用,如超大规模计算、5G 通信、汽车和消费电子。GDDR6 特