Allegro高级教程之差分对设计约束管理

对于一些复杂的电路板设计,特别是对高速数字电路来说,信号完整性问题是工程师越来越关注的问题,解决信号完整性问题的方法之一就是采用信号差分传输方式,在PCB设计中即采用差分对走线。随着高速电路传输速度的不断提高,信号差分传输方式必将得到越来越广泛的应用。本文就Allegro中的差分对设计做一个系统的介绍。关键字:Cade

对于一些复杂的电路板设计,特别是对高速数字电路来说,信号完整性问题是工程师越来越关注的问题,解决信号完整性问题的方法之一就是采用信号差分传输方式,在PCB设计中即采用差分对走线。随着高速电路传输速度的不断提高,信号差分传输方式必将得到越来越广泛的应用。本文就Allegro中的差分对设计做一个系统的介绍。关键字:Cade

AllegroPCBDesigner具备完善的约束驱动管理系统,可以进行约束的创建、管理和验证。PCB设计中所要遵循的规则约束统一在约束管理器(ConstraintManager)中设定。本文主要对通用规则约束的设定进行介绍,包括物理规则、间距规则和其它一些设计规则。关键字:AllegroPCB、Allegro教程、Cadence教程、设计规则、创建规则、规则设置、

在进行PCB设计时,用户可以对设计环境进行定制,Allegro为用户提供了多种环境定制及文件管理功能,以提高PCB的设计效率。例如通过定制鼠标的Stroke功能来快速执行某条命令,根据用户习惯自定义快捷键,在PCB设计中录制脚本等,还可以导入/导出多种文件格式,供其它设计人员共用。利用Allegro的这种快速有效的环境定制优化及文件管理

焊盘和封装是PCB设计的基本组成元素,Allegro提供了多种焊盘和封装形式供用户选择,在〈安装盘符:〉CadenceSPB_16.5sharepcbpcb_libsymbols库中。除了直接调用这些焊盘和封装外,用户还可以自定义封装和焊盘,以适应不同PCB板的设计。本文主要介绍在AllegroPCB中,如何制作焊盘和封装库。关键字:AllegroPCB、Allegro教程、

Backdrill是指删除电路板上多余通孔的生产工艺。对于多层电路板,PCB走线从其中两层进行(除了顶层到底层的走线),就会出现通孔中含有未被使用的部分(ExtraVias),Backdrill中称为Stub。如图1所示。尤其对于高速PCB设计,Stub对信号质量的影响就尤为明显。目前消除通孔对信号质量的影响有两种方法,一是布线过程中使用盲埋孔进行布

DFA(DesignForAssembly)称为装配设计,是指通过对电子产品进行装配分析,制定出合理的元件装配规则,从而提高设计效率、减少生产成本的设计方法。AllegroPCBEditor提供了布局过程中实时的封装-封装的间距检查,分为sidetoside、sidetoend、endtoend、endtoside四种检查模式。对于复杂的电路板,实时的DFA间距检查与分析有助于提高

PSpice为用户提供了模型转换与编辑工具:ModelEditor,用户自己下载的模型参数文件可以通过ModelEditor转换成PSpice的模型文件,并且可以建立相应的模型符号。本文以intersil公司的ISL28114元件模型为例介绍如何将下载的Spice模型文件导入到PSpice模型库中,并对模型进行模拟仿真。一个完整的模型创建与应用实例包括以下几步:1、

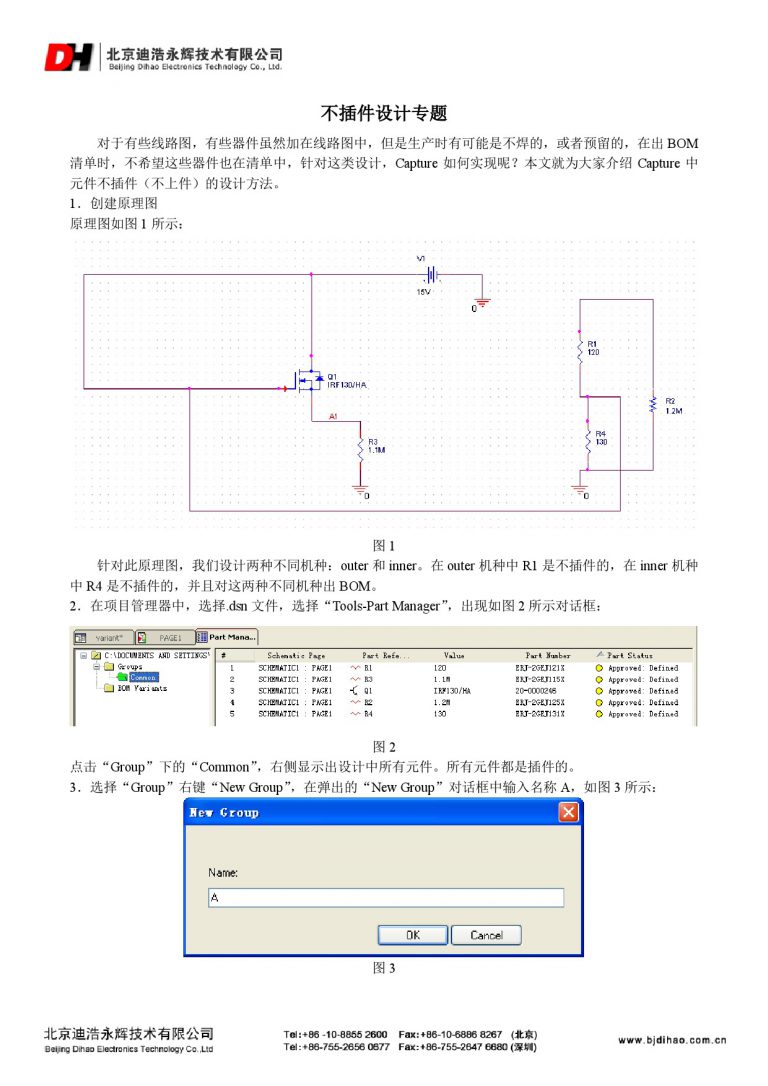

对于有些线路图,虽然有些器件加在线路图中,但是生产时有可能是不焊的,或者预留的,在出BOM清单时,不希望这些器件也在清单中,针对这类设计,Capture如何实现呢?本文就为大家介绍Capture中对于不同机种元件不插件(不上件)的设计方法。关键字:OrCADCapture、OrCAD教程、不插件、不上件、variantBOM元件预留

Cadence为用户提供了加载菜单命令的强大功能,用户可以自己编制新命令,加载到软件中,还可以将新命令加载到Allegro的菜单中。本文以新增文字重叠检查(check_silk)为例,介绍如何加载新的命令,并且将新命令添加到“Manufacture”菜单下:关键字:AllegroPCB、Allegro教程、loadnewskill、加载命令、创建新命令

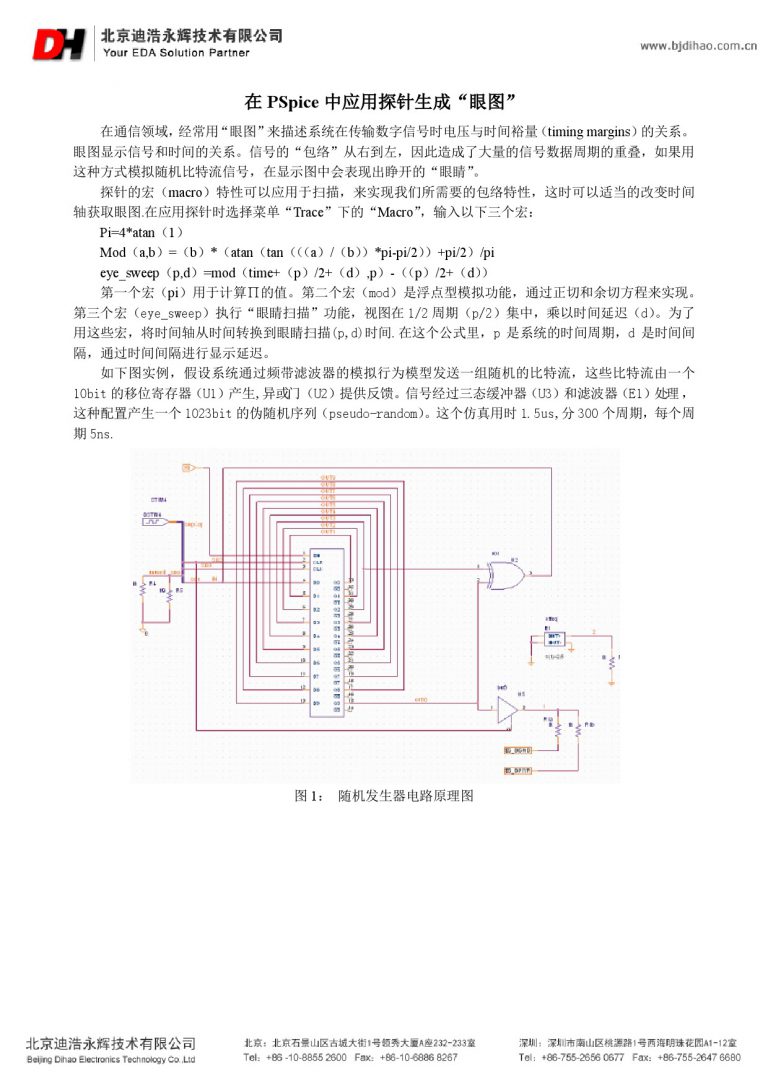

在通信领域,经常用“眼图”来描述系统在传输数字信号时电压与时间裕量(timingmargins)的关系。本文介绍在PSpice中如何应用探针生成眼图,并比较一个数据周期和两个数据周期下眼图的形状。

本文主要介绍在PSpice中采用模拟行为建模对非线性电容器的两种建模方法:查表建模法和多项式建模法。查表建模法通过非线性电容的电容-电压曲线进行建模;多项式建模法依据电容是电压的二次方程进行建模。建模完成后通过瞬态分析对模型进行验证。