What’s new in PSpice A/D 16.6

OrCADPSpice16.6通过改善模拟集合和平均提高20%模拟速度,从而提高用户的生产率。通过引入多核模拟支持系统,包括大型设计和MOSFETs和BJTs等复杂模型支配的设计,取得了显著的性能提高。

OrCADPSpice16.6通过改善模拟集合和平均提高20%模拟速度,从而提高用户的生产率。通过引入多核模拟支持系统,包括大型设计和MOSFETs和BJTs等复杂模型支配的设计,取得了显著的性能提高。

OrcadCaptureCIS/AllegroDesignEntryCIS16.6新增功能列表,如下,具体内容及相关操作见技术白皮书。1.在Capture下运行SigXplorer进行信号完整性分析2.从菜单中放置PSpice元件3.配置菜单和工具栏4.设计和库文件保存功能的扩展5.查找功能的扩展6.NetGroup使用模型的升级7.查询并替换Off-PageConnector(端口连接符)8.Cache更新扩

What’sNewAllegro/OrcadPCB16.6列出了此版本最新增加的功能及改善的功能,同时对之前版本所出现的软件问题修复,做了详细说明

Cadence公司的OrCAD®®PCB设计技术包括一个完整的,具有成本效益的PCB设计解决方案,从设计输入到最终输出。为了成功地实现项目目标,PCB设计师和电气工程师需要能够在整个PCB设计流程无缝强大,直观和集成技术。的OrCADPCB设计技术提供了完全集成的前端设计,模拟/信号完整性仿真,以及布局和布线的提高生产力,缩短产品上市时间的

高速PCB板布线过程中,经常遇到等长设置问题,例如DDR的一组数据线和地址线,但是由于数据线和地址线中间有一个电阻(或排阻),这种情况下设置等长就要引入Xnet的概念,通过设置Xnet的等长来确保数据线和地址线的等长。由无源、分立器件(电阻、电容、电感)连接起来的几段网络的组合称为Xnet,如图:本文介绍在Allegro中如何创建一组

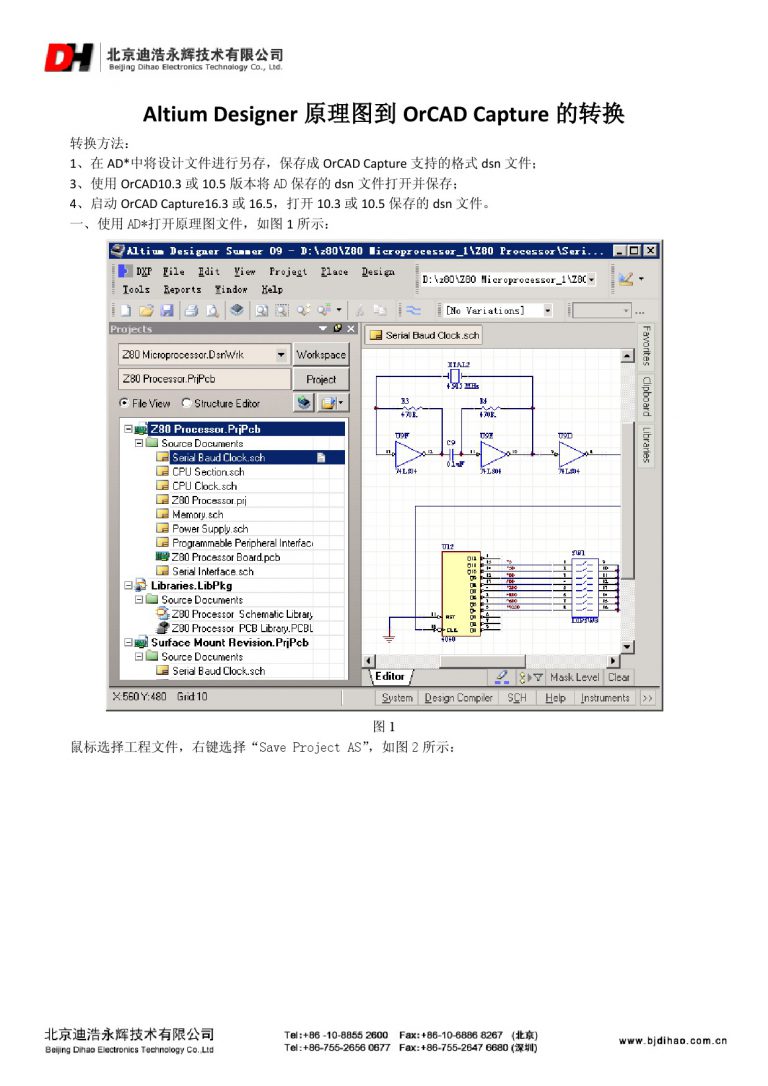

目前,越来越多的设计团队选择采用Cadence工具作为开发平台,那么之前使用AltiumDesigner进行设计的项目,如何转换到Cadence工具中,成为工程师面临的一个问题。文本就AltiumDesigner原理图到OrCAD的转换进行系统的介绍。

Allegro允许用户进行多种类型尺寸的标注,例如线性标注、角度标注、直径/半径标注、元件次序标注等。本文就Allegro的尺寸标注环境做系统介绍。关键字:Cadence教程、Allegro教程、AllegroPCB、Allegro技术专题、尺寸标注

Thieving是指在PCB设计中添加覆铜点或取样点的操作技术,是为了保持PCB在电镀时板上各点镀铜厚度均匀,避免该区域铜箔过度电镀的情况发生。添加的取样点以过孔形式表示,执行Thieving命令后,软件自动添加取样点,如图:关键字:Cadence教程、Allegro教程、AllegroPCB、PCB设计、thieving

对于高频电路而言,势必会产生传输线效应和信号完整性问题,怎样利用PCB的布线来保证整个高频系统实施是设计关键。为了避免高速电路的传输效应,必须严格控制关键网络的走线长度,合理规划走线的拓扑结构。本文就针对高速电路中的布线规则约束做一个系统的介绍。关键字:Cadence教程、Allegro教程、AllegroPCB、PCB设计、PCB约束

随着高密度、微型化电路板设计需求的不断提高,有必要考虑将无源甚至有源器件内嵌到PCB板中,以达到电路板体积小、重量轻的目的。比如移动电子产品、数码产品的设计中就会用到这种器件内嵌技术。CadenceRelease16.5提供了强大的器件内嵌解决方法(EmbeddedComponents),用户可以更方便的应用AllegroPCBEditor完成一些高密度、微

为了方便PCB板的安装,所有元件、安装孔都要有对应的丝印标号。本文主要介绍Allegro中丝印的生成方法。关键字:Cadence教程、Allegro教程、AllegroPCB、PCB设计、丝印、Silkscreen

电路板加工完成后需要进行测试,即检测所有元件引脚间的连接,确保没有短路和断路的情况出现。本文主要介绍Allegro中测试点的添加和测试夹具的输出方法。关键字:Cadence教程、Allegro教程、AllegroPCB、PCB设计、测试点、testpoint