- PCB 差分对的基础知识。

- 差分对布线指南,实现更好的布线设计。

- 高效利用 PCB 设计工具。

差分信号使用两个互补的信号来传输一个数据信号,但第二个信号与第一个信号的相位相反。信号接收器使用反相和同相信号之间的差异来破译信息。使用差分对布线传输信号有一些重要的好处,首先是能减少噪音和 EMI:

- 传入的干扰将被均等地添加到反相和同相的信号中。由于接收器是对两个信号之间的差异作出反应,无论是否受到影响,影响都是最小的。与影响单端信号的干扰相比,这样的性能要好得多。

- 差分对的电磁场大小相等,但极性相反,因此来自两条走线的干扰通常可以相互抵消。

- 所需的电压更低意味着功耗也更低。

- 信号的电压转换将更小,有助于确保电路板的电源完整性。

- 在较低的信号电压下可以使用较高的工作频率。

- 电压越低,辐射的 EMI 就越少。

如上所述,在电路板上使用差分信号有诸多好处,但也要付出一些代价。

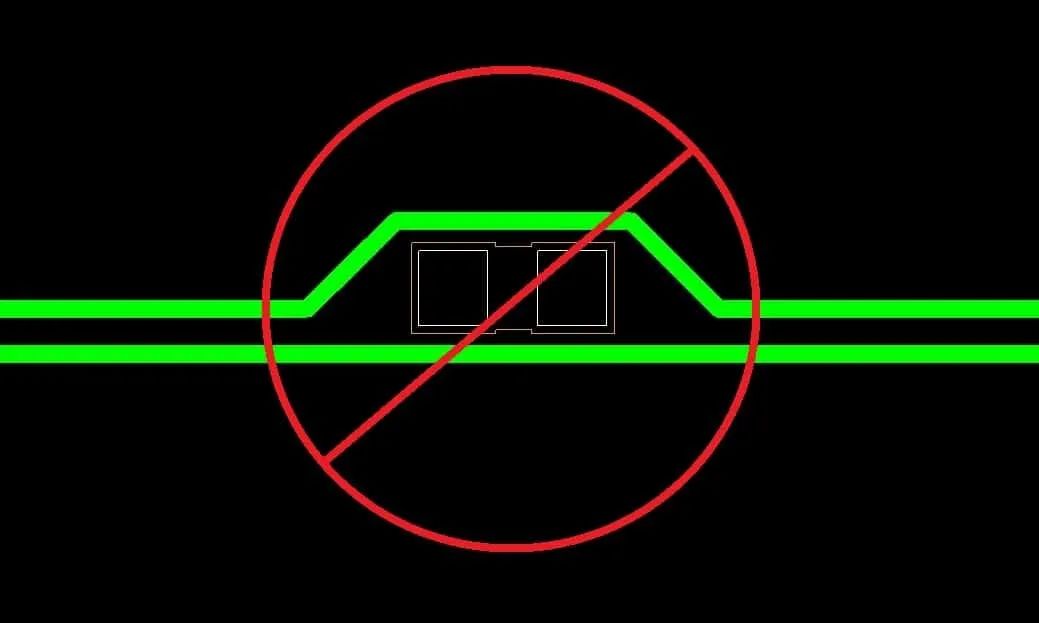

示例:不在障碍物周围进行差分对布线

- 如果可能的话,尽量避免使用过孔。如果必须要使用,应该对称摆放一对过孔。尽量使过孔靠得很近,它们相对于布线焊盘的位置应该是均等的。

- 最好使用内层布线,以尽量减少串扰,但这意味着使用过孔过渡到各层。

- 确保差分对与其他走线彼此分离。通常,间隔距离应为正常走线宽度间距的三倍。

- 如果可能的话,考虑在相邻的信号层上进行侧面差分对布线。这将带来更高的布线密度和更好的串扰控制。

- 规划布线方式,避免障碍物,如过孔或无源器件,以保持差分对的对称性(如上图所示)。

- 规划焊盘入口和出口的布线,使走线之间尽可能形成镜像。

- 在走线的整个长度上使用相同的走线宽度。

- 差分对走线之间的间距保持一致。

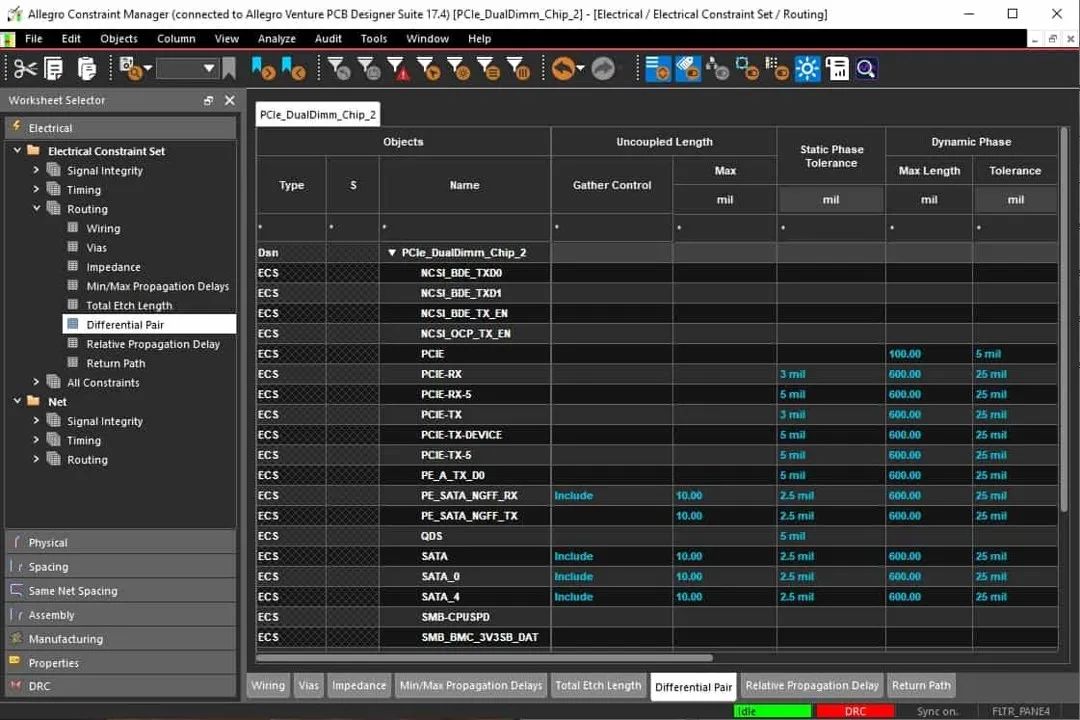

如果想要了解更多 Allegro PCB Designer 及其 Constraint Manager 的设计功能,欢迎点击下方图片: