- 了解电容性耦合的基本原理。

- 了解电容性耦合的利与弊。

- 了解关于减少电容性耦合的技巧。

这一原则同样适用于 PCB 中的嘈杂走线,本文将探讨电容性耦合的基础知识,并学习如何有效地减少电容性耦合以避免串扰。

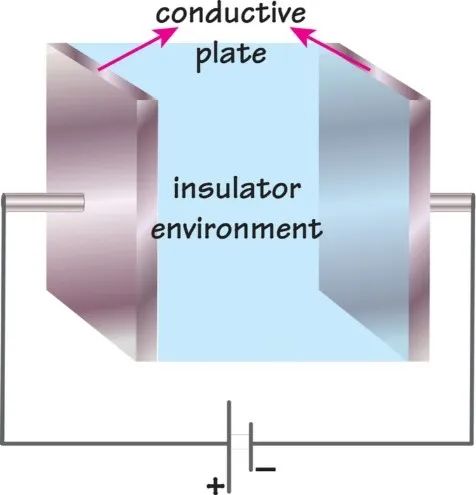

电容器由两个被绝缘体隔开的导电终端组成。当其中一个终端达到比另一个更高的电压电位时,电荷就会在终端之间积累。当电压从终端移除时,电容器以电流的形式释放电荷。

由于具有这样的行为特征,电容器隔断直流 (DC),但成为交流(AC) 的低阻抗路径。在 PCB 中,存在各种元件可以形成一个虚拟电容器,并允许电能在其间转移。

电容性耦合,也被称为静电耦合,是能量在被绝缘体隔开的导电元件之间移动的方式。例如,如果两条铜走线摆放得很近,电容性耦合将导致一条走线上的电能转移到另一条走线上。

接下来,我们将仔细分析这种电能转移的利与弊——具体取决于设计目标。

往好的方面看,一个爱说话的孩子可能成长为未来的领袖、辩论家或是律师。同样,电容性耦合有利也有弊,这取决于具体的情况。

然而,由不良电容或 寄生电容 导致的电容性耦合会破坏电路的性能。电容性耦合会导致串扰,即一个导体的信号被耦合到相邻的导体。

例如,如果 SPI(serial peripheral interface,即串行外设接口)数据靠近一个模拟信号,后者会接收到 SPI 传输的微弱脉冲。相互间的电容性耦合也可能发生在两条传输高速信号的线路之间,损害两个信号的完整性。这样一来,两个信号的接收端会出现很高的错误率。