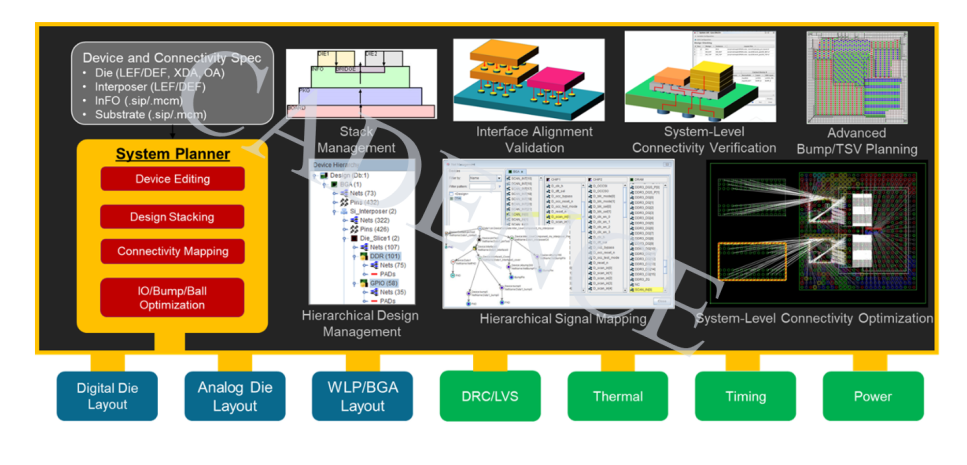

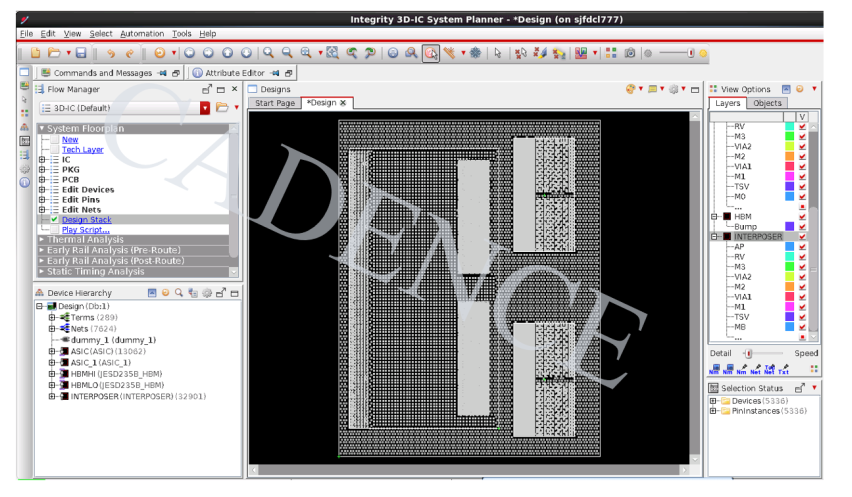

Cadence Integrity 3D-IC 平台是行业领先的全面的整体 3D-IC 设计规划、实现和分析平台,以全系统的视角,对芯片的性能、功耗和面积 (PPA) 进行系统驱动的优化,并对 3D-IC 应用的中介层、封装和印刷电路板进行协同设计。

近几年,随着摩尔定律的失效,集成电路的设计发展逐渐从传统的二维平面转向立体,人们获得了三维带来的诸多优势,比如:更短的引线、更低的功耗、更高的性能和带宽、更小的封装尺寸、以及更好的良率,但同时三维设计也带来了新的挑战:例如设计的聚合与管理、额外的系统级验证等。

过去行业中的解决方案多借助于点工具搭建的流程,裸片和裸片、裸片和封装之间的设计缺少联系,无法进行早期的探索和获得反馈。为了使集成后的系统仍能满足设计要求,必须过度设计以留下余量,造成性能受限并且成本高昂。

Cadence 在 2021 年推出的 Integrity™ 3D-IC 平台,正是为了应对这些挑战而设计。

Cadence Integrity™ 3D-IC 平台集成了 3D 设计规划与物理实现,能够支持系统级的早期和签核分析,全面完整地助力设计者实现由系统来驱动的 PPA 目标。

Cadence Integrity™ 3D-IC 系统级规划

1.系统级规划和优化 2.系统连接性检查 3.Integrity 3D-IC 与系统分析工具的融合

1. 系统级规划和优化

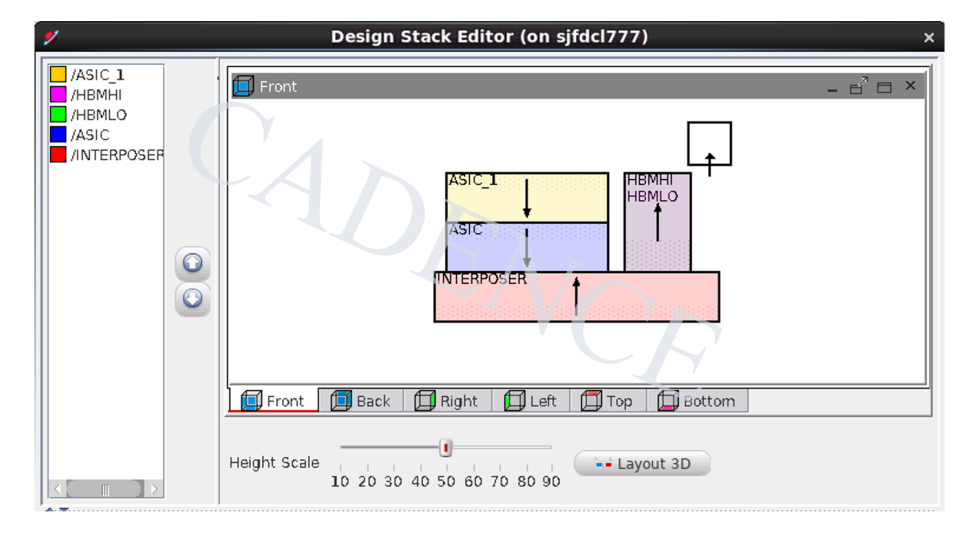

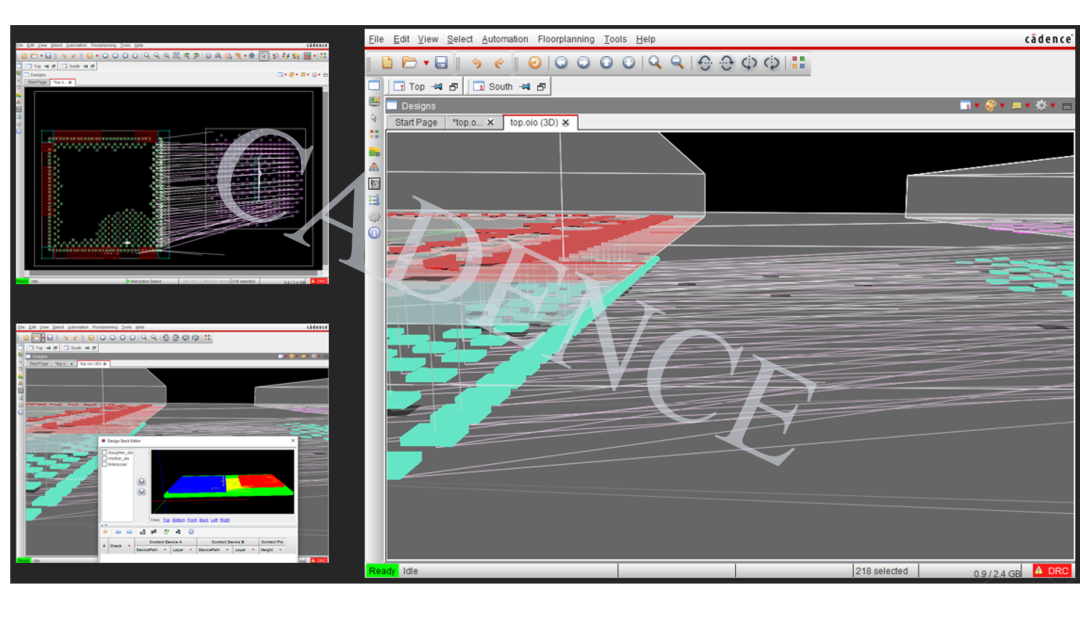

- 芯片的堆叠

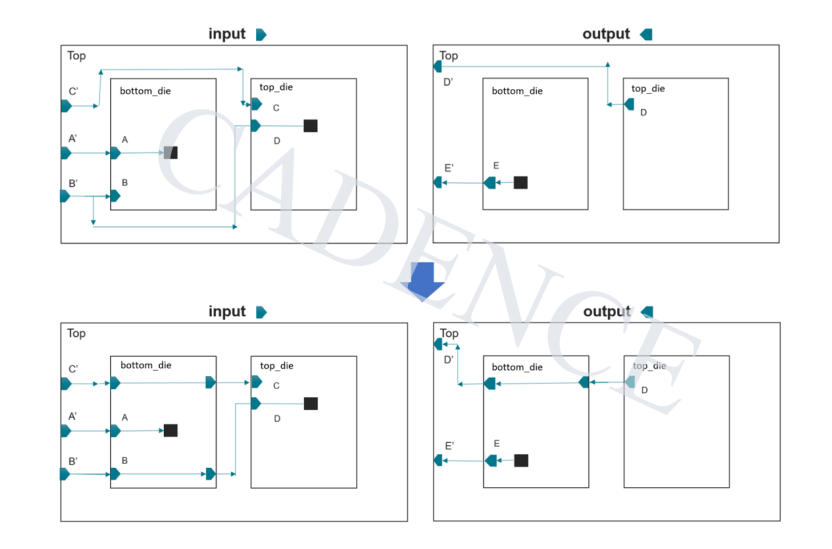

- Feedthrough 的插入

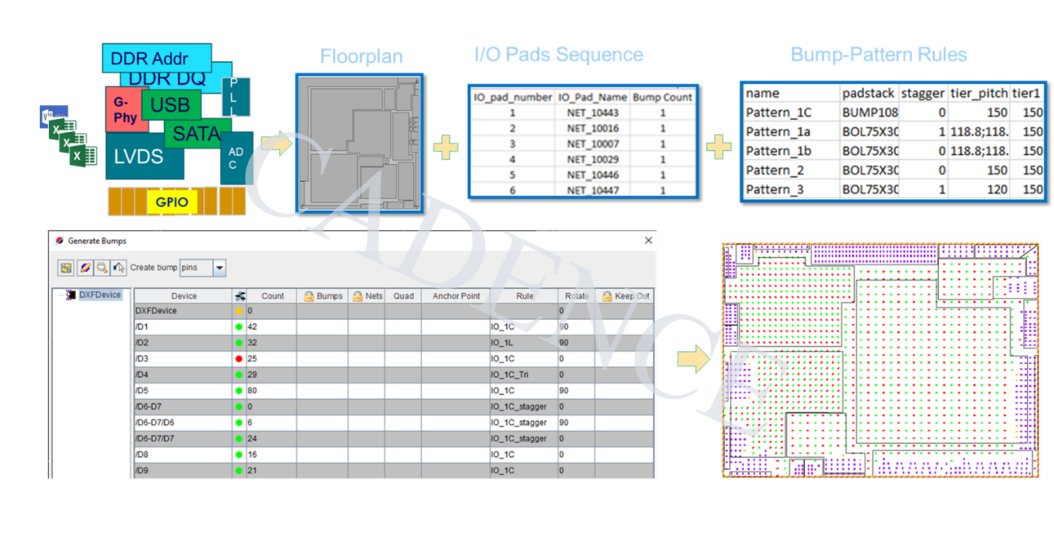

- Bump 的规划与优化

- 3D 图形界面

2. 系统连接性检查

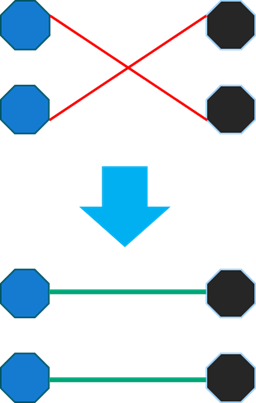

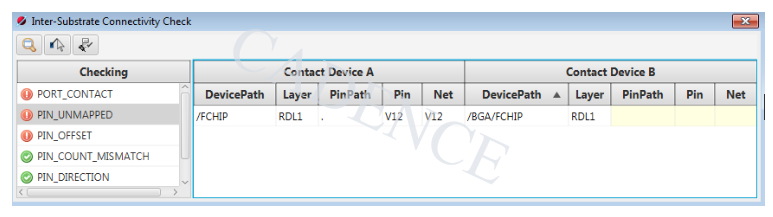

- 芯片间接口连接性实时自动检查

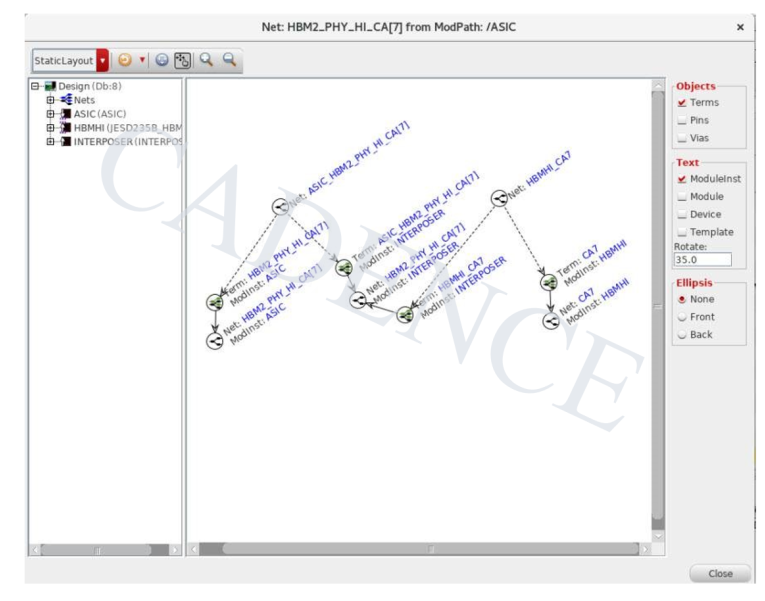

- 系统连接关系图

3. Integrity 3D-IC

- 与系统分析工具的融合