PCB及元器件可靠性建模及分析的重要性

目前市场上对于大多数复杂电子系统的设计实现时都要求具有高的可靠性设计水准,如电信行业,医疗,航空航天,太阳能光伏产业,汽车电子等等。在很多情况下,这些电子系统必须暴露在冷热交替的湿度环境中运行长达25年之久,因此系统设计厂商需要知道他们的产品是否能够满足如此苛刻的工作环境。本文提出了一种新的可靠性建模及分析方法可以用来预测这些系统中电子系统的失效率。这种预测失效率的方法为设计者提供了在设计阶段中发现和纠正设计缺陷,以避免投入巨资而最终却丢失了在该行业的市场机遇。失效率可以用来预测在热循环中焊点和导电通孔的疲劳度及阳离子迁移(也称导电阳极丝)引起的短路CAF(Conductive Anodic Filament)。本文也提出了电路板的有限元分析,分析过度的振动和机械冲击事件过程中显示电路板哪些区域容易受到过度应变。这里最大的价值来自于工程师可以通过执行各种”What if”的情况来决定任何设计组合所带来的影响。

* 如果安装孔位置改变了情况会怎么样?

* 如果过孔的直径、间距改变或PCB铜箔厚度改变情况会怎么样?

* 如果改变材料的厚度或材质会怎么样?

* 哪些器件存在高度风险引起失效或更换元件封装会存在什么问题?

* 如果将焊锡材料从SnPb变为SAC305会对可靠性产生什么影响?

最后,一旦设计被优化到达到满意的要求,软件会预测产品在整个生命周期中的失效率,这些信息被用来更加精确的控制成本,这里也应用一些实际的案例来展示软件的这种能力和价值方法来满足电子行业的需求。

作者简介

作者Greg从事电子行业40年之久,专注于SMT方面的技术研究,属于行业的先驱领军人物。目前作为SR.的高级会员并从事DFR方面的研究工作。他本人曾就职于Reactive Nano Technologies和Newport Enterprises公司,分别担任工程副总裁和商业部副总裁一职。

他本人的经验专注于SMT加工,电路板制造和材料,高级封装,IC制造流程和材料,焊接制程,RoHS和纳米工艺的特殊芯片绑定技术。

Greg, a Past President of IMAPS NA,于1989至2000年担任IMPS Advanced Technology Workshop国际微电子与封装协会主席(IMAPS),同时担任3年的高级微电子杂志(Advancing Microelectronics magazine)的总编辑。

Greg.在美国奥斯汀同时获得了罗格斯大学电子工程学学士和圣爱德华大学的管理学学士学位。

引 言

任何电子系统或组件都是一种复杂物质之间的相互作用产生,这些物质又取决于其内部各种机械,热和电性能之间的相互作用。

这表明在产品设计早期产品的总成本和质量占据最主要的影响。在产品开发周期之后发现和纠正设计缺陷的成本是非常昂贵的,尤其是在现场应用时发生的严重设计质量问题。运用新的可靠性预测方法,将彻底改变这个过程。在单个产品生产之前,新的预测法使工程师将设计文件导入,并根据用户的实际使用环境进行假设,定量预测产品的使用寿命。

随着电子行业的利润率不断萎缩,原始设备制造商(OEMs)更依赖扩大各种利润。不准确的寿命预测将严重的削减公司现金流,预计失效率偏低将导致成本超支,而预计失效率过高将意味着失去了商业竞争力,延长了保修计划同时预留出资金可以开发下一代产品。本文的可靠性预测新方法提供了这种能力和价值,可以预测电子设计环境中的各种功能单元的可靠性,包括裸片,封装,电路板和整个系统。

环境应力是评估的一个因素,从不同的行业如2-3年使用寿命的手持电话到长达25年使用寿命的太阳能电子设备。这些严峻的环境包括:

a.在变化的温度或极限温度下使用

b.工作温度范围在-55°C to 125°C

c.应用在产生较大的冲击,压力,振动或湿度环境中

d.可存储时间超过10年

e.应用时寿命跨度从10年到25年

当面对这些令人望而生畏的产品设计要求,能够尽早发现产品能够适应该环境和应用场合是极其重要的。

一般失效模式

Wire Bond Failures绑定线失效

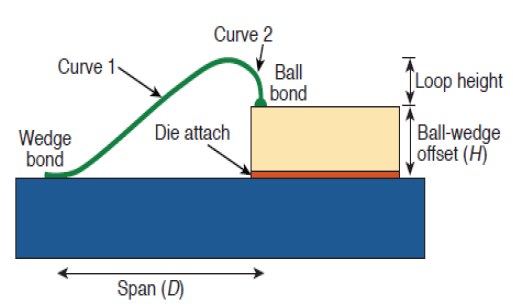

绑定线是过去50年来最主要的芯片封装互联方式,常见的绑定线材料是金,铝或近年来开始使用的铜。常见的绑定焊盘材料是铝。如图1为典型的绑定叠层图。

Figure 1 – Cross Section of a Typical Wire Bond.典型绑定线叠层

如果持续暴露在高温下(内部为金属化合物),暴露在高温且与人体接触,暴露在温度循环变化(缓慢变化),绑定线会发生失效。

Printed Wiring Board Failures印刷电路板绑定线失效

印刷线路板存在多种失效模式影响到可靠性,PCBs常见的失效情况如下:

* 尺寸(高温下大尺寸的板子体现明显)

* 厚度(厚度大的板子存在更大的热应力)

* 材料(低Tg转化温度参数的材料更容易受到影响)

* 设计本身(高密度,高宽长比)

* 过回流焊的次数

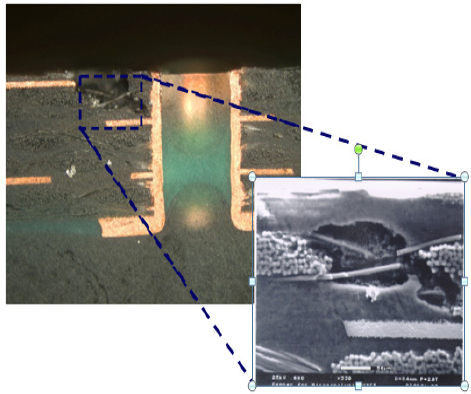

这些失效模式在如图2的阳离子迁移(CAF)属于比较典型的现象,同时因一些地方的避让,走线也会带来贯穿孔PTH。

Figure 2– Conductive Anodic Filament Failure阳离子迁移失效

阳离子迁移(CAF)被称作是金属电迁移,印刷电路板表面受外在离子污染或因腐蚀后铜焊盘表面所产生的离子,将从印刷电路板表面的阳极透过印刷电路板的内层向阴极沉积造成漏(导)电现象,此现象发生在分离的玻璃与环氧树脂间,这是个电化学过程。CAF可以引起电流泄漏,电路内部间歇式短路,PCB内部导体间电介质击穿等。

PTH孔产生的避空区域(voids)会引起大的应力集中点,导致裂纹缺陷。该避让位置可以提供至关重要的信息,用来识别缺陷的过程;它围绕玻璃束;在树脂区域;在内层互连线(形成楔状避让)或者在PTH孔的内测或PTH孔边缘。走线腐蚀(etch pits)是由于锡抗腐蚀剂不足或不恰当的外层走线制程及重新走线导致。他们都可以引起局部某个部位产生大的应力,增加出现裂纹缺陷的可能性,严重的走线腐蚀可导致电路开路。

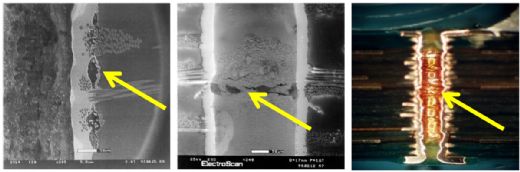

PTH孔产生过应力导致的裂纹现象是由于压缩PTH时热膨胀系数(CTE)不匹配。在ICT测试时使用“针床”探测施压时也会对PTHs产生压力。电镀铜时的环状裂纹也会产生在PTH孔壁,这是由于电镀铜的应力(~17mm)和印制板外层平面(~70mm)的热膨胀系数存在差异。如图3展示了三种失效机理:

图3 PTH孔失效机理:void避空区域(左),Etch pits走线腐蚀(中),孔壁裂纹(右)

或许在非理想状态下,如果你能确定在产品设计阶段没有发生任何有关失效机理现象也能使产品保持在预期的环境中可靠的运行,那么你完全可以在设计阶段使用自动化来设计分析。

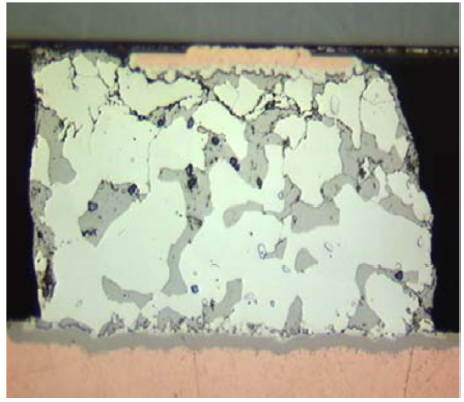

Solder Fatigue Failures焊接疲劳引起失效

SMT焊点的机械疲劳性能是电子产品中的一种主要耗损机理。这一点在商业级/消费级的户外环境很真实的存在,尤其要求长寿命和严格的操作条件。这种在产品生命周期中分析评估焊点的疲劳度产生的应力方法,可以提供深层次的分析焊点是否存在失效。如图4,为BGA封装下方焊点产生的疲劳现象实例。

图4 BGA封装的焊点疲劳现象实例

Automated Design Analysis自动化设计分析

在执行自动化设计分析时,应考虑一些高级别步骤。

其中包括:

* 定义可靠性目标

* 定义环境

* 添加电路板

* 导入文件

* 生成输入

* 执行分析

* 解析结果

Reliability Goals可靠性目标

确定理想的产品寿命和性能标准并将其记录在案。

理想的产品寿命可定义为保修期,亦或视客户的期望而定。一些公司根据生存性设定可靠性目标,然而生存性却往往受限于诸如过去 15 年多来 95% 的可靠性和 90% 的信心等置信度。使用生存性的好处在于,可帮助设定测试时间和样本大小的界限,而并未假设故障率特性(降低、增加、稳态)。

Defining Environments定义环境

有意义的可靠性预测,必须考虑到产品应用的环境。有几种常用的方法识别环境。方法 1:使用 MIL-STD-810、MIL-HDBK-310、SAE J1211、IPC-SM-785、Telcordia GR3108 和 IEC60721-3 等工业/军工标准。该方法具有以下优势:低成本标准、综合性以及在业内的共识性。若某既定行业相关信息缺失,仅考虑其他行业的标准即可。该方法弊端在于,标准存在的时间,有些已经超过 20 年,针对目前的使用而言缺乏验证。这些标准以未知的界限高估或低估了可靠性。

确定现场环境的另外一个方法是,在类似环境中对类似产品进行实际测量。这样可确定平均和实际中的最差情况。可以确定所有导致失效的负载,也可将所有环境、生产、运输、存储和现场纳入分析。除热循环环境外,在分析中还可输入振动和冲击值。图 5 所示为此输入示例。

振动负载可能非常复杂,且可能包含正弦振动(g为频率的函数)、随机振动(g2/Hz 为频率的函数)以及正弦叠加随机振动。视底盘/外壳而定,振动载荷可以是多轴、带阻尼或放大的。

Figure 5 – Typical stresses that can be addressed in the Automated Design Analysis

Import Files导入文件

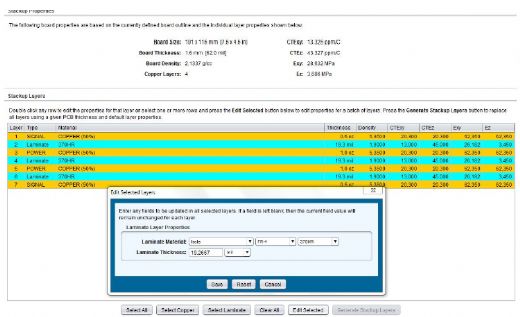

自动化需要分析的数据可从外部导入ODB++文件,这里面包含了所有的PCB元件信息和它们的位置信息,也可以通过导入Gerber文件和对应的元器件清单(Bill of materials)。如图6展示了一个PCB叠层和相关的可靠性模型的实例。它可以自动生成PCB叠层,其内部的数据库模型数量超过了400多种复合材料,每一种材料都有48个不同的属性来定义被选择模型。

Parts List 元器件列表

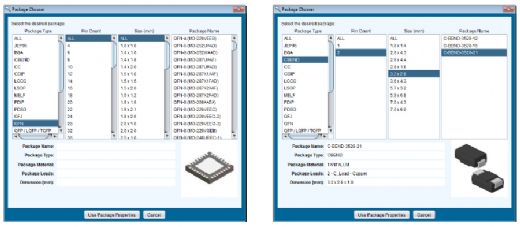

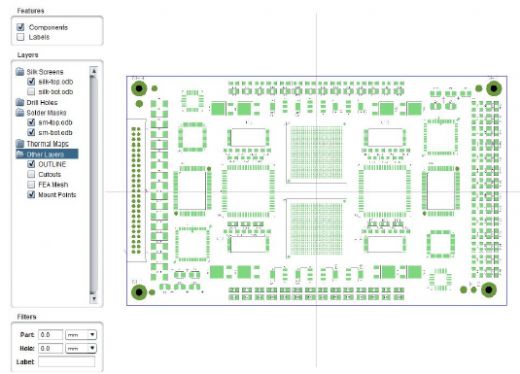

每一个独立的元件数据是ODB++文件的一部分,然而,有时候需要手工修改下元件的数据以确保元件的物理特性是准确的。如图7(a)展示了元器件编辑器下的2个元器件属性,如C-Bend和QFN的封装,用户可以在分析过程中很容易的选择到正确的封装。图7(b)展示了PCB板上的元器件排列图。

Figure 6– PCB Stackup with Materials Database

Figure 7 – Illustration of Component Editor (a) on top and Board layout (b) on bottom

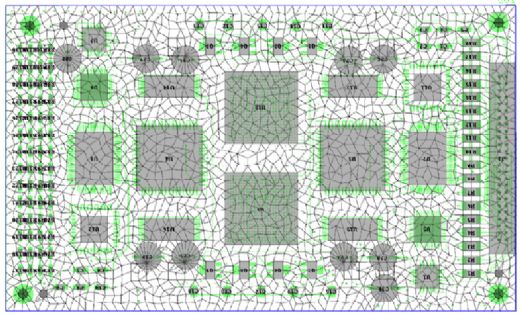

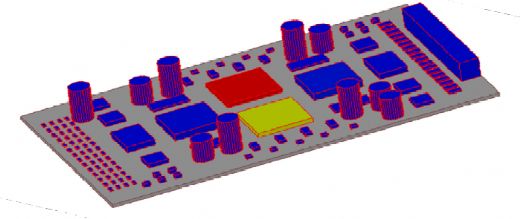

该分析还可以通过从输入的数据中创建一个网状结构和模型建立3D模型。图8展示了网状结构。图9展示了典型的三维立体图。

Figure 8 – Mesh Configuration

Figure 9 -3D Image obtained as a Result of Analysis

根据提供这些信息进行分析处理即可获得输出的可靠性的信息。

Analyses分析

分析时可以执行8种不同的分析,其中包括:

CAF-阳离子迁移信息

电镀过孔疲劳度

焊接点疲劳度

有限元模拟仿真

ICT冲击

DFMEA设计失效模式分析

振动疲劳分析-固有频率

机械冲击

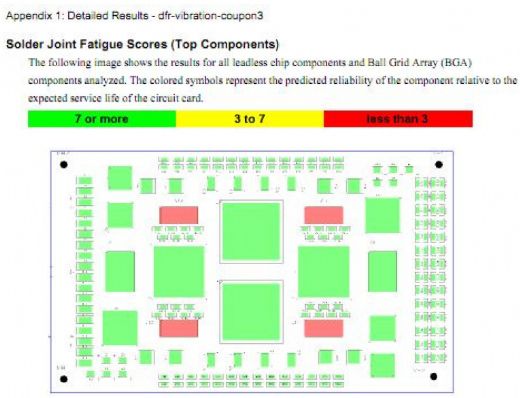

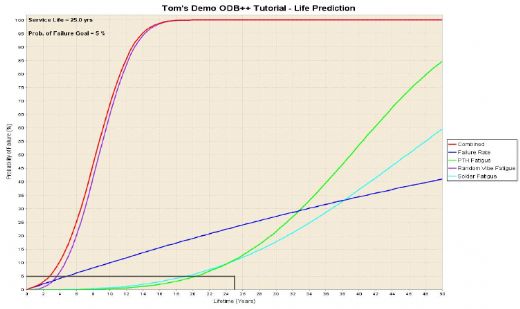

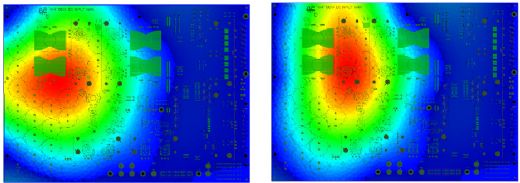

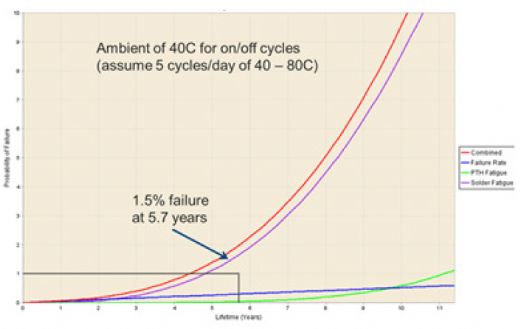

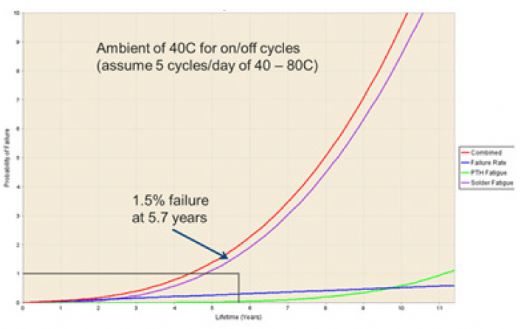

这些输出的信息可以通过不同方式来表示;如可靠性差的相关曲线,存在差异化元件的列表,物理位置,整体评估及元件的相对排序。如图10所示。

Figure 10 – Failed component Locations (top) and Unreliability Curves (bottom)

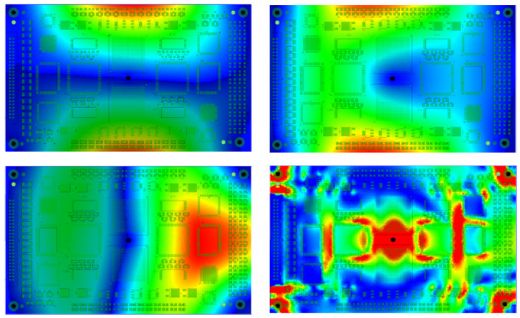

分析时还可以找出固有频率对产品设计某个区域的影响,如图11所示。它可以提供很形象的应力位置信息并对应到固有频率上。该软件可以识别多达10种固有频率。

Figure 11 – Natural Frequencies Identified (1st-upper left), (2nd-upper fight), (3rd -lowerleft) and 4th – Lower Right)

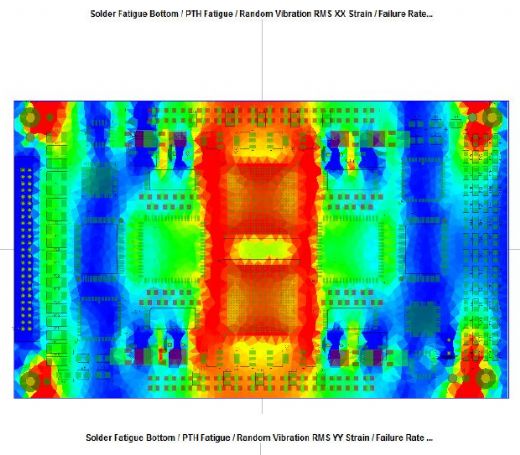

除此之外,分析时还能提供电路板根据振动情况产生的应力分布数据,图12展示了XX和YY方向上的振动数据。

Figure 12 – XX (top) and YY (bottom) Images Illustrating Strain Levels

“What if”分析实例

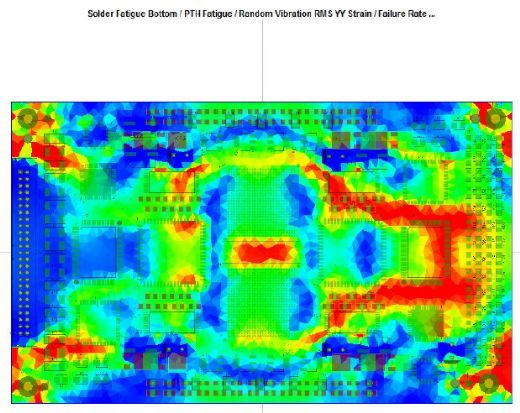

图13给出了航天电子设备中使用的电路板卡上焊点疲劳特性对比图。左图为使用Sn/Pb装配时的结果,右图是使用SAC-305锡膏焊接的结果。在Tin/Lead分析中按照产品预期10年寿命来分析焊锡焊点的疲劳度,用绿色的曲线表示。然而,当采用SAC-305焊锡分析时,焊点的寿命低于10年,也用绿色的曲线。完成该仿真分析对比仅花费了不到5分钟的时间,曲线对比的结果表明,对于航天类的用户将焊锡换为无铅(Pb-free)材料时会对产品性能带来不利的影响。

Figure 13 – Comparison of Sn/Pb and SAC-305 Solder Joint Fatigue in Avionics Application

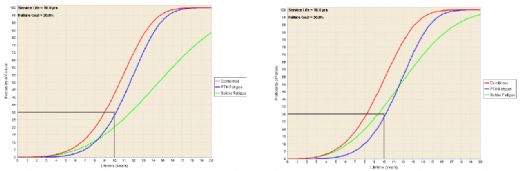

另一个实例,在工业类用户中都有因振动测试引起失效的经历,在此过程中,DFR可以快速在固有频率变化后确定安装螺柱的最优位置,来消除设计中产生的问题。图14展示了不同位置的结果,通过“what if”仿真分析的时间少于5分钟。

Figure 14 – Comparison of Mount Point locations (left image is failing), (right image after addition of mount point-Passing)

PRODUCT TEST PLANS产品测试计划

众所周知,产品测试计划包括了设计验证,产品认证和加速寿命测试,这些都是一个新产品或新技术成功推向市场的关键。这些测试计划需要足够的压力条件,以反映出真正的设计不足或缺陷,但又不能过度的提高测试条件水平,而引起的非代表性产品故障发生。测试必须足够快,以满足严格的时间进度要求,但不能因此加速而产生过大的应力。每一次测试都必须提供有价值的信息,而且必须证明满足最终使用环境(包括筛选,存储,运输,安装和实际运行)。

关键的第一步是很好的了解该产品的使用环境。如何在运输过程中保护产品(卡车,轮船,飞机,降落伞,仓库等)?怎样的工作温度/湿度,热循环状态,环境温度/工作温度,盐的成分,硫的成分,粉尘状况,液体状况等以及机械循环(盖板循环,连接器循环,扭曲位置等)对产品的影响,尤其是在航空电子设备应用中尤为重要。

随之而来的问题 – 你有测试数据吗,是否靠猜呢?

产品测试计划对新产品或新技术的成功是至关重要的,必须有足够的压力测试条件,以模拟真实的工作环境来找出产品设计的缺陷。基于失效物理(PoF)来制定测试计划和配置文件,可以模拟出与实际应用领域关联的情况。本文将提供在深入理解这一过程之上而制定的可行性测试计划,通过仿真工具的提前模拟来最小化执行测试过程,从而降低开发成本和时间进度。

图15是一个自动化设计分析案例,展示了如何根据提供现场环境提出合适的测试时间和测试条件,来制定分析失效机理的产品质量计划给客户。

Figure 15 – Failures Curves on Top and Predicted Test Plan for Validating Data on Bottom

总结

本文介绍了一些与电子产品可靠性相关的问题,可以使用仿真工具在设计阶段来分析用以提高产品可靠性,减少问题的发生。

设计前期了解这些信息可以允许设计师在设计阶段,对诸如过孔连接点,元件布局,加强固定装置等进行修改,以确保符合可靠性的要求,在早期启动原型制造的运行,可以充分的预知后续生产带来的问题,从而降低了开发成本和风险,同时缩短产品的上市时间。

注:利用软件预测PCB失效物理,用户仅需要通过ODB++导入数据,主流PCB设计工具Cadence Allegro PCB, Orcad, Mentor BoardStation, Expedition,PADS, Zuken, Altium/Protel均为ODB++输出文件。