Sigrity SystemSI 可以对高速串行通道进行眼图和误码率分析,对系统中的任意参数进行扫描,得到最优化配置,并且集成了 PCI-E、SATA 等工业标准,直接对仿真结果进行判别。

Sigrity SystemSI 可以对整个 DDR 系统进行准确的 SSN 分析,集成 JEDEC 标准,自动为用户量测 SI 参数,并以此为基础,进行自动化时序分析。

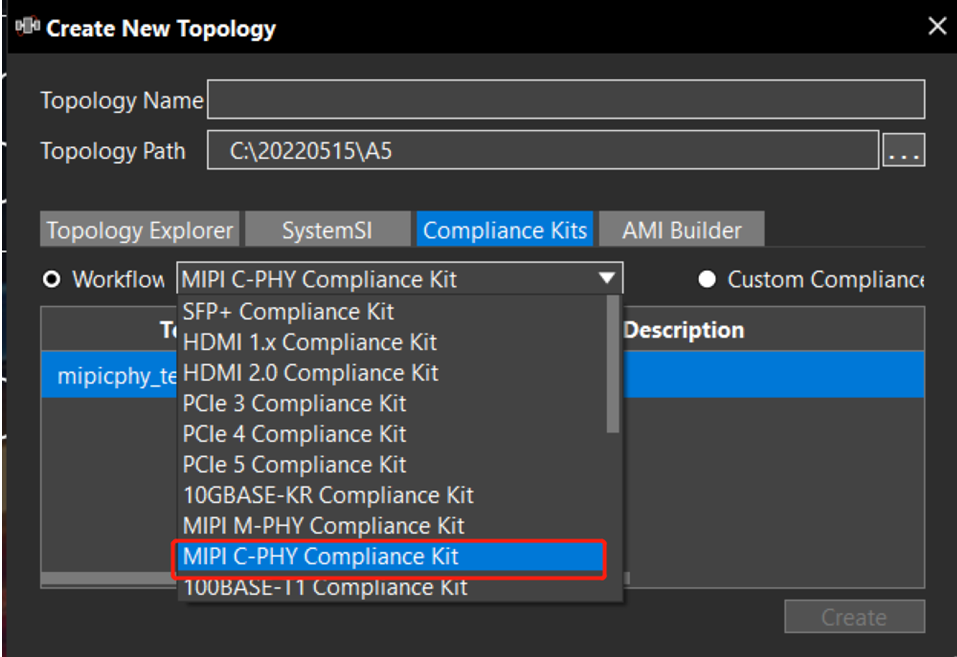

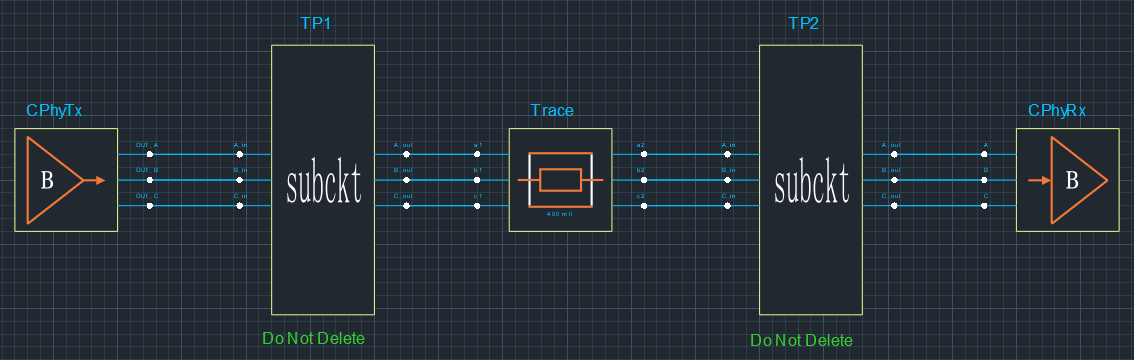

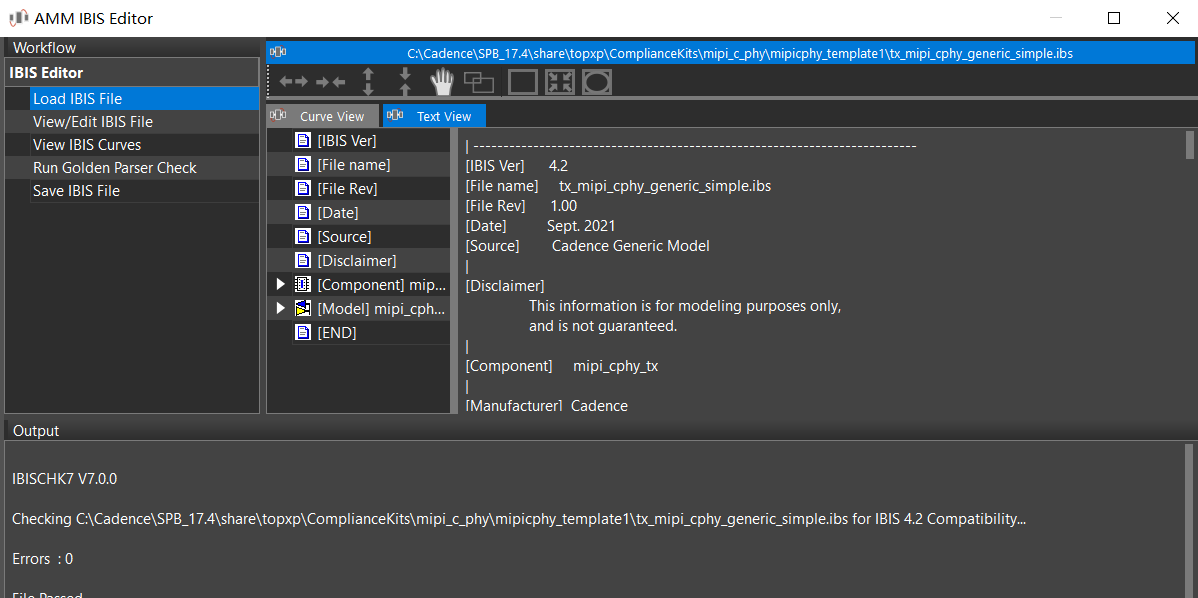

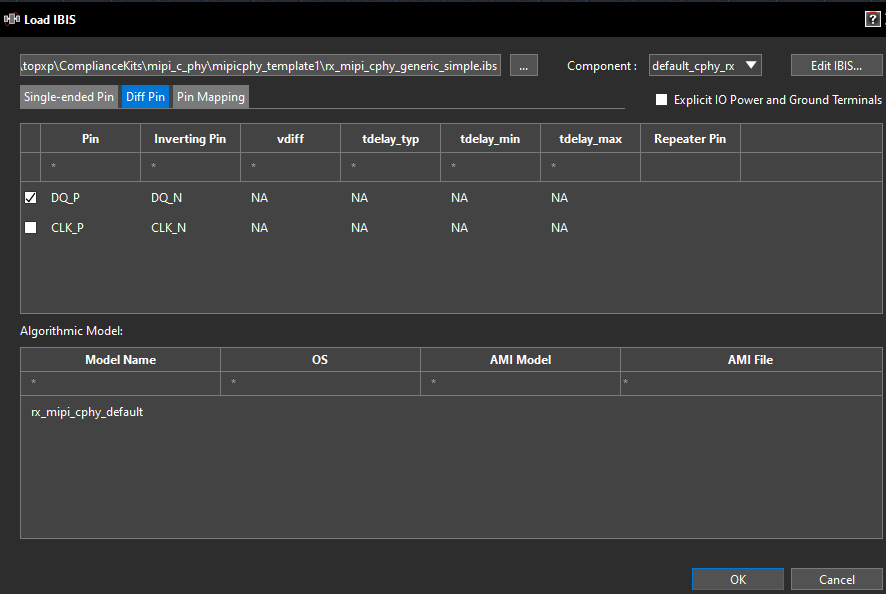

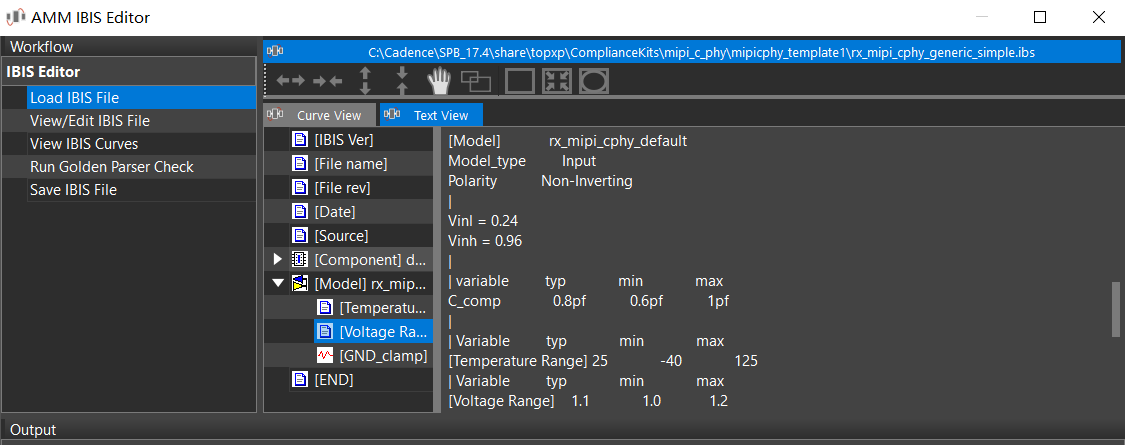

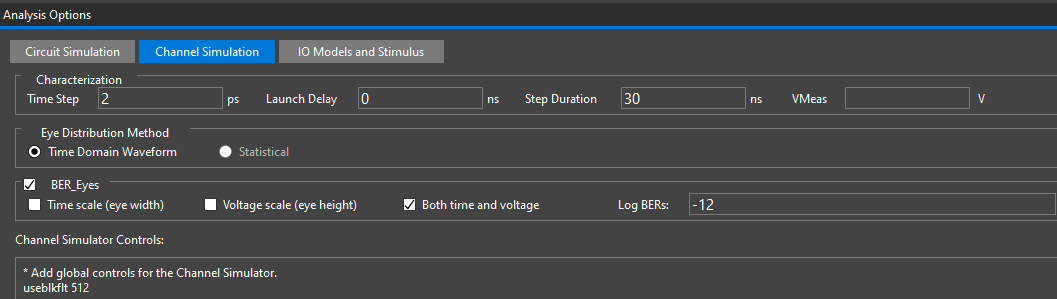

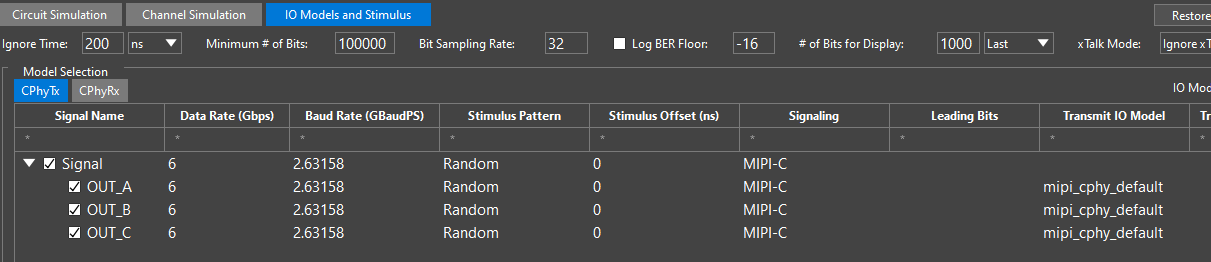

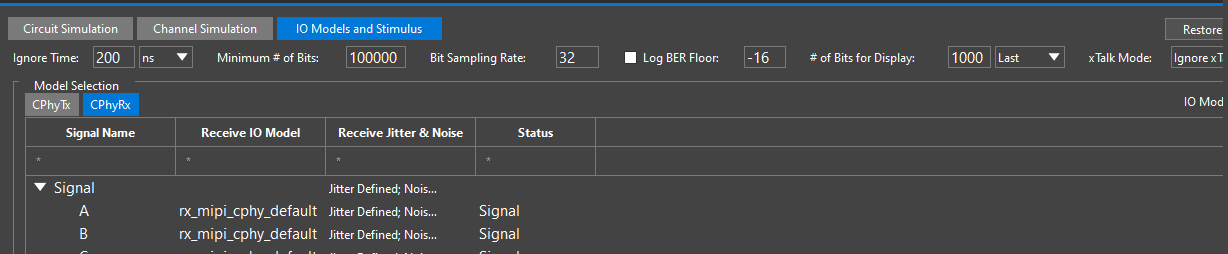

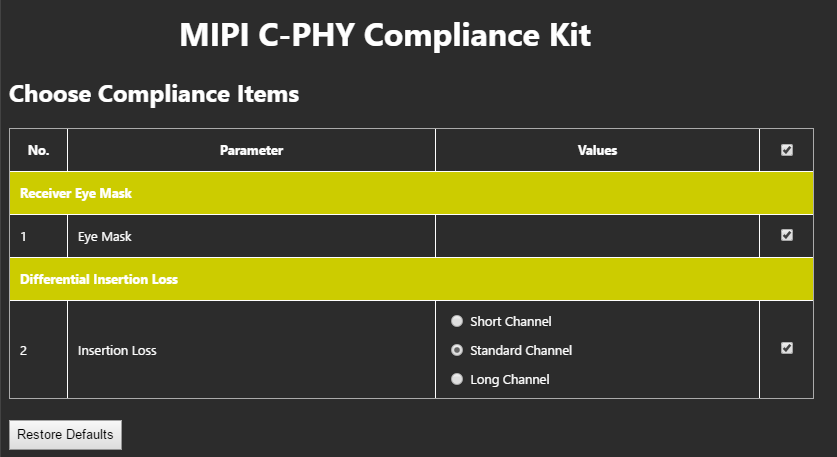

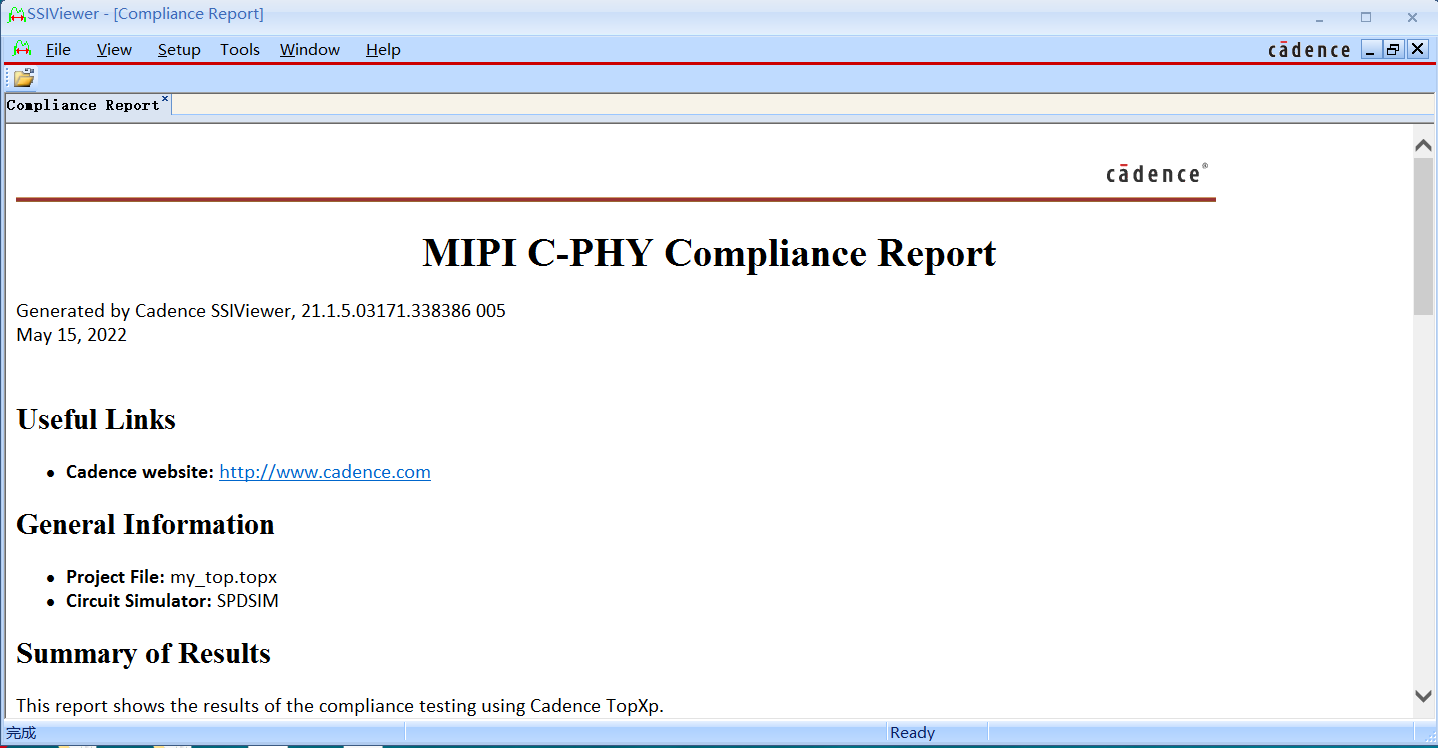

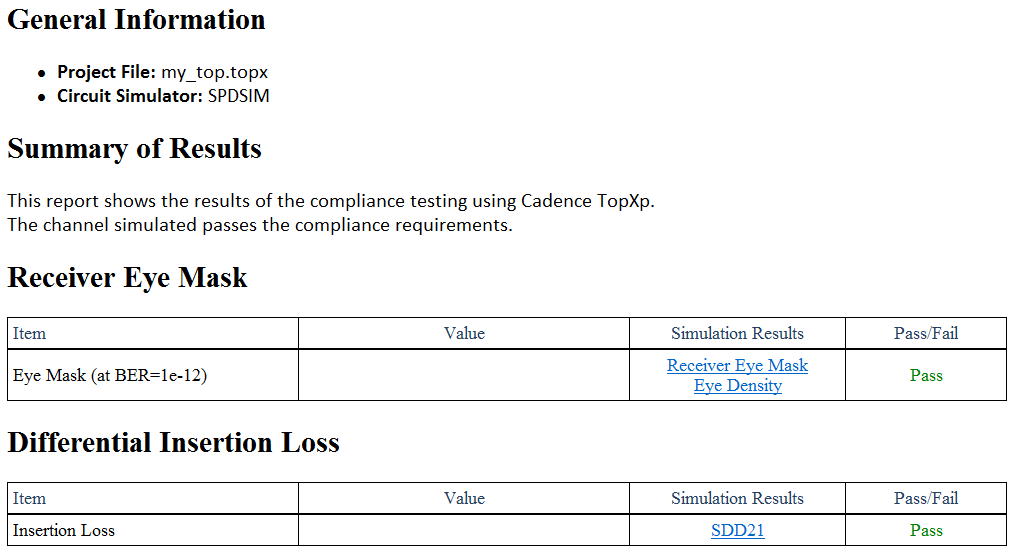

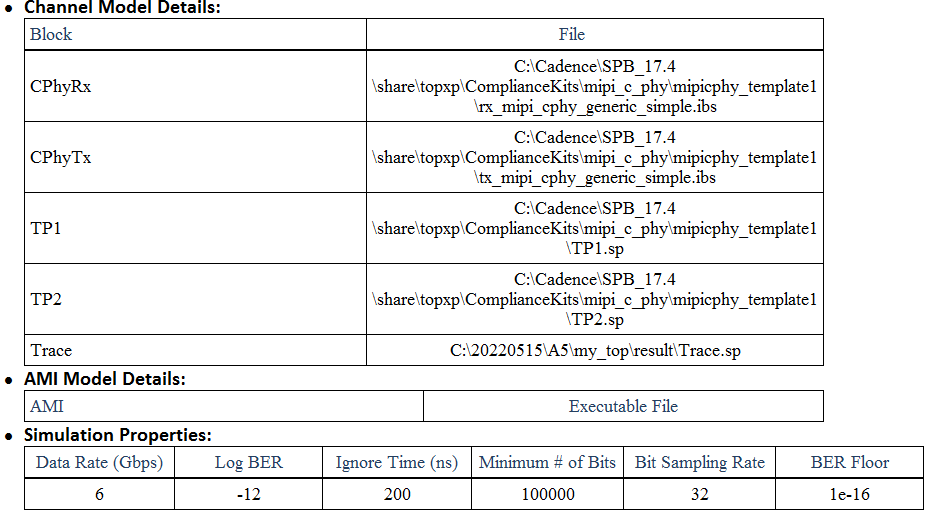

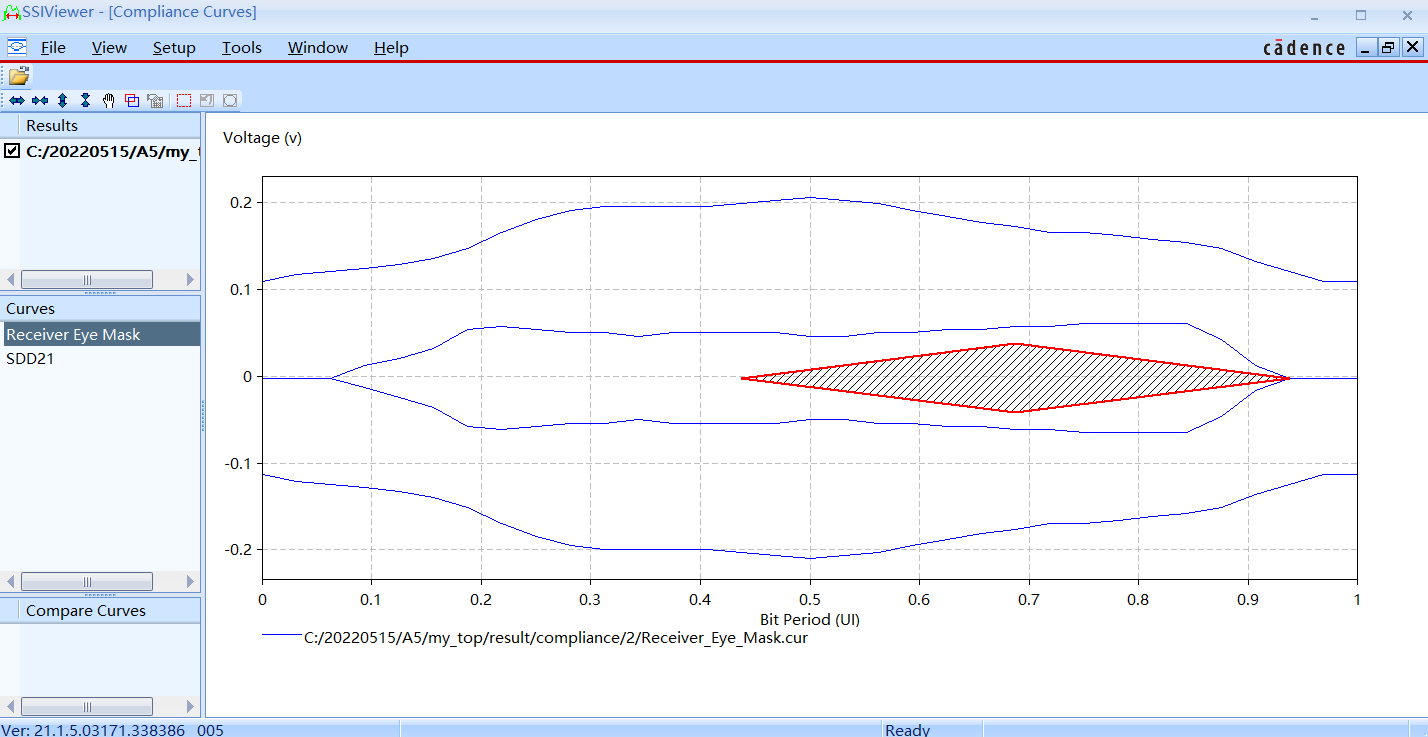

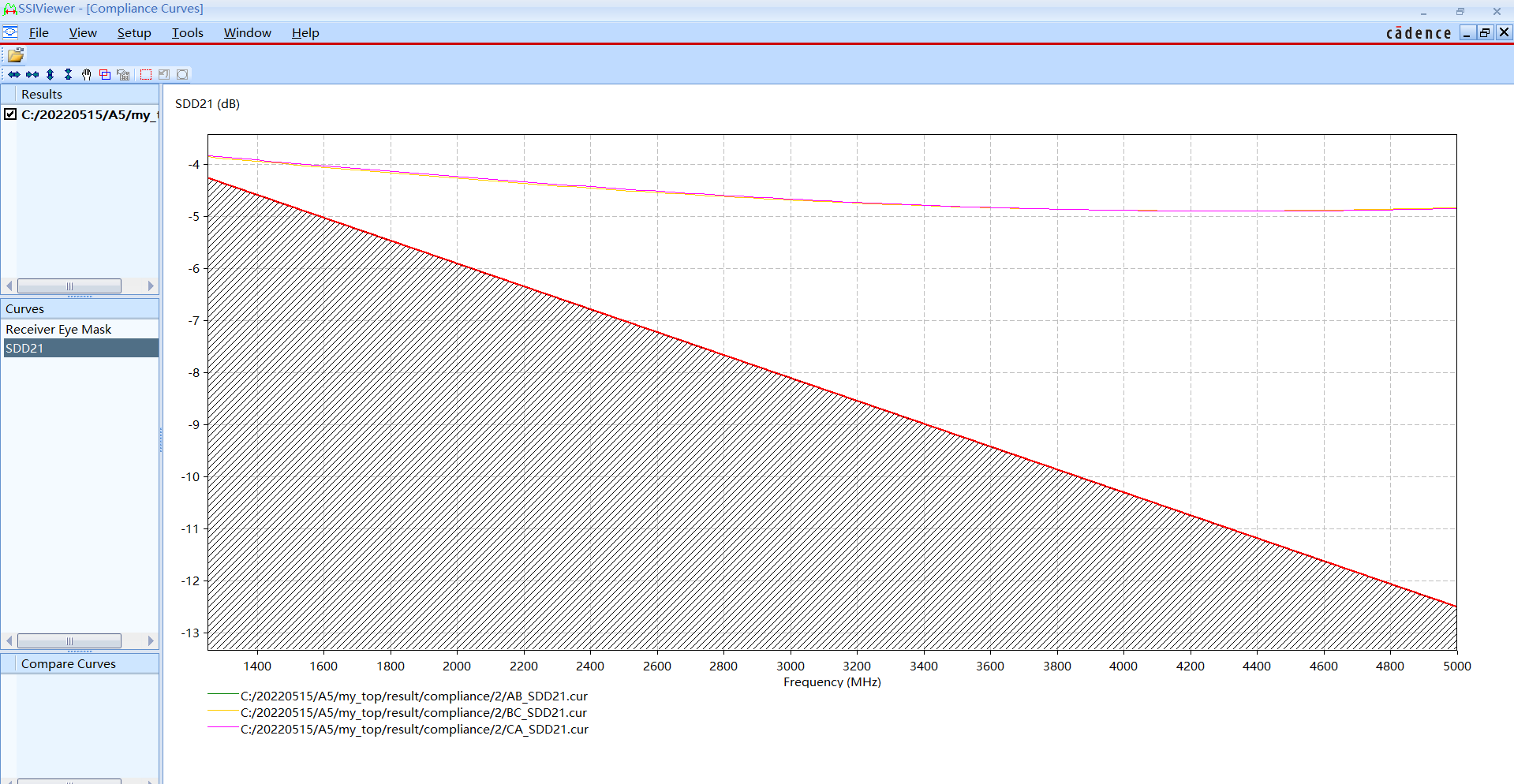

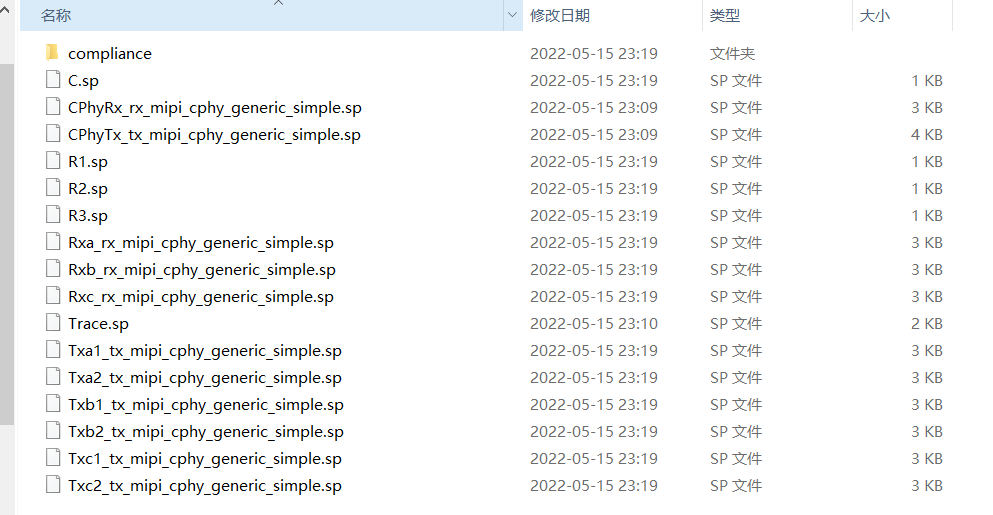

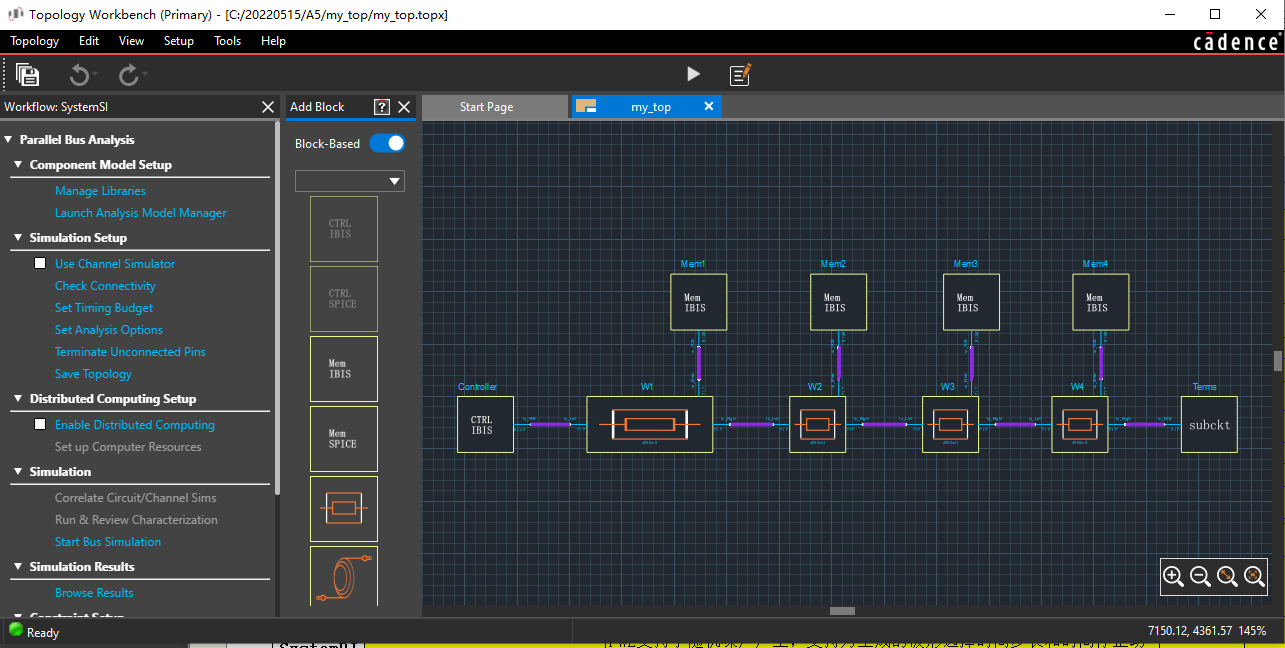

Wbench_SPB17.4_QIR4 更新之后,Sigrity SystemSI 可以支持 MIPI-C 仿真与合规检查分析,支持信号链路拓扑互连及仿真。