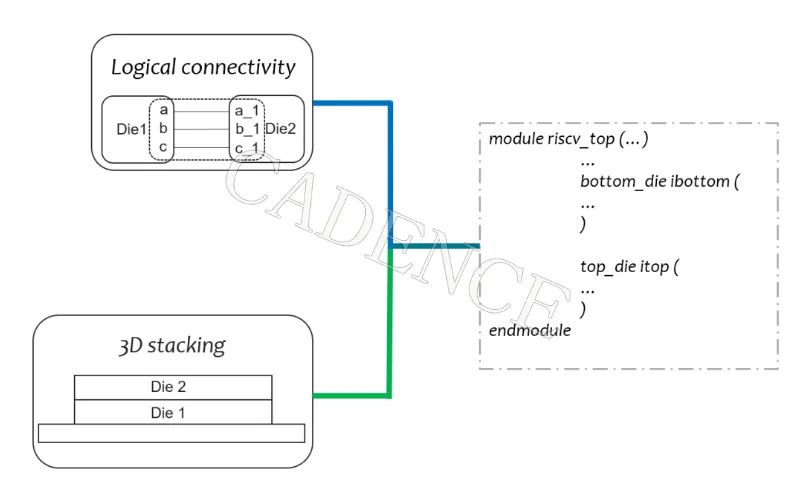

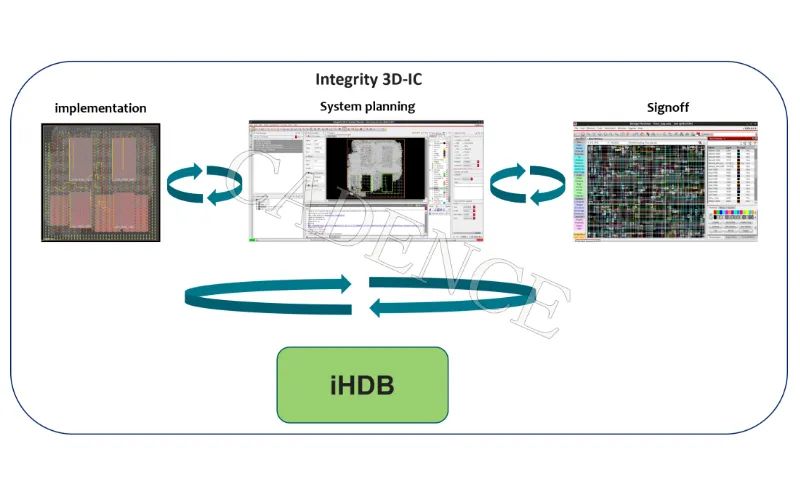

- 通过系统规划器为 3D 系统提供独特的层次化设计和优化功能

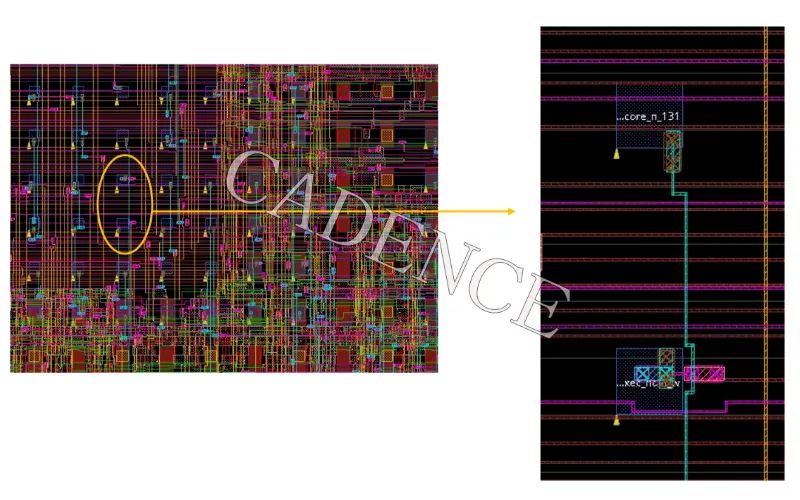

- 通过与 Innovus™ Implementation System 基于 Tcl 的实时直接集成,提供完整的堆叠管理、芯片到封装的信号映射以及先进的 Bump 和 TSV 规划功能

- 高效的数据库,可对每一层堆叠结构进行层次化的多级表示

- 顶层规划

- 物理与逻辑连接的设计和优化

- 物理实现的自动化流程

- iHDB (Integrity Hierarchical Database)

- 数据的同步

凭借 Cadence 在模拟和数字 IC 设计,封装设计以及 PCB 设计领域提供的全方面 EDA 工具产品的集成,Cadence Integrity 3D-IC 通过统一的层次化数据库结构,利用 Cadence 行业中先进的数字 / 模拟 / 封装以及签核技术,实现了让用户可以在系统规划和实现流程的早期就进行系统分析和设计迭代,达到系统 PPA 驱动的高性能 3D-IC 设计效果,同时可以避免高昂的过度设计成本。

注册成功且通过 Cadence 审核的用户可获得完整版 PPT 资料。审核通过后 Cadence 会将 PPT 发送至您的邮箱,提供您的公司邮箱地址通过审核的几率更大哦!

Cadence Integrity 3D-IC 平台提供了一个高效的解决方案,用于部署 3D 设计和分析流程,以实现强大的硅堆叠设计。该平台是 Cadence 数字和签核产品组合的一部分,支持 Cadence 公司的智能系统设计战略(Intelligent System Design™),旨在实现系统驱动的卓越 SoC 芯片设计。