文档中心

Allegro高级教程之实时DFA间距检查与应用设计专题

DFA(Design For Assembly)称为装配设计,是指通过对电子产品进行装配分析,制定出合理的元件装配规则,从而提高设计效率、减少生产成本的设计方法。Allegro PCB Editor提供了布局过程中实时的封装-封装的间距检查,分为side to side、side to end、end to end、end to side四种检查模式。对于复杂的电路板,实时的DFA间距检查与分析有助于提高生产力和生产效率,而且能够降低对计算机辅助制造系统(CAM)的依赖。本文主要介绍如何在Allegro PCB Editor中实现DFA设计与分析。

关键字:Allegro PCB、Allegro教程、DFA、DFA检查

PSpice模型创建与应用实例

PSpice为用户提供了模型转换与编辑工具:Model Editor,用户自己下载的模型参数文件可以通过Model Editor转换成PSpice的模型文件,并且可以建立相应的模型符号。本文以intersil公司的ISL28114元件模型为例介绍如何将下载的Spice模型文件导入到PSpice模型库中,并对模型进行模拟仿真。

一个完整的模型创建与应用实例包括以下几步:

1、导入模型文件

2、建立模型符号

3、应用模型进行仿真

关键字:PSpice仿真、PSpice模型、PSpice建模、PSpice model、模型创建

Allegro design entry HDL_datasheet

Cadence Allegro Design Entry HDL系统互连设计平台可以为PCB设计、封装和系统级封(SiP)提供完整和可扩展的技术。设计创建于原理图,也可以创建于电子表格和HDL(Verilog语言)。Cadence设计创建技术与Allegro PCB Editor和Allegro约束管理系统紧密集成,可以为约束驱动的PCB设计提供强健和高度定制化的解决方案。它支持企业吸收和建立含有多种特性和实用工具,可加速PCB设计创建。除典型的复制/粘贴特性外,它还支持页面级、模块级、设计级设计复用。多个用户可以同时进行设计,在对时间要求高的项目上赋予了设计团队亟需的灵活性。与Cadence Incisive仿真器和Cadence Ps-pice®仿真的集成,可分别实现数字和模拟仿真。

Allegro PCB SI_datasheet

Cadence PCB 信号完整性(SI)与电源完整性(PI)分析技术提供了可调整的、节约成本并且支持前仿真和后仿真的系统互联设计和分析环境。他们提供了在电路板、多层板和系统级的高级分析。Cadence PCB SI 和PI 产品与Cadence PCB 编辑器、Cadence Allegro PCB 布线器、Allegro Design Entry HDL 和Allegro System Architect 紧密结合,能够实现端到端、约束驱动的高速PCB 系统设计。Cadence PCB SI 让设计师能够在整个设计过程中解决高速问题,从而能够解决设计密度、复杂度和高速边缘变化率的不断提高而带来的问题。这种方法让设计团队不用在设计过程的后期进行耗时的仿真̶修复̶仿真的迭代。它还让设计师通过以制造容限来建立拓扑和模型进行分析从而使得产品的电汽性能最优化以及成本最小化。Cadence PCB SI 让用户能够在布线选择(规则)中,对电汽性能和可靠性的影响进行利弊权衡。一旦确定,会以这些最优约束来驱动PCB 的物理布局和布线。综合的设计和分析环境让设计师不用转化设计数据库进行仿真。设计师还可以通过考虑封装设计对芯片间传输信号整体表现的影响,从而解决时序容限不断缩小的问题。该综合流程让设计师能够轻松执行对复杂高速PCB 系统的布局前和布局后的模型提取与仿真验证。

Cadence Allegro PCB Design_datasheet

Allegro PCB Designer是可扩展的,经过反复验证的PCB设计工具,可以适应于对缩短设计周期和可预测设计结果所带来的技术和设计方法的挑战。产品由Base模块和Option附加模块组成,PCB Design Solution通过一个完全集成的设计流程进行PCB Layout设计。Allegro PCB Designer(Base模块)包含一般的、通用的约束管理解决方法、PCB Editor、自动/交互布线器和用于机械制造的CAD接口。PCB Editor提供了完整的布局布线环境--从基本的PCB平面规划(Floor-planning)、布局、布线到布局复用(Placement Replication)、高级互连设计规划(Interconnect Planning)--从简单设计到复杂设计。

OrCAD教程之关于建立BOM时不需要上件/插件(no_plug_in)的元器件管理

对于有些线路图,虽然有些器件加在线路图中,但是生产时有可能是不焊的,或者预留的,在出BOM清单时,不希望这些器件也在清单中,针对这类设计,Capture如何实现呢?本文就为大家介绍Capture中对于不同机种元件不插件(不上件)的设计方法。

关键字:OrCAD Capture、OrCAD教程、不插件、不上件、 variant BOM 元件预留

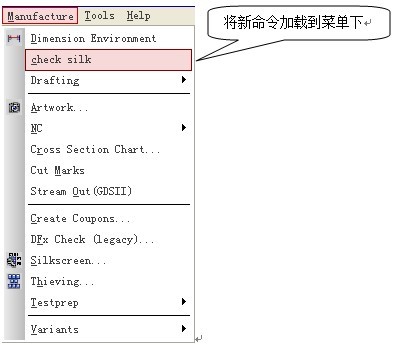

Allegro高级教程之Load New Skill in Allegro(加载新命令)

Cadence为用户提供了加载菜单命令的强大功能,用户可以自己编制新命令,加载到软件中,还可以将新命令加载到Allegro的菜单中。本文以新增文字重叠检查(check_silk)为例,介绍如何加载新的命令,并且将新命令添加到“Manufacture”菜单下:

关键字:Allegro PCB、Allegro教程、load new skill、加载命令、创建新命令

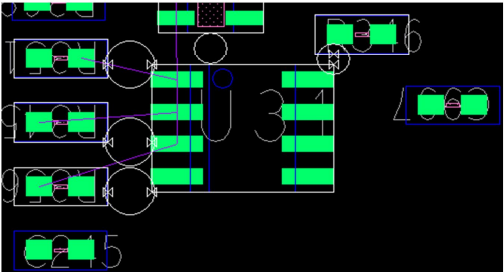

Allegro高级教程之Design Partition(分板设计专题)

Allegro PCB为用户提供了PCB分板设计功能,即将设计分为多个部分,由团队中的不同人员分别进行编辑。多个设计人员共享一个layout并通过独立的模块数据库单独工作,分板设计完成后合并各分板。设计可以纵向划分(按不同的section),也可以横向划分(按不同的layer)。每一个设计人员都可以看到所有的分板,并且能更新视图来监控其它设计部分的状态和进度。这种分板设计可以大幅缩短整体设计的周期,加快设计进程。

关键词:Allegro PCB、Allegro教程、分板设计、并行设计、Design Partition 、TeamDesign