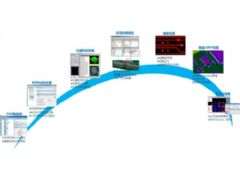

IC-Package-PCB系统研发设计综合解决方案

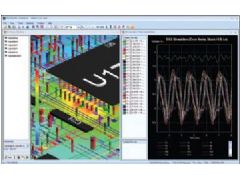

数模混合电路系统设计仿真

耀创科技提供基于Cadence/AMS PSPICE数模混合电路仿真验证解决方案,同时提供相应的技术和工程服务培训,帮助客户建立设计初期的仿真验证综合方案,加快设计周期。

结合SPICE/Verilog/VHDL数字验证技术,将数字电路技术和模拟器件行为有效的结合仿真,可以大大提高设计效率,帮助工程师在设计早期就可以发现和预测产品的性能好坏。PSpice仿真技术能够仿真大量的设计和设计单元,包括电源,滤波器,放大器,数字逻辑门解码电路,PWMs,晶体管,MOSFETs,非线性磁芯,压敏电阻,稳压器,和二极管。PSpice提供了集成的仿真与波形分析仿真环境,并且在同一个图形窗口,同一参考时钟轴上显示数字模拟信号仿真结果。使用PSpice技术,工程师基于“What if“方式可以分析和探测电路性能和功能的关系、仿真复杂的混合信号电路设计。从而减少了在设计早期需要投入昂贵的仪器费用,仅仅通过探针即可实现波形的动态显示,不管是时域还是频域波形。

耀创科技曾协助客户完成诸如输入输出滤波器优化仿真、PLL锁相环设计仿真、多通道A/D转换及控制电路仿真、低噪声电路分析、各种波形发生器(正弦波、三角波)、特殊激励发生器、基准源设计等,赢得了客户的高度认可。

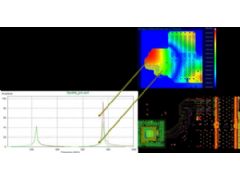

先进系统封装设计SiP

耀创科技提供IC封装设计和仿真验证的一体化Front To End解决方案。

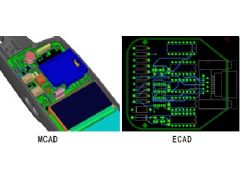

基于Cadence Allegro SiP和Allegro Package Designer(APD)及Sigrity仿真的解决方案主要面向电子设计创新领域以及越来越多的要求产品小型化、轻薄化、高集成度和高可靠性的市场需求。

Allegro SiP和Sigrity芯片先进封装设计解决方案涵盖了封装设计、封装模型提取、电性能电源完整性、信号完整性分析及热分析等,为客户提供了封装设计和仿真所需要的全套工具。适用于引线框架封装,键合飞线(Wire Bond)和倒装芯片(Flip Chip)等基板封装,晶圆级封装(WLCSP),系统级封装(SIP_System In Packge)等各种形式的封装形式,在满足现阶段3D封装的情况下,又将推出更高端应用于TSV封装设计的解决方案,为IC封装设计提供业界最全面的设计与分析解决方案,满足新一代智能手机、平板电脑、超薄笔记本电脑的需要。