文档中心

Sigrity Aurora

Cadence SiP Layout

OrCAD PSpice Designer

OrCAD PSpice Designer是一款高性能的、经过工业级设计验证的数模混合电路仿真和波形查看仿真工具,作为全球最流行的、通用的、元器件和IC模型可扩展的混合电路仿真器,OrCAD PSpice软件仿真技术适用于许多行业领域的产品设计中,如航空航天、医疗、电力电子和汽车等行业,也广泛应用于一些研究机构作为设计参考实现来使用。它能够模拟你的设计从简单的电路,复杂的电路,功率电源系统到射频系统和定制的IC设计。内置数学函数,ABM行为建模,电路优化,机电系统联合仿真,其电路模拟仿真环境已经远远超过一般意义的电路仿真软件。

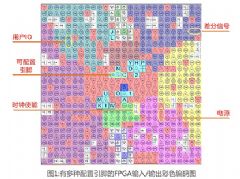

Cadence OrCAD FPGA System Planner

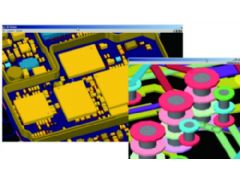

Allegro PCB Design Solution

OrCAD PCB Designer

OrCAD PCB Designer提供了PCB从概念到生产所有环节所需要的设计解决方案,它具有灵活可扩展特点且经过产品设计验证,市场覆盖了从智能控制、工业机器人、汽车和航空航天等,OrCAD PCB Designer Standard和OrCAD PCB Designer Professional产品均可帮助客户在当今的电子市场保持一定的竞争力。OrCAD PCB 设计解决方案可以缩短设计周期,挑战新兴的软硬结合基板设计,可大大加快产品上市时间,实现设计目标。

Allegro Pspice Simulator

在较大的电路设计系统上,PCB设计团队需要快速、可靠的仿真软件来实现对设计的收敛。Cadence Allegro PSpice®System Designer提供PCB设计人员的仿真技术是把电路仿真环境与PCB布局布线设计环境完全集成在一起,构成一个完整的统一集成环境。设计师通过集成模拟和事件驱动数字仿真,可以在不牺牲精度的情况下提高仿真速度。同时,使用PSpice高级分析功能,设计师可以最大限度的提高电路的性能、提高成品率和可靠性。