文档中心

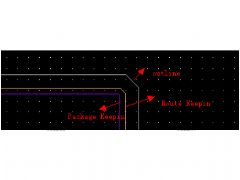

Allegro高级教程之高速设计规则约束管理

对于高频电路而言,势必会产生传输线效应和信号完整性问题,怎样利用PCB的布线来保证整个高频系统实施是设计关键。为了避免高速电路的传输效应,必须严格控制关键网络的走线长度,合理规划走线的拓扑结构。本文就针对高速电路中的布线规则约束做一个系统的介绍。

关键字:Cadence教程、Allegro教程、Allegro PCB、PCB设计、PCB约束、高速电路、高速PCB、线长控制、等长控制、延迟设置、网络拓扑结构、阻抗匹配

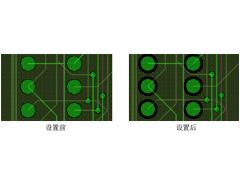

Allegro高级教程之元件嵌入式布局解决方案(Embedded Components)

Allegro中元件嵌入式布局设计分为以下几个步骤:

1、设置Embedded_Placement属性,只有附带该属性的元件才能进行嵌入式布局;

2、设置嵌入式板层;

3、设置嵌入式摆放约束规则;

4、实现元件嵌入式布局。

关键字:Cadence教程、Allegro教程、Allegro PCB、PCB设计、元件嵌入布局、元件内嵌、微型化电路板设计、高密度电路板设计、Embedded Components

Allegro基础教程之Allegro后处理方法之丝印(Silkscreen)

为了方便PCB板的安装,所有元件、安装孔都要有对应的丝印标号。本文主要介绍Allegro中丝印的生成方法。

关键字:Cadence教程、Allegro教程、Allegro PCB、PCB设计、丝印、Silkscreen

Allegro基础教程之测试点生成和添加方法

电路板加工完成后需要进行测试,即检测所有元件引脚间的连接,确保没有短路和断路的情况出现。本文主要介绍Allegro中测试点的添加和测试夹具的输出方法。

关键字:Cadence教程、Allegro教程、Allegro PCB、PCB设计、测试点、testpoint

Allegro基础教程之Allegro PCB设计输出流程介绍

电路设计没有问题,就可以进行PCB的后续输出工作,即输出供制板厂家制板用的钻孔文件和光绘文件了。本文主要对Allegro PCB的输出流程做简要介绍,主要包括钻孔文件和光绘文件的设置和输出。

关键字:Cadence教程、Allegro PCB教程、Allegro PCB、PCB设计、钻孔文件、钻孔图、光绘文件、silkscreen、artwork

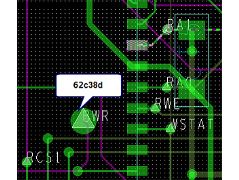

Allegro基础教程之原理图和PCB同步交互模块

Allegro可以实现原理图和PCB的实时交互,用户可以实时地对应原理图和PCB的相应元件,有助于PCB的布局布线工作。

在PCB设计过程中,如果对PCB做了修改,还可以通过Back annotation使原理图设计和PCB设计保持同步,这一过程又称为反标。可以执行反标的对象包括:

更改了的属性(property changes );

更改了的封装标识(ref-des changes);

交换了的引脚或功能模块(pin and gate swaps)

关键字:Cadence教程、Allegro教程、Allegro PCB、PCB设计、Back Annotate、Back Annotation、反标

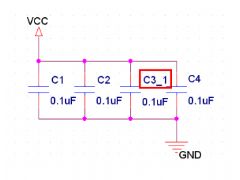

Allegro基础教程之覆铜设计指南

所谓覆铜,就是将PCB上闲置的空间作为基准面,然后用固体铜填充。覆铜的意义在于减小地线阻抗,提高抗干扰能力,降低压降,提高电源效率。本文对Allegro中的覆铜设计做一个系统介绍,主要内容包括:

覆铜的基本概念;

覆铜参数的设置;

创建铜皮;

分割铜皮。

关键字:Cadence教程、Allegro教程、Allegro PCB、PCB设计、覆铜、铺铜

Allegro基础教程之Allegro PCB辅助命令操作汇总

Allegro为用户提供了多种辅助命令操作,在PCB设计过程中用户可以更加方便、灵活实现某些辅助功能,本文主要介绍以下几种辅助命令:

Show element

Z-Copy

Edit-Change

Highlight/Dehighlight

Shadow mode

Parasitic

3D View

Reports

关键字:Cadence教程、Allegro教程、Allegro PCB、Show element、Z-Copy 、Edit-Change、Highlight/Dehighlight、Shadow mode、Parasitic、3D View、Reports