OrCAD PCB Designer with PSpice

Cadence® OrCAD® PCB Designer with PSpice套装产品包含将PCB从概念到产品化过程所需的一切工具,它拥有一套完整的集成化设计流程-包含设计输入、元器件工具、PCB编辑器、自动/交互布线器,模拟仿真器,以及与制造和机械CAD相关的接口。电路设计及PCB Layout套装产品OrCAD PCB Designer with PSpiceCadence OrCAD PCB Designer with Pspice是经过验证的、可扩展的、成本有效的PCB编辑和布线工具。

关键技术:

- Cadence OrCAD Capture,用于高效快速且经济地输入、修改和验证复杂系统设计的全面解决方案;

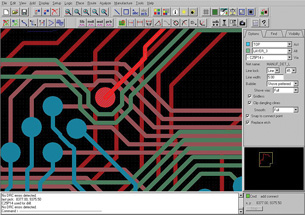

- Cadence OrCAD PCB Editor,基于Allegro技术,具有直观、易用、驱动约束的环境,可创建和编辑各种复杂程度的PCB;

- Cadence SPECCTRA® for OrCAD,自动和交互PCB布线的领先解决方案;

- Cadence PSpice® AD,支持数字接口和仿真验证的全功能模拟仿真器;

优势:

- 经过验证的、可扩展的、成本有效的PCB编辑和布线工具,可满足不断发展的设计需求;

- 提供完整的交互环境;

- 包含完整的功能套件;

- 提供从前端到后端的约束管理系统,用于约束创建、管理和验证;

- 通过集成应用功能模块来有效提高设计效率;

- 无缝隙的前端到后端集成设计环境;

功能特点:

Design Capture Technology

OrCAD Capture 提供快速有效地输入、修改和验证复杂系统的全面解决方案。EMATIC EDITING(原理图编辑)用户可通过整套功能库放置和连接元件。 PROJECT MANAGEMENT(项目管理器)用户可在整个设计流程中收集和组织项目所需的所有资源。

HIERARCHICAL DESIGN AND REUSE(分层设计和重复使用)让用户无需通过多次拷贝来重复使用某个子电路,而是通过分层块简单地多次引用该子电路即可。

LIBRARIES AND PART EDITING(库和器件编辑器)可以通过Capture用户界面直接访问Orcad的库编辑器。可以在库中创建和编辑器件,当然也可以在原理图页中创建和编辑器件,而不必中断工作流程。

EASY DATA ENTRY(数据输入)可以方便地定义器件、管脚和网络数据,让设计者通过电子表格编辑器轻松且快速的进行诸如元器件、网络、管脚、图纸规格型号或子节点属性的编辑和修改。

PCB Editor Technology

功能特点

| 无限制数据库 | 所见即所得的铜箔与DRC检查 |

| 网表/交叉布局/交叉查询 | 交互式布线和编辑 |

| 焊盘和封装符号编辑器 | 自动生成丝印 |

| 支持层分割 | 可定制/自动生成钻孔符号/钻孔数据输出 |

| 支持各种过孔和盲埋孔设置 | 支持SKILL程序, 宏命令和脚本运行 |

| 自动布局/快速布局/统一编辑规划 | 可创建多种装配图形 |

| 支持IFF文件导入 | 可生成多种类型BOM单 |

| 支持创建2-D草图和尺寸标注 | 动态覆铜方式可以实时更新铜箔外形 |

| 支持输出Gerber 274X, 274D等光绘文件 | 支持CAD接口–DXF (Ver.14), IDF (Ver.2 and 3) |

| 可反复进行UNDO/REDO操作 | 支持其他PCB接口– OrCAD Layout, PADS (Ver.5), P-CAD (Ver.8) |

| 支持多种数据格式Valor ODB++, ODB++(X)等 | 约束管理器(含物理规则,间距规则,基本属性和DRC) |

| 输出基于HTML的报告 | 可人工添加测试点 |

PCB EDITING ENVIRONMENT(PCB编辑环境)提供了操作方便,易学易用,约束驱动式设计环境,可以满足从创建简单PCB设计到复杂多层PCB设计的要求。

CONSTRAINT MANAGEMENT(约束驱动管理)系统通过电子表格界面来显示物理和间距规则,用户可以在表格中定义、管理和验证不同的规则。

FLOORPLANNING AND PLACEMENT (布局规划与放置)由约束和规则驱动布局。

INTERACTIVE ETCH EDITING (交互布线)提供自动化控制维护用户控制,同时最大限度提高布线效率。

Dynamic push-and-shove capabilities make interactive editing easy

DYNAMIC SHAPES technology(动态覆铜技术)提供了实时的铜箔分布和自动避让功能,铜箔参数可以在三个不同的优先级中起作用。 PCB MANUFACTURING features (PCB制造)包括了一套完整加工流程输出,从光绘工具、裸板制造到测试输出等,加工文件支持多种类型诸如Gerber 274x,钻孔文件和测试文件等。

PCB Autorouter Technology

功能特点

| 最多支持到6层布线 | 交互式过孔查询 |

| 基于覆铜或栅格方式的自动布线 | 交互式布线和自动推挤 |

| 表贴封装形式扇出 | 交互式布线规划 |

| 支持单一或同组网络布线 | 支持在线自动执行DRC检查 |

| 支持管脚交叉网格设置 | 元件翻转、任意角度旋转、对齐、推挤和移动 |

| 45度 ECO布线 | 布局布线密度分析 |

| 存储器走线扇出模式(表贴或钻孔) |

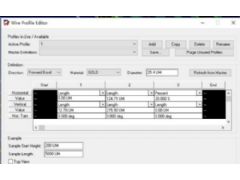

AUTOMATED INTERCONNECT ENVIRONMENT(自动互连环境)强大的自动化功能解决了复杂交互布线的挑战。

AUTOROUTING(自动布线)自动布线快,布通率高,设计的布线算法可应对大范围的PCB互连挑战布线算法被用来设计处理更广泛的PCB板连接之间带来的挑战-不管是简单还是复杂,低密度还是高密度。

INTERACTIVE ROUTE EDITING(交互式布线)简化和加快线编辑流程。当重新布线时,会对已经存在的互连线或导体进行自动推挤或沿靠近的元件pin脚绕行。

PLACEMENT EDITING(布局编辑)允许设计人员快速放置元器件,同时预估空间、逻辑流程和元件密度等,该操作可在布线前或者必要时在布线流程中进行。

PCB EDITOR INTEGRATION(集成PCB编辑)通过PCB editor界面,所有设计信息和约束自动进入布线器,一旦布线结束,所有布线信息自动反馈到PCB editor。

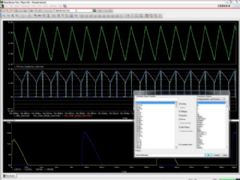

Advanced Simulation Technology

PSpice A/D是全功能的模拟和数模混合仿真器,可以解决实际设计中带来的挑战,支持从高频系统到低功耗IC设计仿真。

功能特点:

| 设计输入和编辑 | 支持模型编辑 |

| 创建激励源 | 创建行为级模型 |

| 进行电路模拟 | 磁性元件编辑器 |

| 数模混合信号模拟 | 数据加密 |

| 通过图表显示数据和结果 | 集成SLPS功能(任选) |

| 模型库 | 电路仿真节点检查可重新启动 |

OrCAD Signal Explorer

Cadence Allegro Design Authoring

Allegro Pspice Simulator

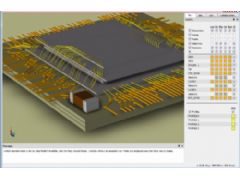

在较大的电路设计系统上,PCB设计团队需要快速、可靠的仿真软件来实现对设计的收敛。Cadence Allegro PSpice®System Designer提供PCB设计人员的仿真技术是把电路仿真环境与PCB布局布线设计环境完全集成在一起,构成一个完整的统一集成环境。设计师通过集成模拟和事件驱动数字仿真,可以在不牺牲精度的情况下提高仿真速度。同时,使用PSpice高级分析功能,设计师可以最大限度的提高电路的性能、提高成品率和可靠性。

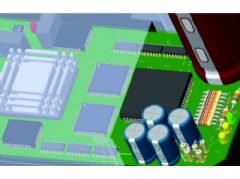

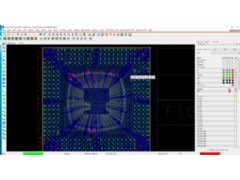

OrCAD PCB Designer

OrCAD PCB Designer提供了PCB从概念到生产所有环节所需要的设计解决方案,它具有灵活可扩展特点且经过产品设计验证,市场覆盖了从智能控制、工业机器人、汽车和航空航天等,OrCAD PCB Designer Standard和OrCAD PCB Designer Professional产品均可帮助客户在当今的电子市场保持一定的竞争力。OrCAD PCB 设计解决方案可以缩短设计周期,挑战新兴的软硬结合基板设计,可大大加快产品上市时间,实现设计目标。

Allegro PCB Design Solution

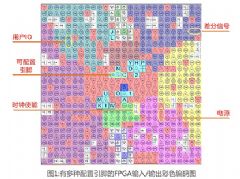

Cadence OrCAD FPGA System Planner

OrCAD PSpice Designer

OrCAD PSpice Designer是一款高性能的、经过工业级设计验证的数模混合电路仿真和波形查看仿真工具,作为全球最流行的、通用的、元器件和IC模型可扩展的混合电路仿真器,OrCAD PSpice软件仿真技术适用于许多行业领域的产品设计中,如航空航天、医疗、电力电子和汽车等行业,也广泛应用于一些研究机构作为设计参考实现来使用。它能够模拟你的设计从简单的电路,复杂的电路,功率电源系统到射频系统和定制的IC设计。内置数学函数,ABM行为建模,电路优化,机电系统联合仿真,其电路模拟仿真环境已经远远超过一般意义的电路仿真软件。

Cadence SiP Layout

OrCAD Sigrity ERC

Sigrity™ ERC(电气规则检查)拥有电气规则检查的功能,这能让电路板设计者在没有仿真模型或者足够的信号完整性专业能力的情况下, 简单而快捷地分析信号质量的问题和原因。

由于使用了工业和市场领先的Cadence Sigrity技术, Sigrity ERC超越了简单的基于几何的设计规则检查, 分析到那些通常只能被专业SI/PI工具发现的信号质量问题。

OrCAD PCB Productivity Toolbox

OrCAD PCB Productivity Toolbox提供了一套实用工具,旨在通过启用或简化当前常见或新兴的许多设计任务来提高PCB设计人员的工作效率,工具箱实用程序直接集成到OrCAD PCB编辑器环境中,也遵守其一贯的执行风格,对设计人员的工具使用习惯几乎没有影响。

Cadence OrCAD Capture CIS

Cadence OrCAD Capture CIS全球应用最多且经过生产验证的原理图输入工具和强大的元件信息管理系统。Cadence OrCAD Capture CIS集成强大的原理图设计功能,其特点主要是具有快捷的元件信息管理系统(CIS),并具有通用PCB设计入口。扩展的CIS功能可以方便地访问本地元件优选数据库和元件信息。通过减少重新搜索元件信息或重复建库,手动输入元件信息,维护元件数据的时间,从而可以提高生产率。无论是设计全新的模拟,数字,或混合信号电路,还是修改现有电路板的电路原理图,或进行层次结构电路图设计,OrCAD Capture CIS提供电路设计从构思到生产所需的一切。

Cadence OrCAD Capture原理图输入

OrCAD Capture CIS

Orcad Capture CIS/ Allegro Design Entry CIS 16.6新增功能列表,如下,具体内容及相关操作见技术白皮书。

1. 在Capture下运行SigXplorer进行信号完整性分析

2. 从菜单中放置PSpice元件

3. 配置菜单和工具栏

4. 设计和库文件保存功能的扩展

5. 查找功能的扩展

6. NetGroup使用模型的升级

7. 查询并替换Off-Page Connector(端口连接符)

8. Cache更新扩展

9. 为元器件设置 User Assigned Flag.

10. 实现同一个设计中不同层次电路图的自动顺序编号

11. 数据库压缩与处理能力的增强

12. 打开由低版本软件生成的设计文件

13. 关闭所有标签页

14. DRC功能扩展

15. Project SaveAs功能的扩展

16. 学习资料

II. Capture 16.6中已经解决的重要问题

1、CCR 1065649: 兼容16.5和16.3版本问题

2、CCR 730224:对库文件进行了更新但没有更新信息

3、CCR 724738:Update/Replace Cache对用户定义的引脚形状无效

OrCAD PCB Designer-U-Creative.pdf

OrCAD PCB Designer-U-Creative.pdf