Cadence Sigrity Aurora 为 PCB 设计前、设计中和布局后提供传统的信号和电源完整性 (SI/PI) 分析,结合 Cadence Allegro PCB 编辑和布线技术,Sigrity Aurora用户在设计初期就可以使用 “What-if” 探索环境进行分析,从而获得更准确的设计约束并减少设计迭代。

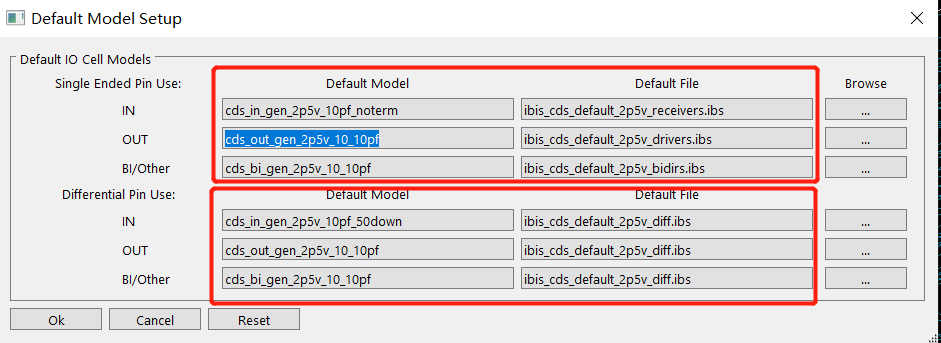

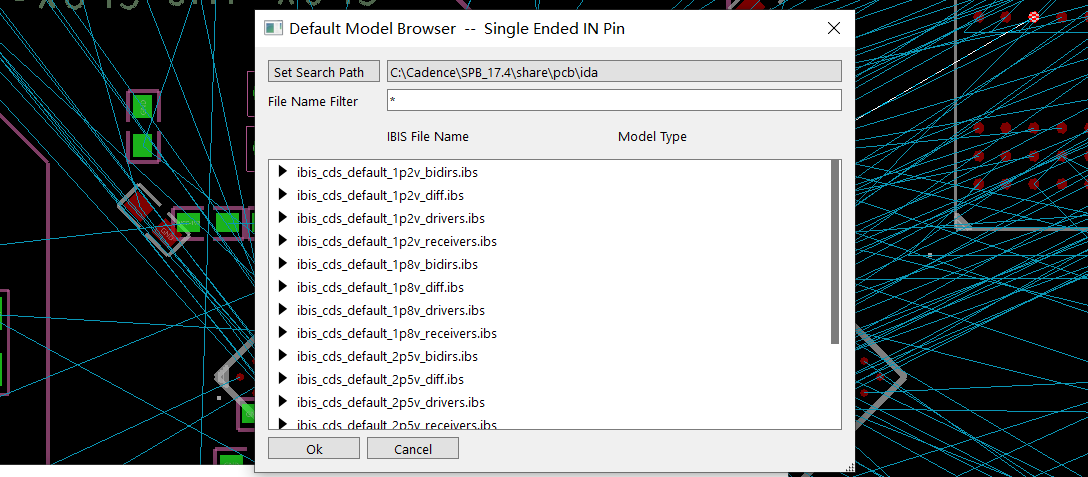

Sigrity Aurora 直接读写 Allegro PCB 数据库,可快速准确地整合设计和分析结果。它提供了一个基于 SPICE 仿真器和获得专利的 Sigrity 嵌入式混合场求解器,用于二维和三维结构提取。同时支持兼顾电源影响(Power-Aware)的 IBIS 模型,如需要还支持晶体管级别的模型。高速信号可以在布局阶段中或布局阶段后,对比备选方案进行研究,以便对所有相关信号进行全面分析。

在最新的 SPB 17.4 版本中,Cadence Sigrity Aurora 主要在以下几个方面对互连建模的仿真功能进行了更新:

- 支持对未布线网络的拓扑提取及建模:支持布线前按照预拉线曼哈顿长度拓扑提取,并进行信号互连搭建,进行信号完整性仿真分析。

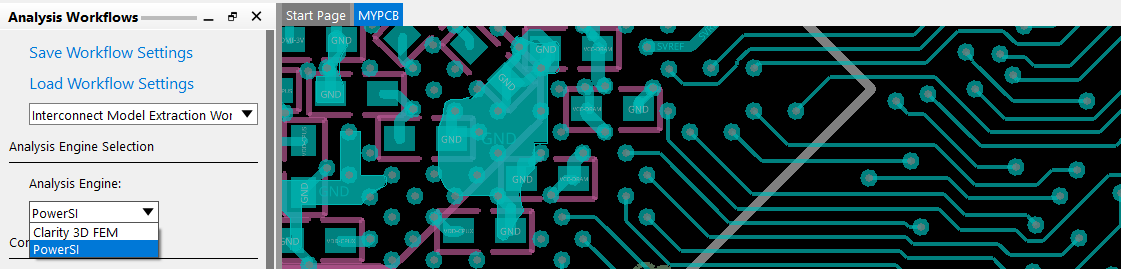

- 支持 Clarity 3D Solver 和 Sigrity PowerSI 引擎直接集成:在 Aurora 环境中,可以通过选择需要提取的网络调用 Clarity3D Solver 和 Sigrity PowerSI 引擎进行 S参数 的仿真建模。

- IR Drop 直流电压降仿真支持自动剪切功能:自动剪切功能,可以加快仿真的速度,针对大型 PCB 的区域分析及部分电路仿真提升仿真的速度。

- 新增生成同轴电缆和双绞线电缆的模型:生成同轴电缆和双绞线建模,支持框架及及参数建模和自定义参数建模的办法,通过修改编辑支持直接进行信号互连拓扑及信号互连仿真。

Sigrity Aurora互连建模仿真亮点——

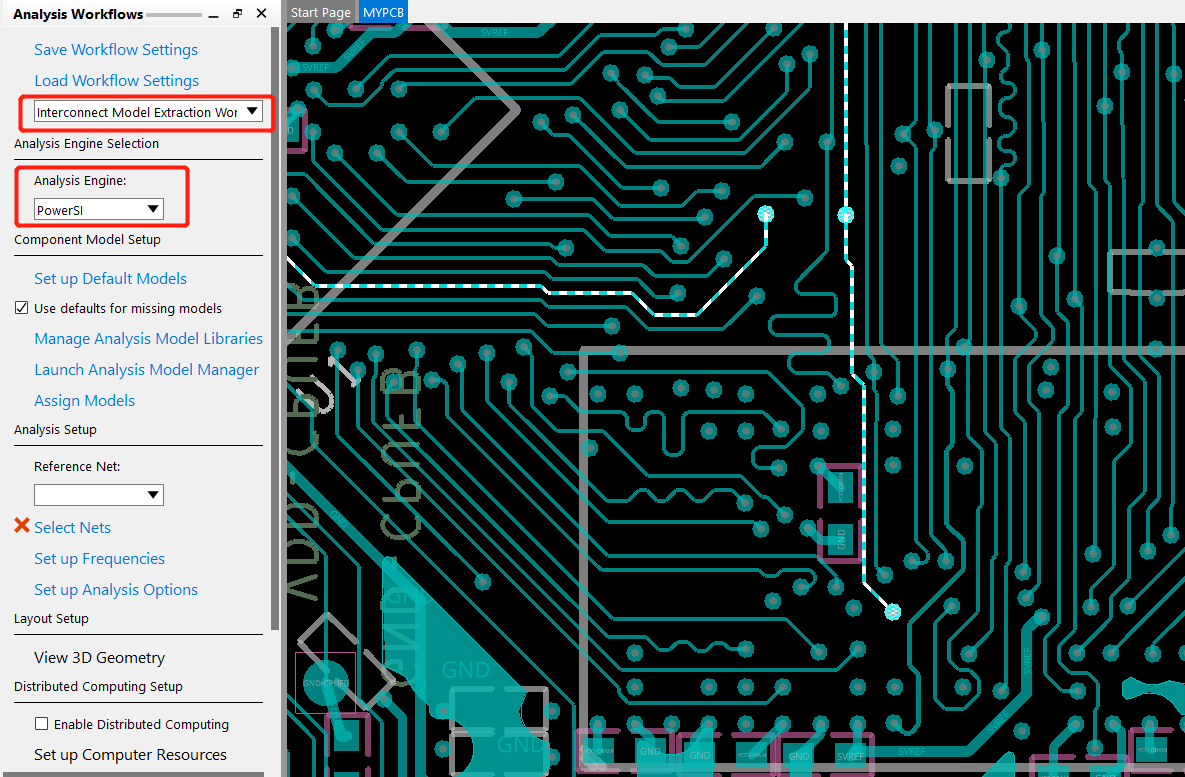

#2 支持 Clarity 3D Solver 和 Sigrity PowerSI 引擎直接集成

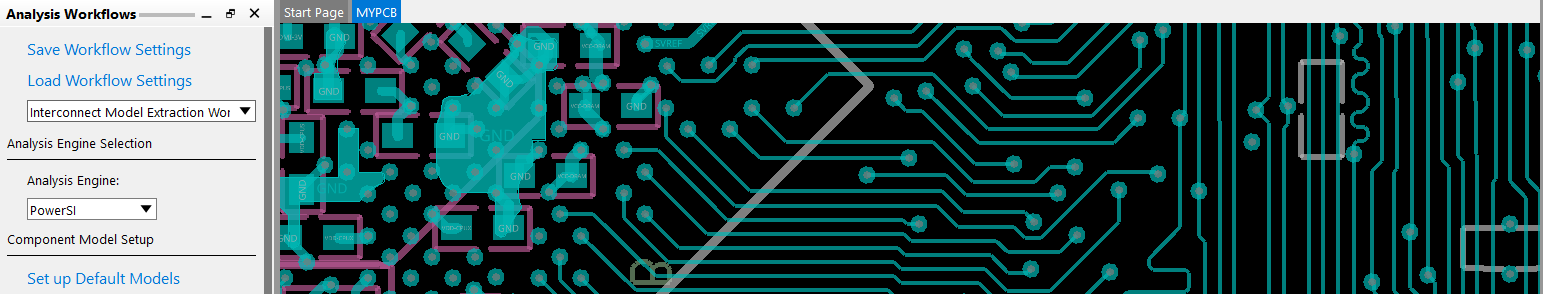

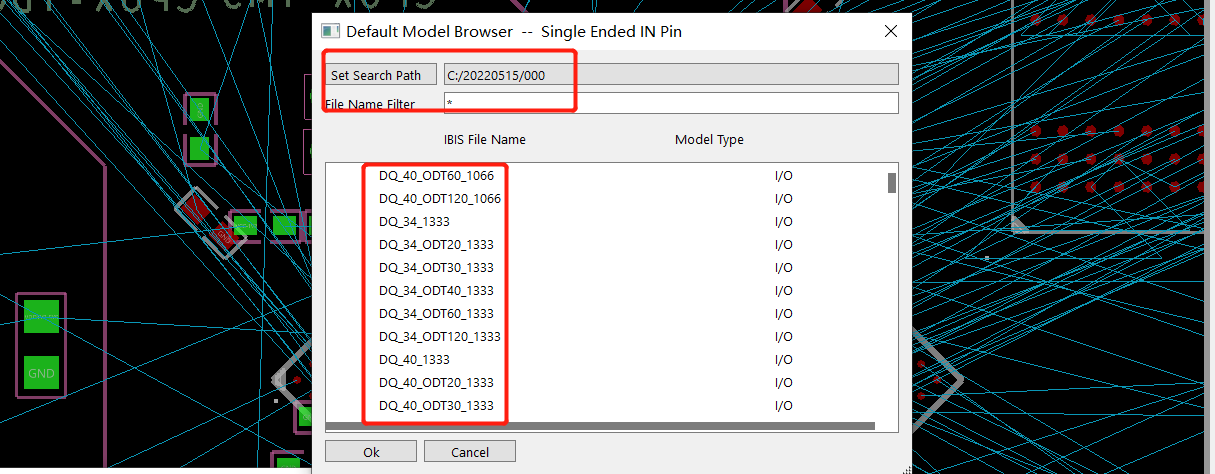

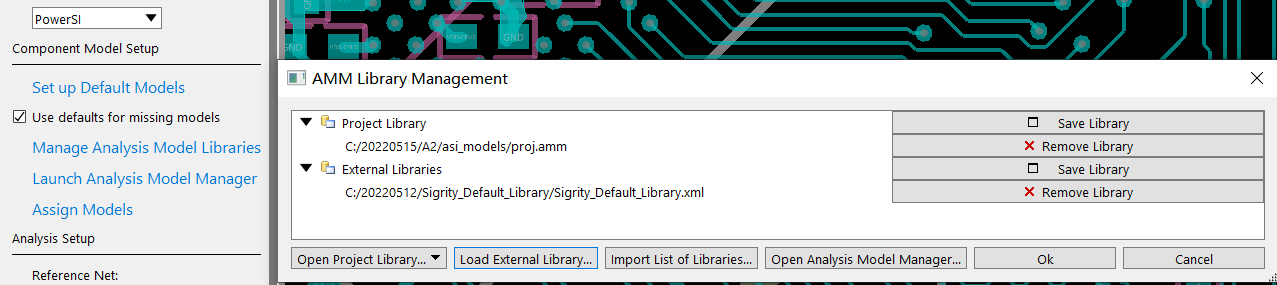

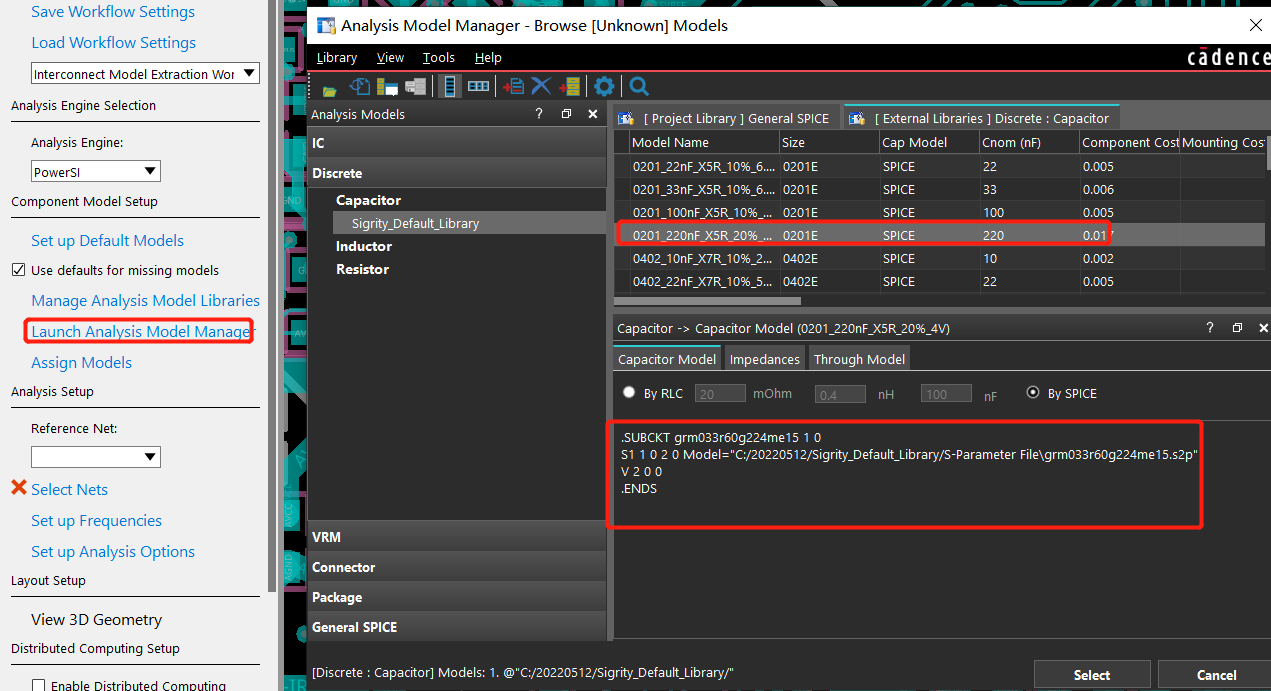

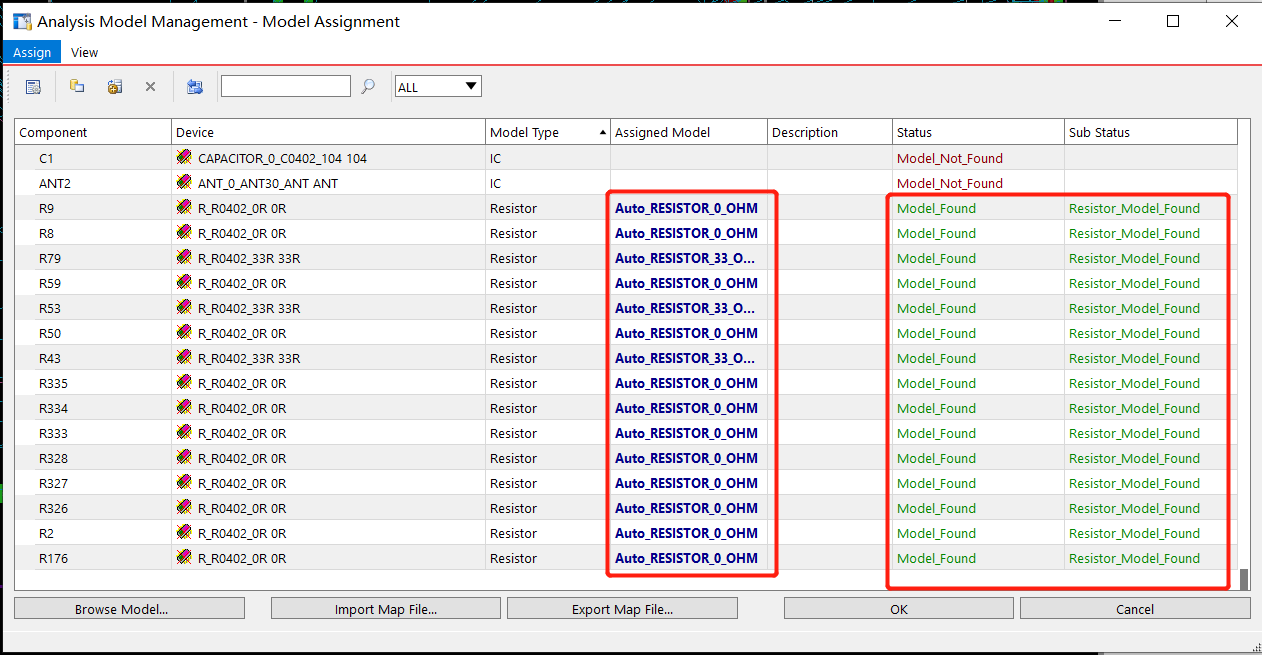

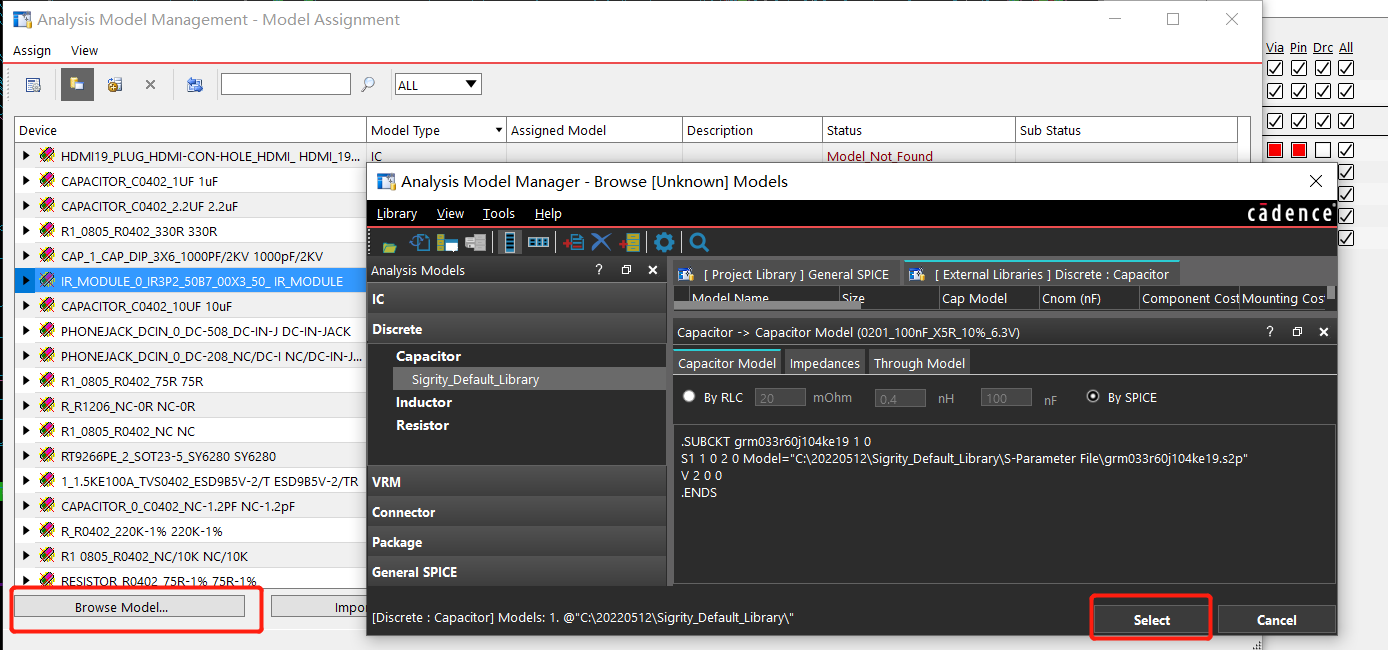

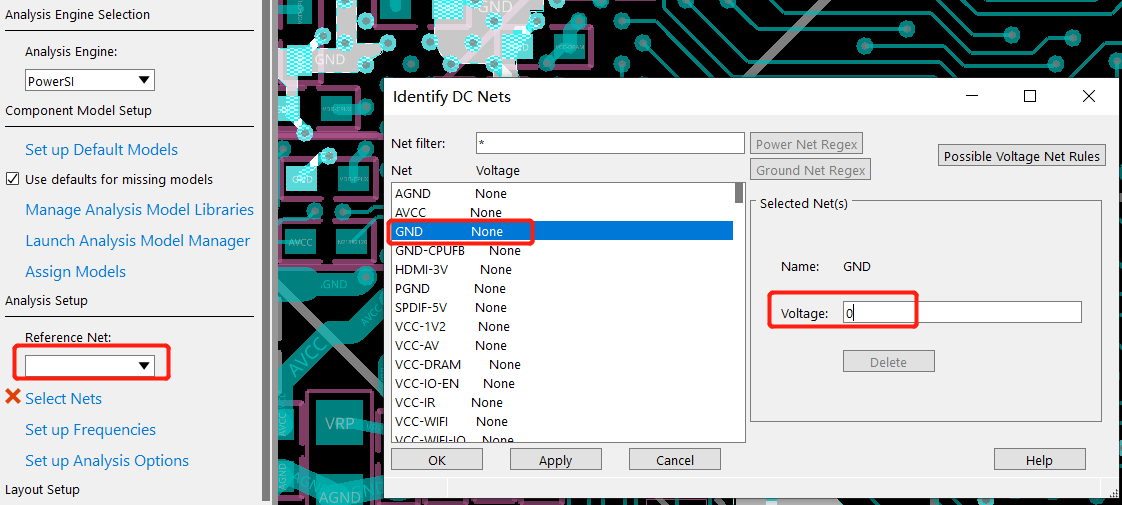

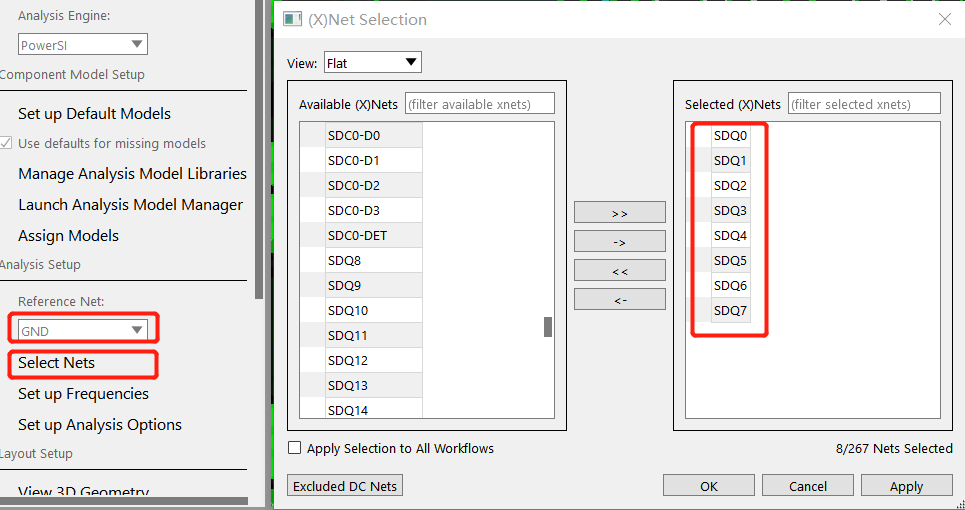

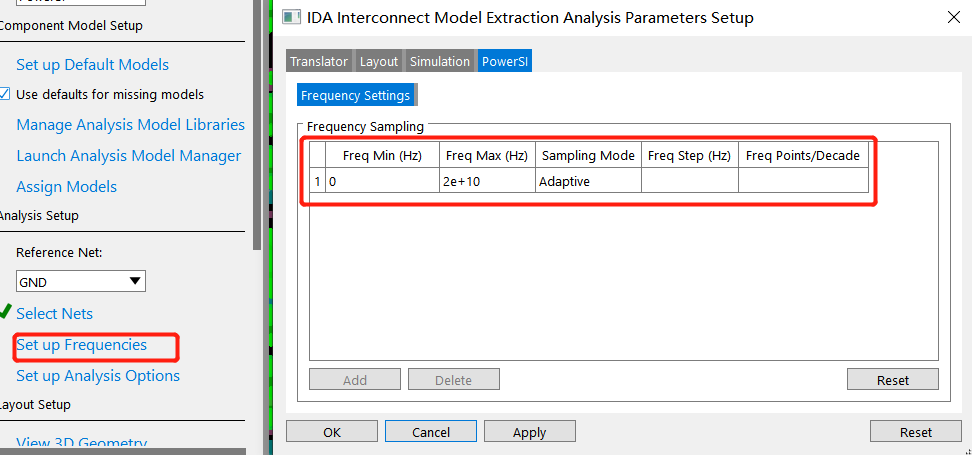

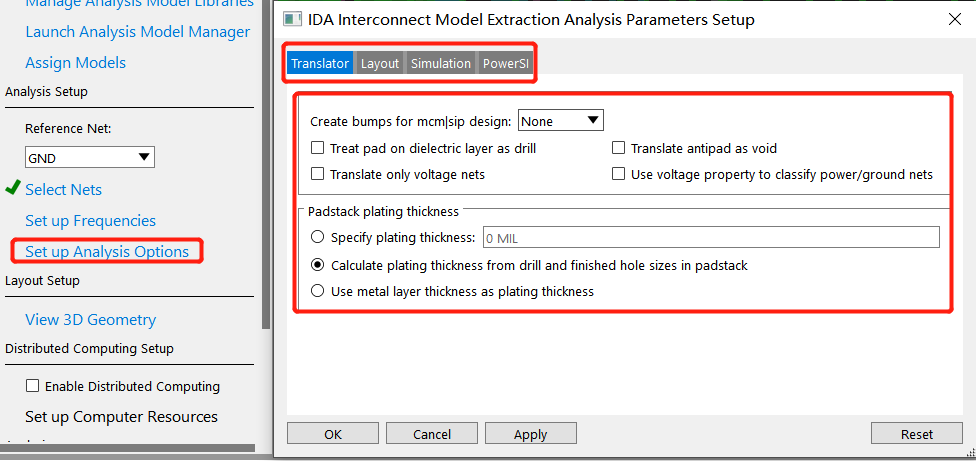

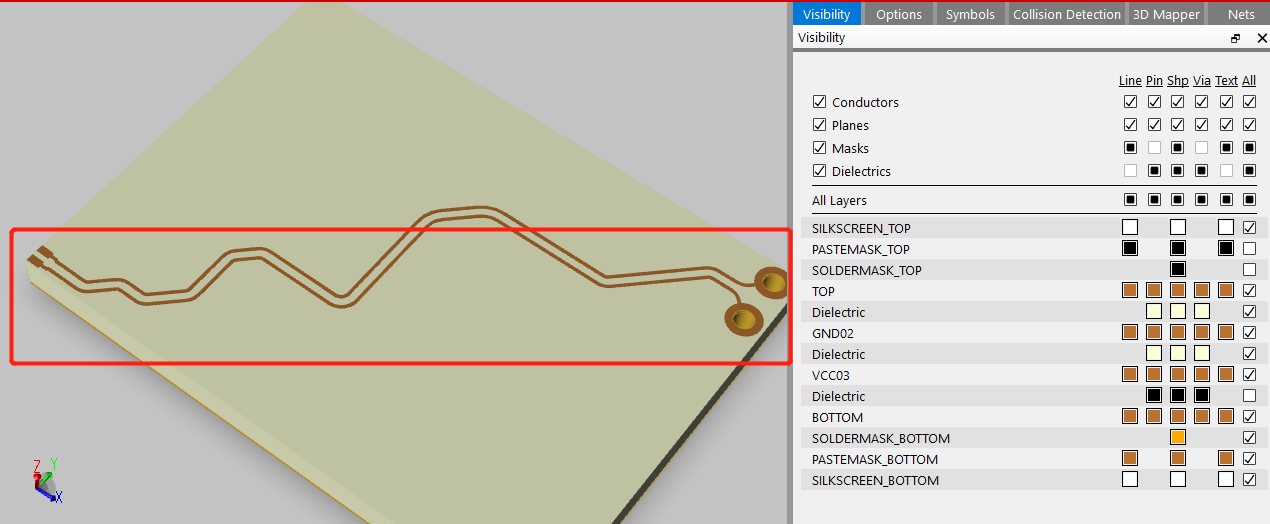

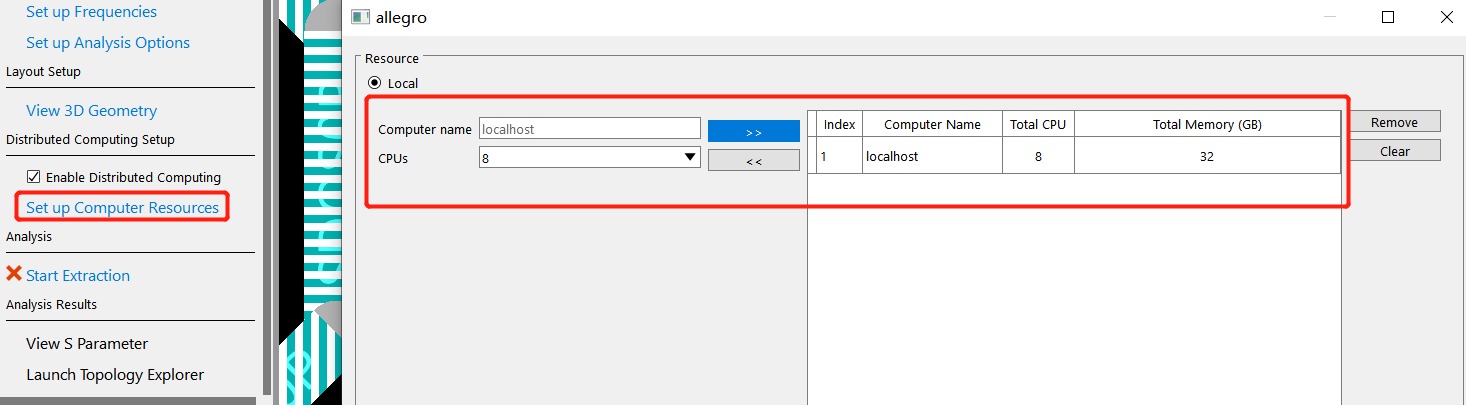

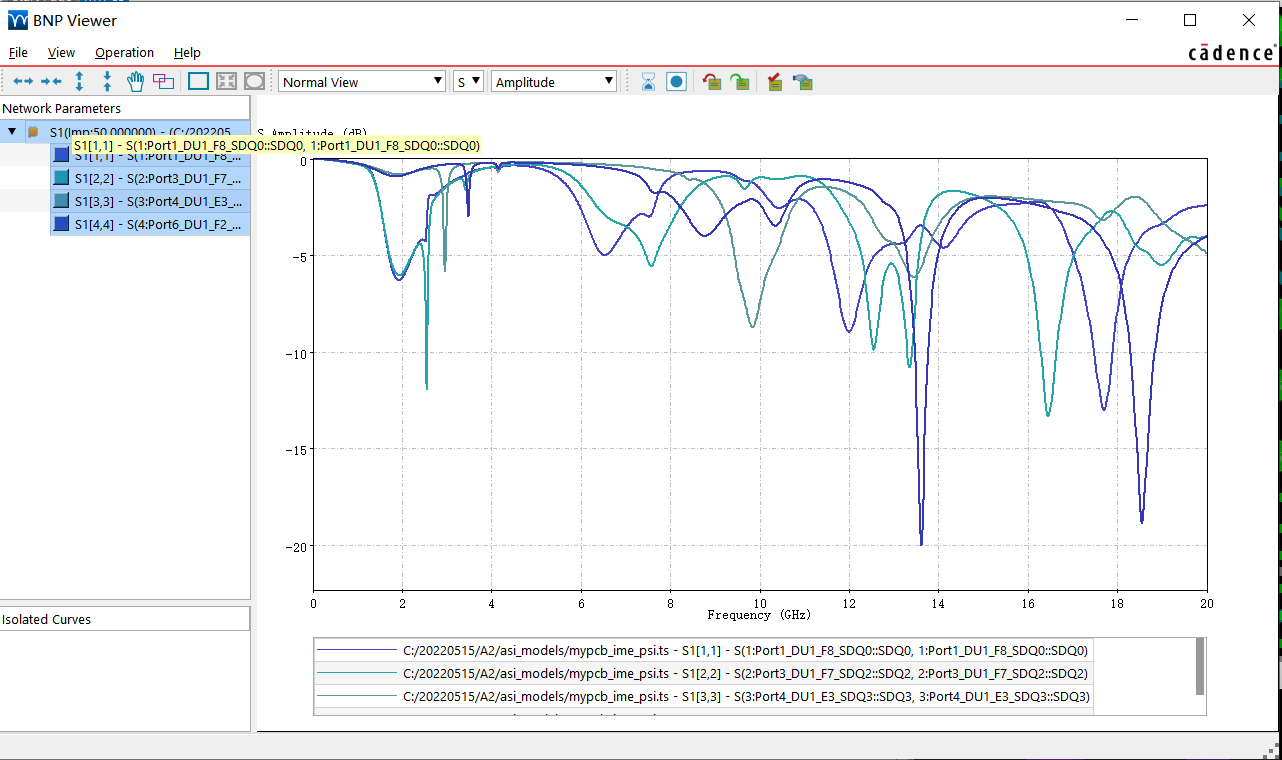

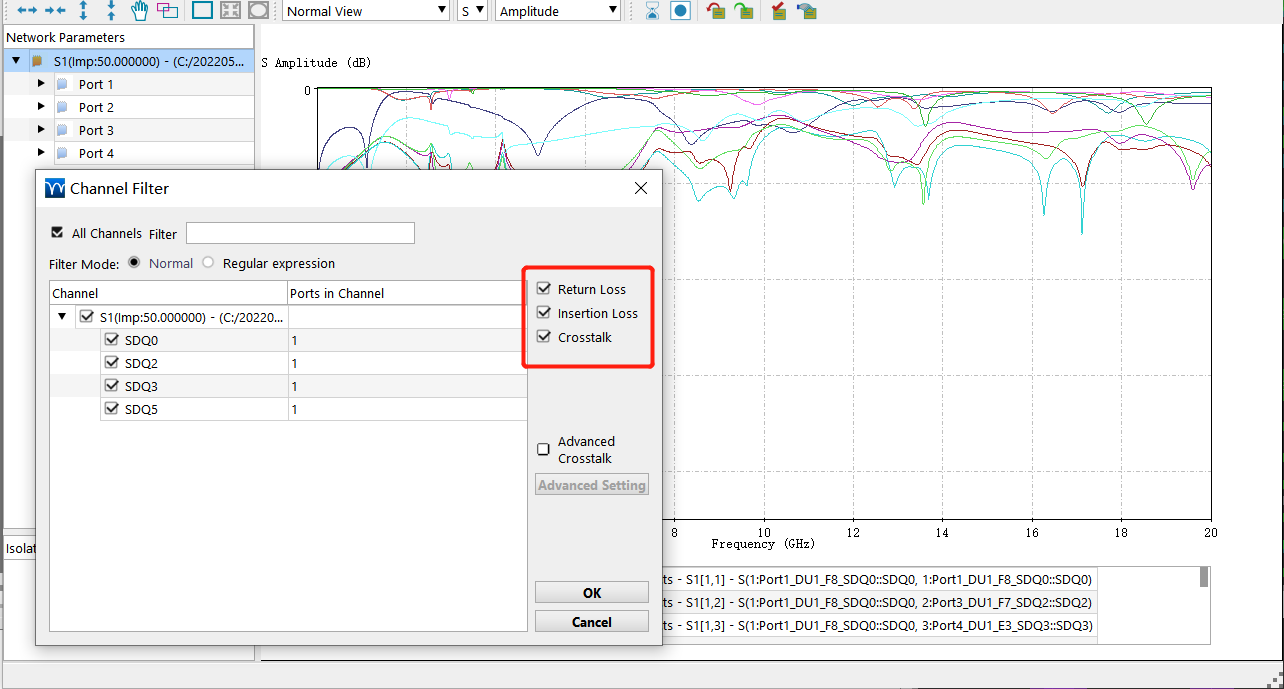

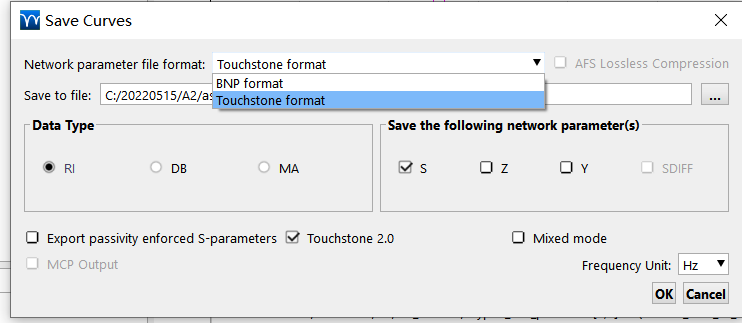

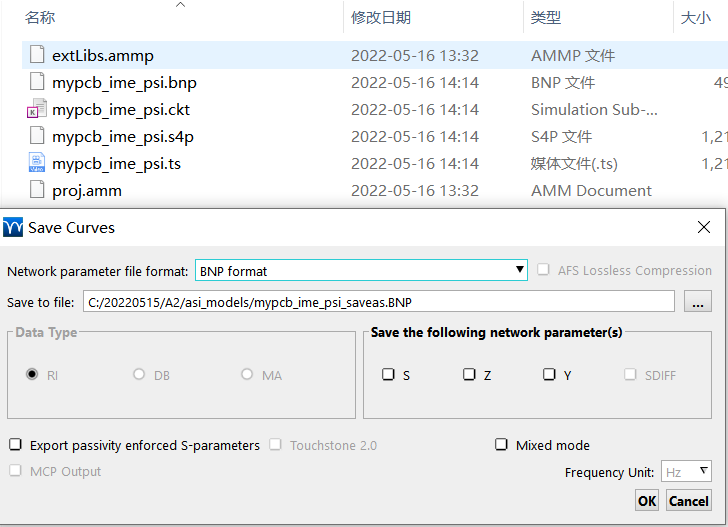

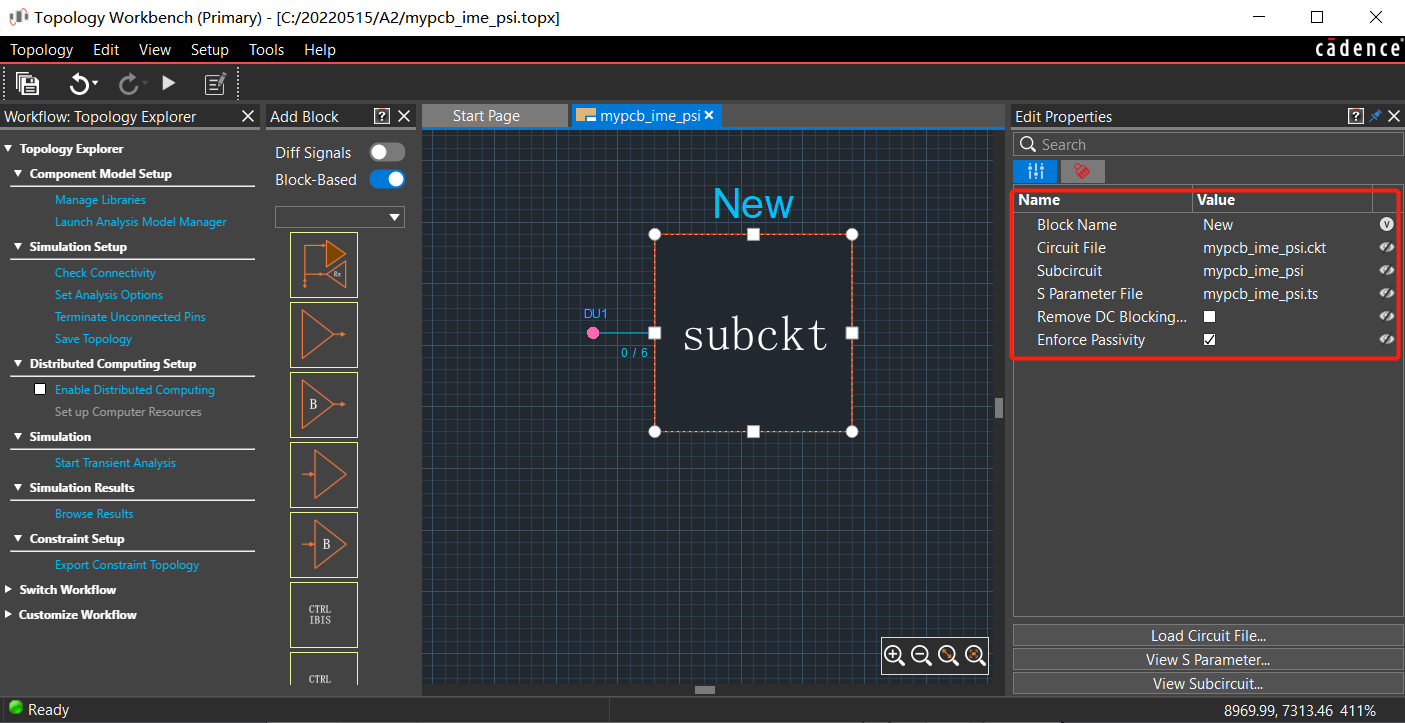

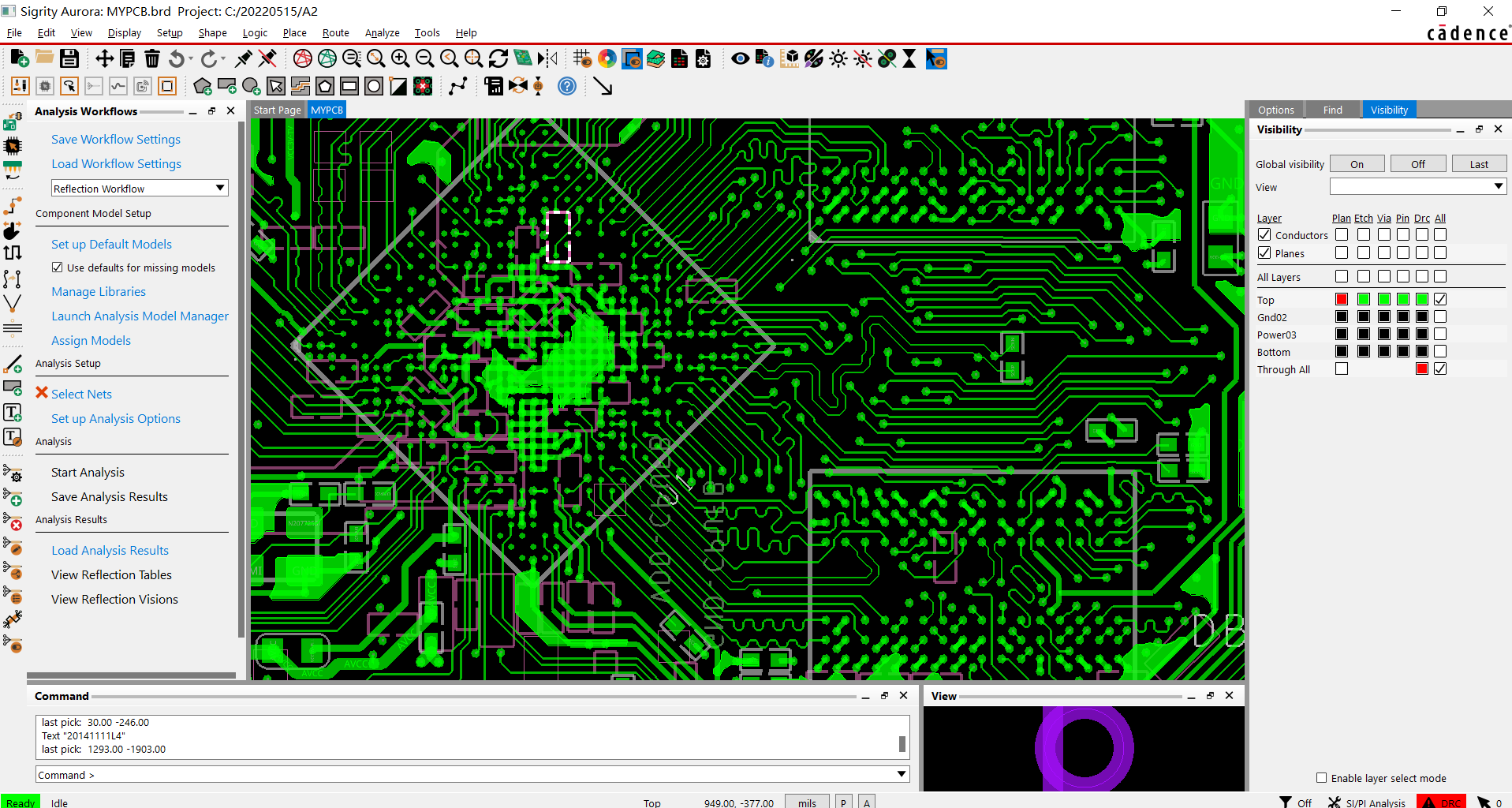

Aurora_TopWbench_SPB17.4 更新之后,Clarity 3D Solver 和 Sigrity PowerSI 引擎直接集成到 Allegro 环境中,可以通过选择需要提取的网络调用 Clarity3D Solver 和 Sigrity PowerSI 引擎进行 S参数 的仿真建模。

接下来我们使用一个实例文件来讲解 S参数 的仿真建模方法。