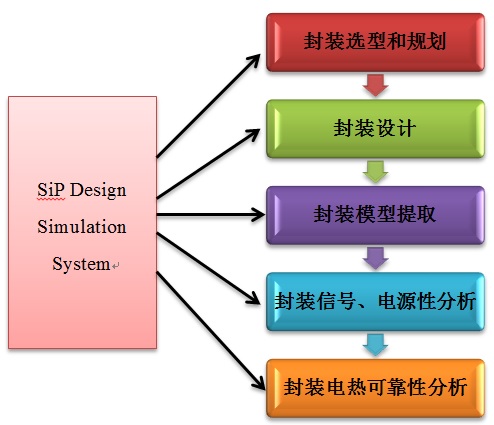

Cadence Allegro SiP Layout

封装基板布局布线工具,该工具可以完成从简单到复杂不同层次的基板设计,能完成多管脚、高密度、多芯片堆叠、三维封装等复杂的封装设计,还提供多重腔休、复杂形状封装形式的支持。支持所有的封装类型,包括陶瓷封装、PGA、BGA、CSP等封装类型。Cadence SiP Digital Layout为SiP设计提供了约束和规则驱动的版图环境。它包括衬底布局和布线、IC、衬底和系统级最终的连接优化、制造准备、整体设计验证和流片。该环境集成了IC/封装/I/O布局性能、三维晶粒堆叠结构生成与编辑性能。另外,完全的联机设计规则检查(DRC)可支持层压、陶瓷、及镀膜技术间各种组合的复杂和独特要求。多层倒装芯片与放射状任意角衬底布线提供了快速的约束驱动互连创建。

功能优点 :

- 提供三维晶粒堆栈创建/编辑,以进行快速堆栈装配与优化。

- 实现IC、衬底与系统级IC的I/O填补环/阵列协同设计与连接优化。

- 允许IC和衬底间的互连分配和优化,以达到基于信号完整性和可布线性的最优/最少层使用。

- 通过倒装芯片晶粒自动布线-破孔,减少冗长乏味的、耗时的人工破孔编辑。

- 约束导向的HDI设计,使用自动辅助互动布线,加快实行并减少潜在的错误。

- 包括全面的衬底DFM性能,以获得快速设计制造准备。

- 提供三维设计查看器和DRC,以获得精确的全三维键合壳验证、设计复审纠错、以及装配测试设计文件。

- 团队式设计分割,缩短设计周期时间并优化设计师资源。

功能描述:

1. 多种连接方式与灵活封装形式的支持

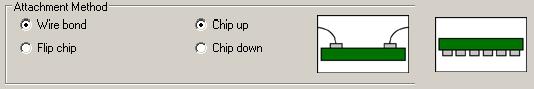

- 支持多种封装工艺如:金丝压焊、周边阵列倒装芯片、以及堆栈式多硅芯片封装。

- 支持多种组建连接方式:WireBond、Flip-Chip等组件连接方式。

- 灵活支持RF电路和高速数字电路兼容于同一封装。

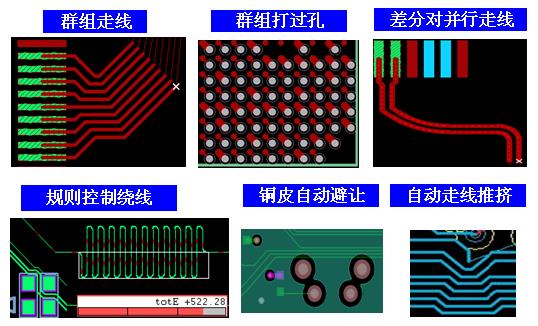

2. 强大的布局布线能力

- SiP Layout完美驱动布局布线可实现全自动的复杂的布线要求,成熟的技术,庞大的用户群,有利于设计人员的快速上手。

- Bonding线的灵活扇出方式和自动推挤。

3. 规则驱动设计方法

约束驱动作为基板版图设计的灵魂,在SiP Layout封装设计中也得到了充分的体现。越来越复杂的基板设计是传统CAD工具和布线工具难以完成的, SiP Layout从原理图开始就嵌入了约束管理器器,可以方便的定义衬底布局布线的约束要求,诸如线宽、间距、线路阻抗、传输延时、差分线、阻抗匹配等的设定,针对基板上的RF信号和高速数字信号时钟,SiP Layout的约束驱动功能可以有效的保证时序的正确性。

4. 封装设计3D查看与验证

为了提高功能密度,SiP Layout设计在封装内采用了复杂的三维(3D)架构。包括堆叠金属线压焊裸片、堆叠在倒装芯片裸片上的金属线压焊裸片、裸片之间直接连BONDING线、使用媒介基板、以及包括堆叠封装(PoP)、嵌入式封装在内的其它复杂组合。

- 3D堆叠方式预览很好的帮助设计师或制造商理解层叠的堆叠方式。

- 支持完整个设计预览或特定对象预览,例如晶粒堆栈或复杂的导孔阵列。

- 辅助检查DFM问题,验证产品的可靠性,从而设计问题,DFM工艺问题发现在设计前端。

Sigrity XtractIM封装基板仿真模型参数提取工具

XtractIM 是一款专门针对IC封装的宽带模型提取及封装性能评估工具。XtractIM能够生成标准的IBIS格式和SPICE子电路格式的封装模型。提取出的模型可以是各引脚或各网络的RLC网表,可以是带耦合参数的矩阵,也可以是Pi/T型SPICE子电路。XtractIM生成的模型可以用来评估封装模型电性能的好坏,也可用于系统级的SI和PI的仿真。XtractIM除了比其他类似的工具仿真速度快很多之外,得到的封装模型还具有更高的精度和更宽的频带。XtractIM还可以提供基于信号和电源地的封装电气性能评估,帮助客户快速检查封装电气性能、定位设计缺陷,避免设计风险。

Sigrity Speed2000封装信号完整性分析工具

Speed2000是一款针对IC封装进行时域瞬态仿真的通用分析软件。软件采用电路求解器、传输线求解器、三维电磁场求解器可以根据IC封装的不同结构,快速而准确的分析出复杂结构内部的动态电磁效应。Speed2000真实地再现实际系统中的电源地网络,考虑芯片封装中的各种电磁效应,包括封装基板内电源地之间的波动(同步开关噪声),过孔和走线之间的耦合,以及电路和封装间的交互作用。

Sigrity PowerSI/3D-EM封装电源完整性分析工具

PowerSI可以为先进的集成电路(IC)封装供快速、准确的全波电磁分析。PowerSI对电子系统在频域中进行分析,非常适用于对集成电路的封装进行整体电磁分析。PowerSI使用了Sigrity独特的专利分析技术,在对芯片堆叠,三维键合线,基板平面上的分割、槽,多层电源/地结构,大量的通孔和走线等具体结构并在提取精确模型时使用了自适应的数值网格技术。- 业界唯一的仿真引擎自动去检测优化高密过孔算法,大大提高了仿真的精度。 - 支持从0Hz开始的全频模型段S/Y/Z网络参数提取,并通过强制S参数因果性和无源性选项,改善时域仿真结果的收敛性;自适应扫频方式,增强的低频仿真精度。- 电源网络和地网络当作非理想的情况来处理,考虑的是非理想的信号返回路径,准确提取SSN等复杂SI/PI问题。- 提取芯片封装级电源网络与信号网络的阻抗(Z)参数及散射(S)参数,找出关键的谐振频率点分布,为精确分析电源和信号的性能提供依据。- 先进的3DFEM算法提供了优秀的仿真精度,同时具备10倍于同类的产品卓越仿真效率。- 先进的高频及低频算法,确保高频精度的同时,在低频精度上大大领先于同类产品。- 同类产品中唯一集成混合仿真引擎,支持SPICE电路模型。- 支持各种单Die和多Die的封装结构,还可以模拟出封装结构中电场和磁场的强度分布。- 支持任意几何结构的剪切,可以用于简化加快超大规模电路的仿真,或者用于快速仿真局部区域的特性。- 全流程化的操作界面,软件界面自带仿真flow,用户只需根据界面提示就可轻松完成仿真任务。

Sigrity PowerDC封装电热协同仿真分析工具

PowerDC能对芯片封装提供快速准确的直流分析和电热应力协同分析。PowerDC提供了一个step-by-step的工作流程来发现隐含的直流压降问题、电流密度问题、热可靠性问题。这些问题可能导致系统故障并带来额外的产品成本。PowerDC能够快速的给出分析结果,同时带有感应线优化和DRC检查等高级功能。分析结果可以导出用于其他相关分析。

Sigrity T2B模型转换工具

T2B是实现晶体管级模型(SPICE)到行为级模型(IBIS)的转换工具。