文档中心

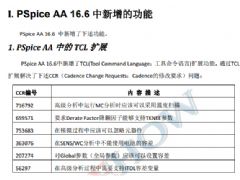

What's new in PSpice A/D 16.6

OrCAD Capture CIS

Orcad Capture CIS/ Allegro Design Entry CIS 16.6新增功能列表,如下,具体内容及相关操作见技术白皮书。

1. 在Capture下运行SigXplorer进行信号完整性分析

2. 从菜单中放置PSpice元件

3. 配置菜单和工具栏

4. 设计和库文件保存功能的扩展

5. 查找功能的扩展

6. NetGroup使用模型的升级

7. 查询并替换Off-Page Connector(端口连接符)

8. Cache更新扩展

9. 为元器件设置 User Assigned Flag.

10. 实现同一个设计中不同层次电路图的自动顺序编号

11. 数据库压缩与处理能力的增强

12. 打开由低版本软件生成的设计文件

13. 关闭所有标签页

14. DRC功能扩展

15. Project SaveAs功能的扩展

16. 学习资料

II. Capture 16.6中已经解决的重要问题

1、CCR 1065649: 兼容16.5和16.3版本问题

2、CCR 730224:对库文件进行了更新但没有更新信息

3、CCR 724738:Update/Replace Cache对用户定义的引脚形状无效

What's new in Allegro PCB 16.6

OrCAD 16.6 Lite Download

本的OrCAD 16.6精简版软件将让你体验所有功能和功能实际的软件*。这样继续下去,发现它是多么容易使用国家的最先进的这些的OrCAD PCB设计技术。

的OrCAD 16.6精简版软件包括以下工具的演示版本:的OrCAD捕获,Cadence的OrCAD Capture CIS附加选项,PSpice的A / D转换, Cadence公司的PSpice高级分析,的OrCAD PCB编辑器,和Cadence SPECCTRA®专为OrCAD。16.6版本在Windows 7 32位和64位系统,包括适用于Windows的UAC(用户访问控制)限制,支持完全支持。

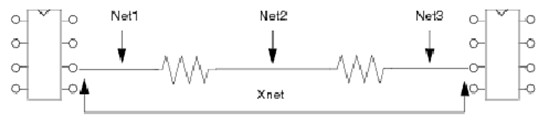

Allegro高级教程之基于Xnet的网络等长设置

由无源、分立器件(电阻、电容、电感)连接起来的几段网络的组合称为Xnet,如图:

本文介绍在Allegro中如何创建一组Xnet并设置这组Xnet等长。

关键字:高速电路、网络等长设置、XNET、XNET等长、传输延迟、Allegro线长控制

数据转换之Altium Designer原理图到OrCAD Capture的转换-

Allegro基础教程之PCB外形尺寸标注模块介绍

Allegro允许用户进行多种类型尺寸的标注,例如线性标注、角度标注、直径/半径标注、元件次序标注等。本文就Allegro的尺寸标注环境做系统介绍。

关键字:Cadence教程、Allegro教程、Allegro PCB、Allegro技术专题、尺寸标注

Allegro基础教程之Allegro后处理方法之Thieving功能介绍

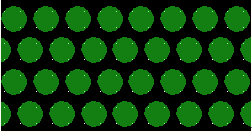

Thieving是指在PCB设计中添加覆铜点或取样点的操作技术,是为了保持PCB在电镀时板上各点镀铜厚度均匀,避免该区域铜箔过度电镀的情况发生。

添加的取样点以过孔形式表示,执行Thieving命令后,软件自动添加取样点,如图:

关键字:Cadence教程、Allegro教程、Allegro PCB、PCB设计、thieving