Sigrity SystemSI 可以对高速串行通道进行眼图和误码率分析,对系统中的任意参数进行扫描,得到最优化配置,并且集成了 PCI-E、SATA 等工业标准,直接对仿真结果进行判别。

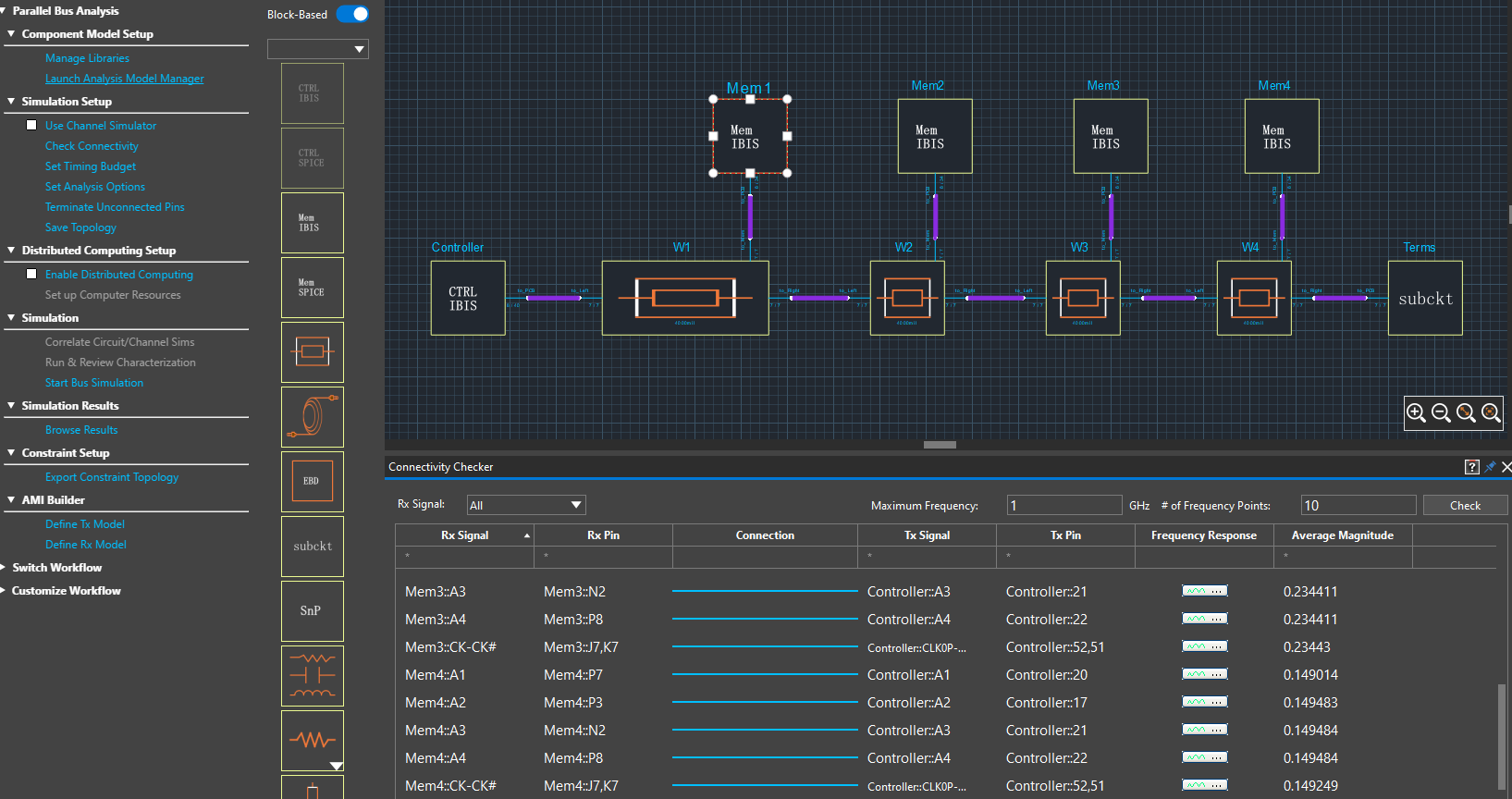

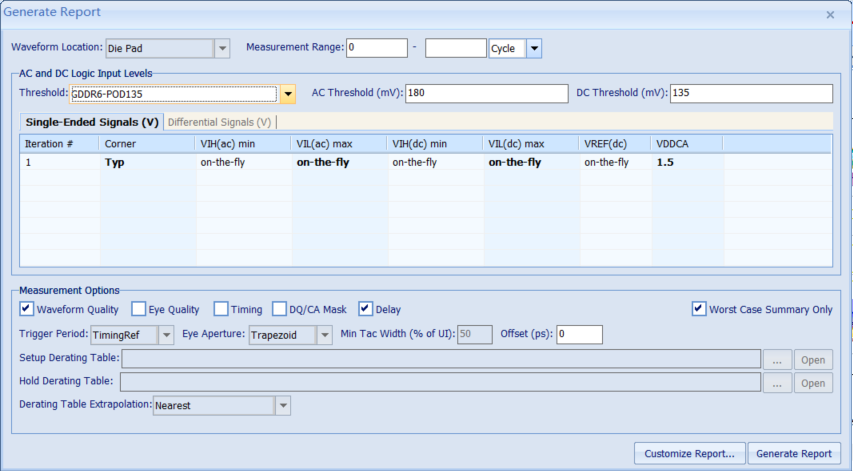

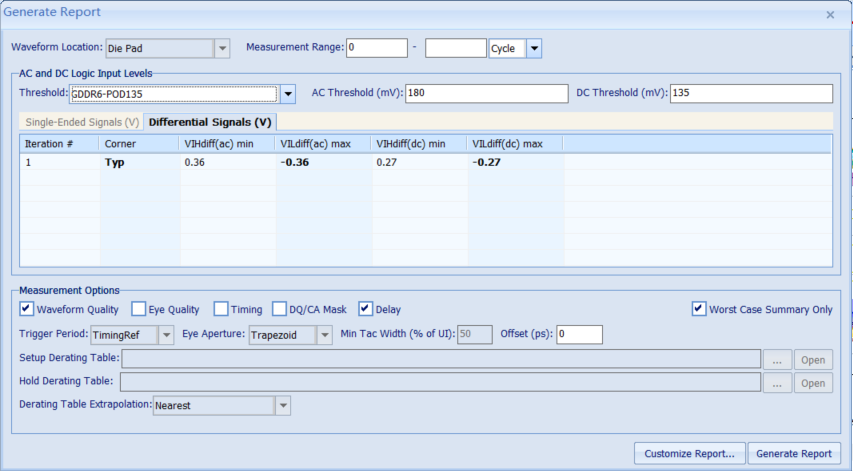

Sigrity SystemSI 可以对整个 DDR 系统进行准确的 SSN 分析,集成 JEDEC 标准,自动为用户量测 SI 参数,并以此为基础,进行自动化时序分析。

Sigrity SystemSI 的高速串行和并行模块,可以适应高速信号传输通道的标准分析流程,支持 AMI 算法建模接口,能够更高效地创建发送端和接收端模型,同时内部的参数定义方式将芯片设计和业界高速传输标准(DDR/HDMI/USB/PCI-E等)以流程化的方式提供给用户,最终满足用户对系统总体 BER 的预测,并判断抖动、噪声是否都在指定的容限内,实现更简单易用的流程化操作。

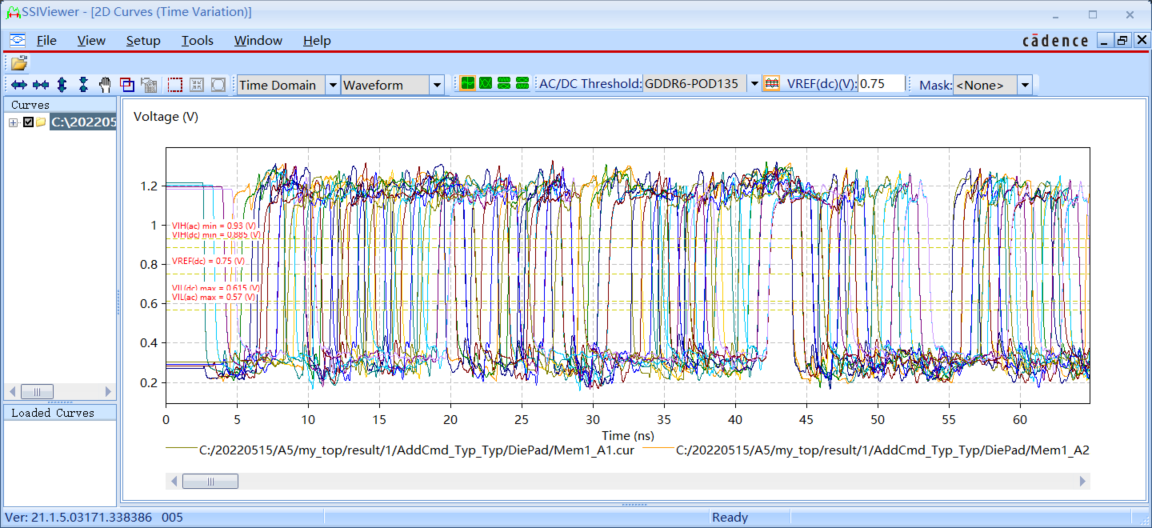

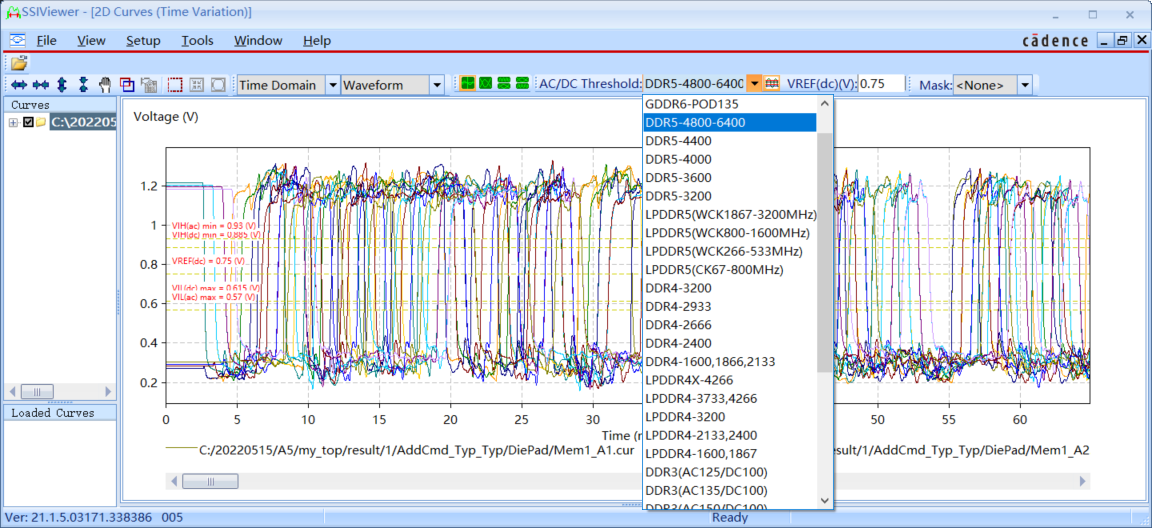

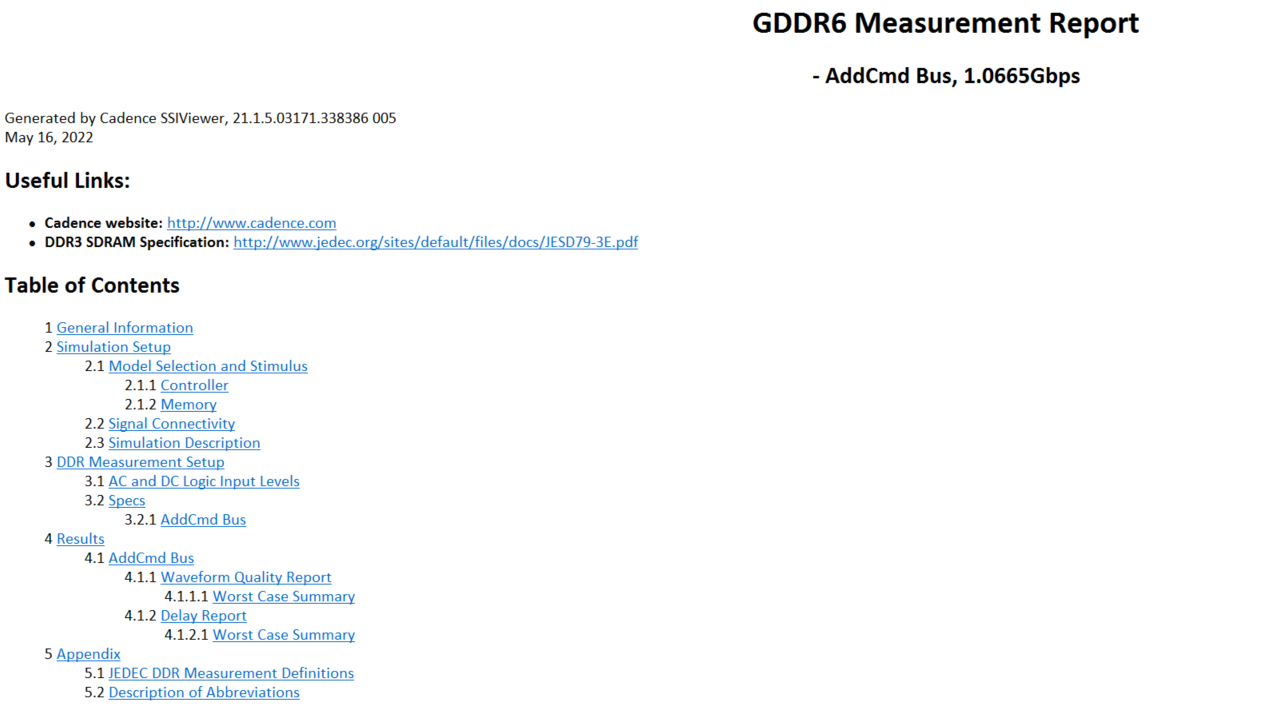

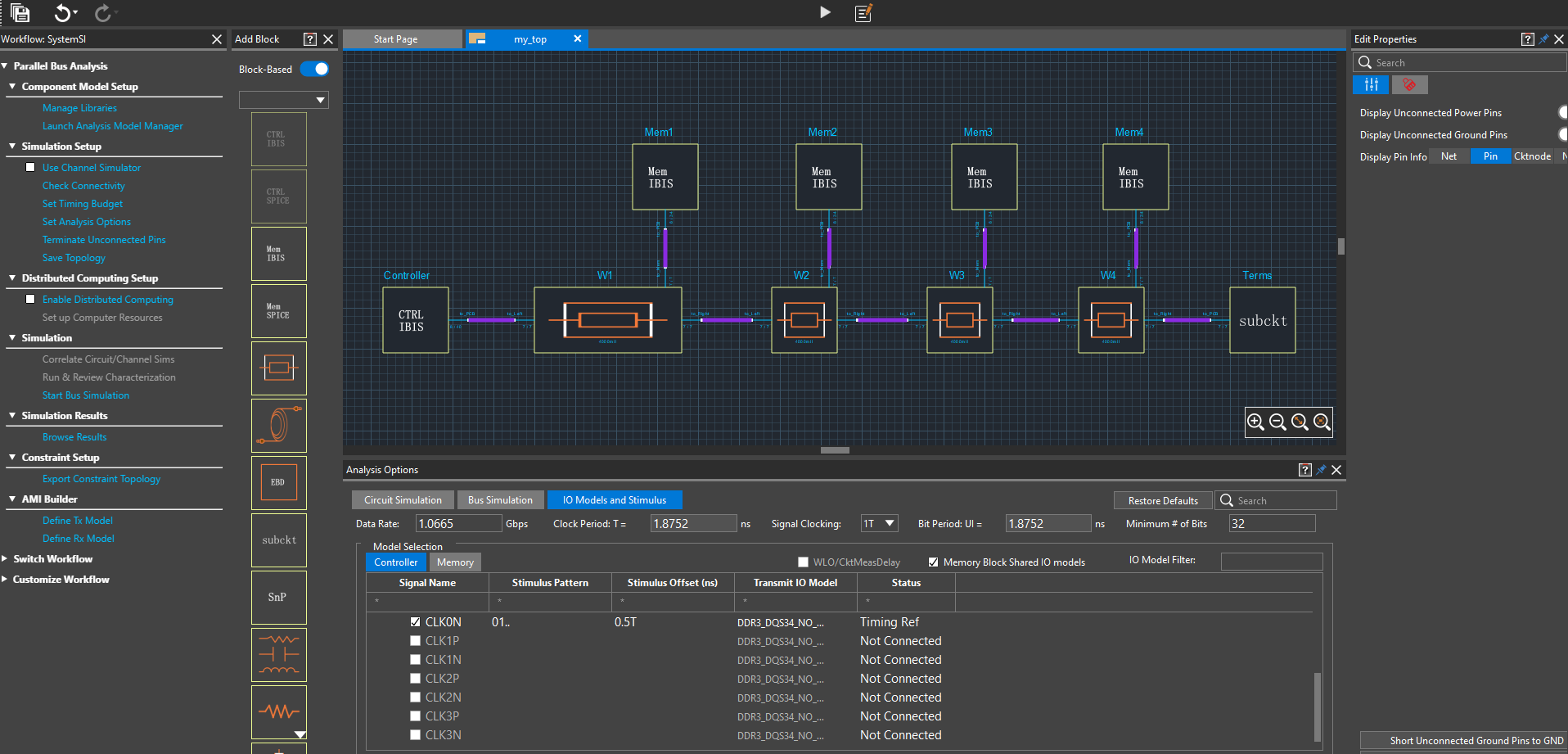

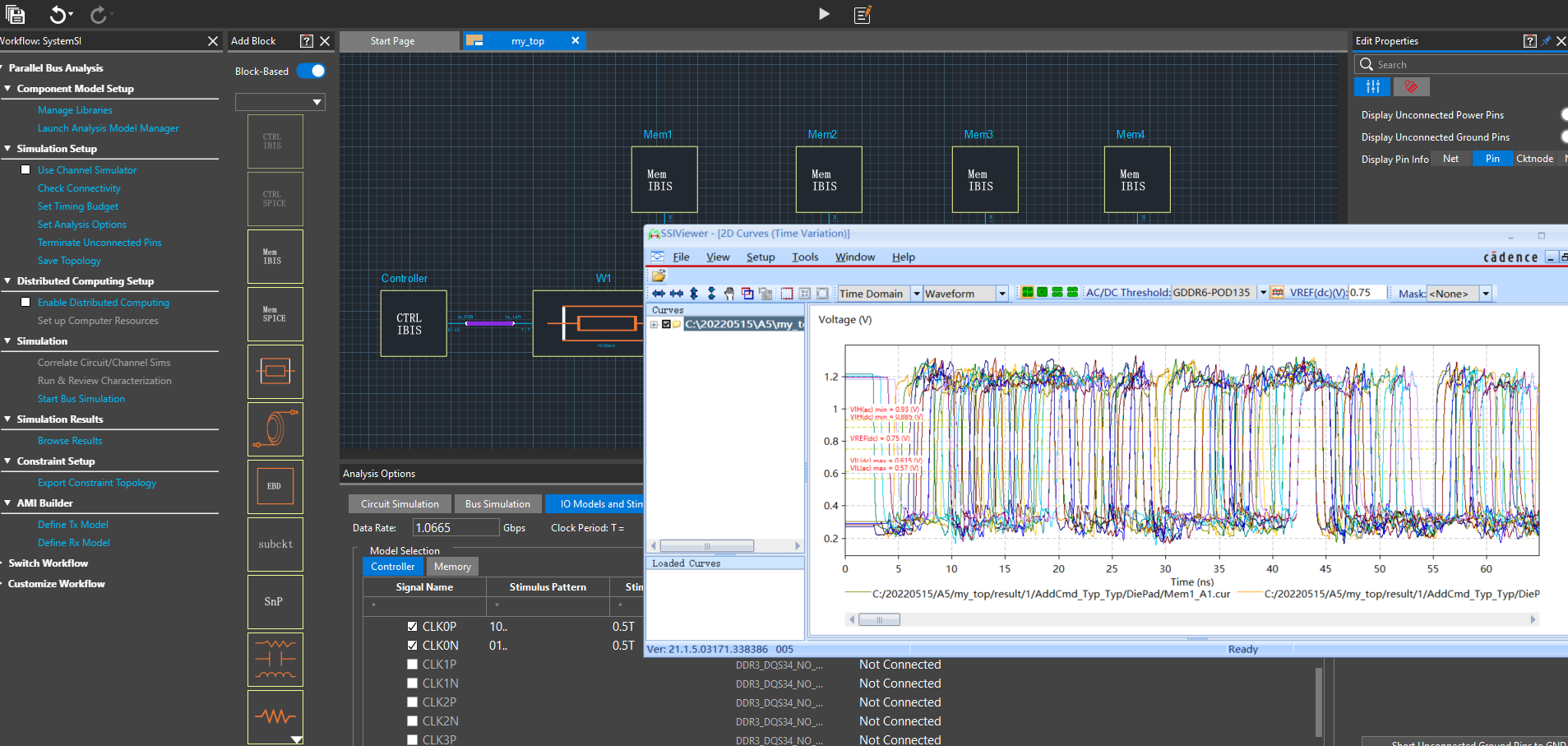

2# 为GDDR6 接口增加基于 JEDEC 自动化分析功能

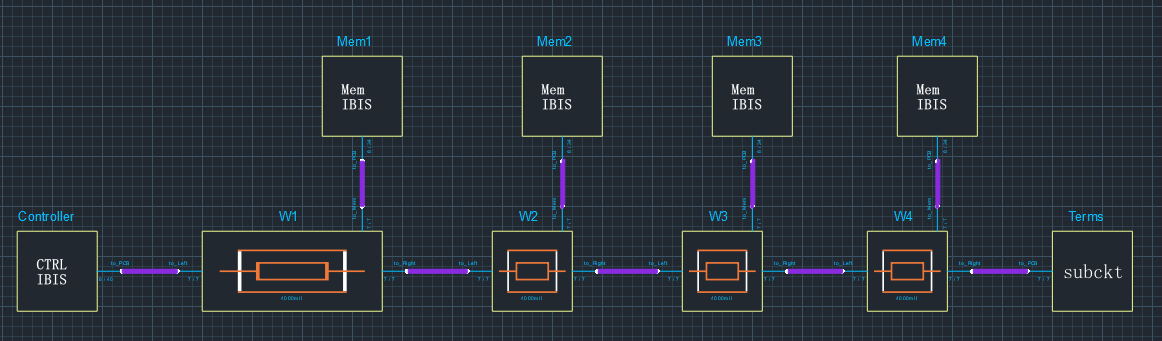

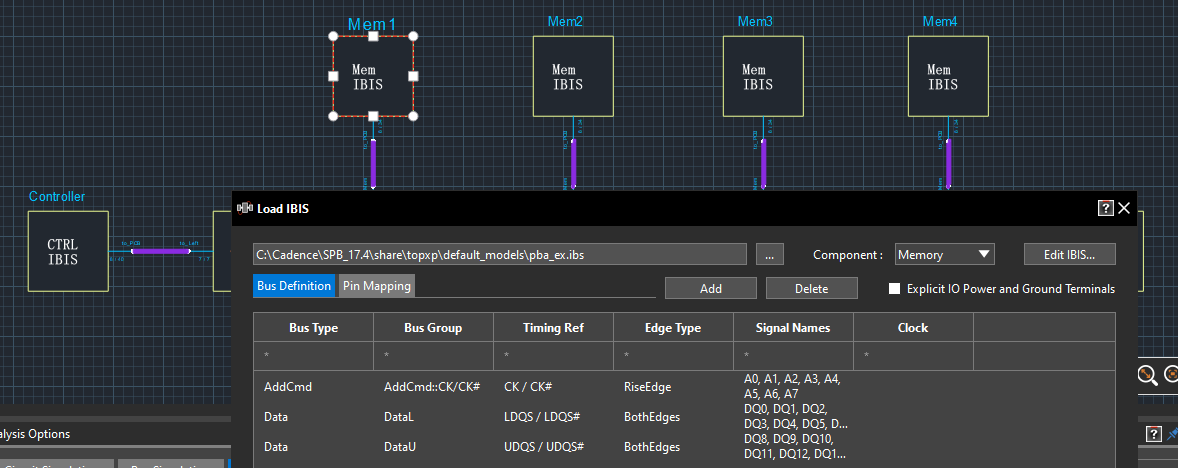

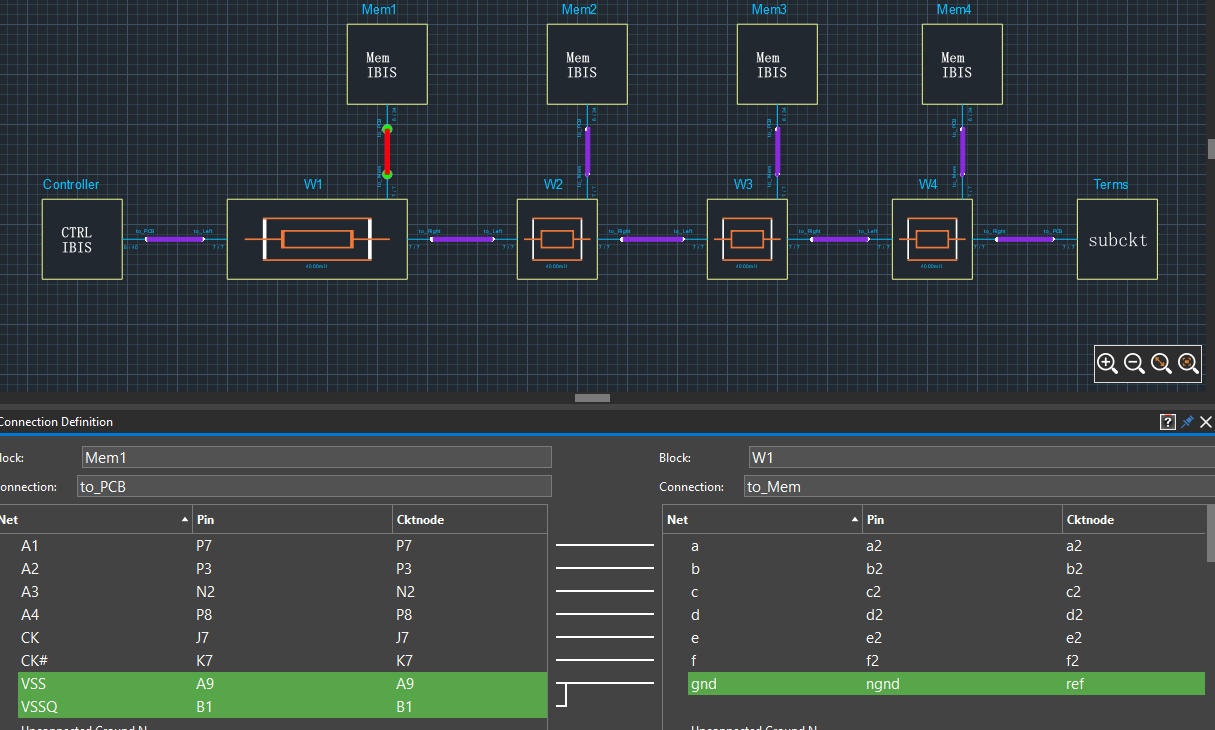

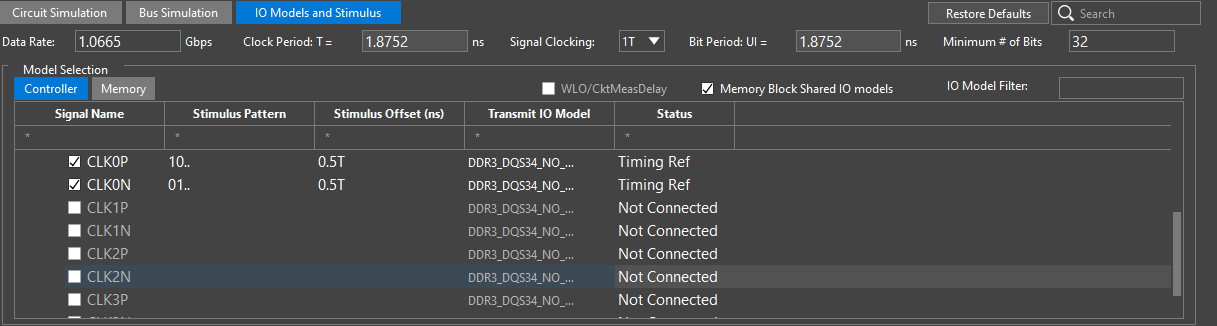

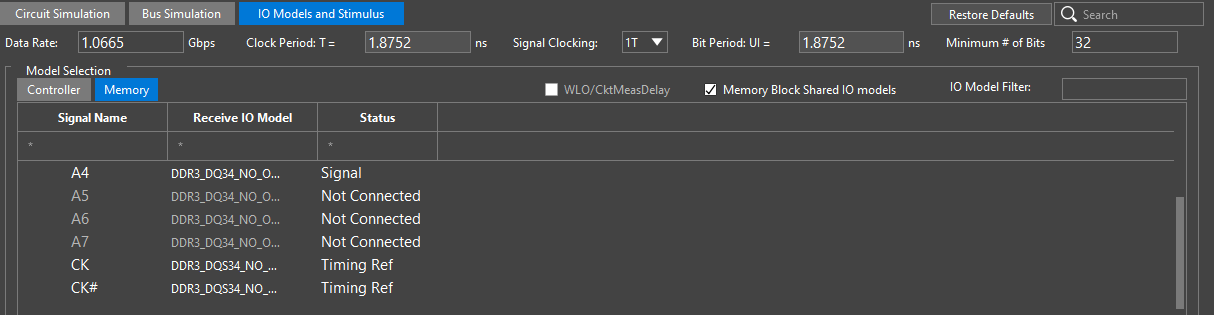

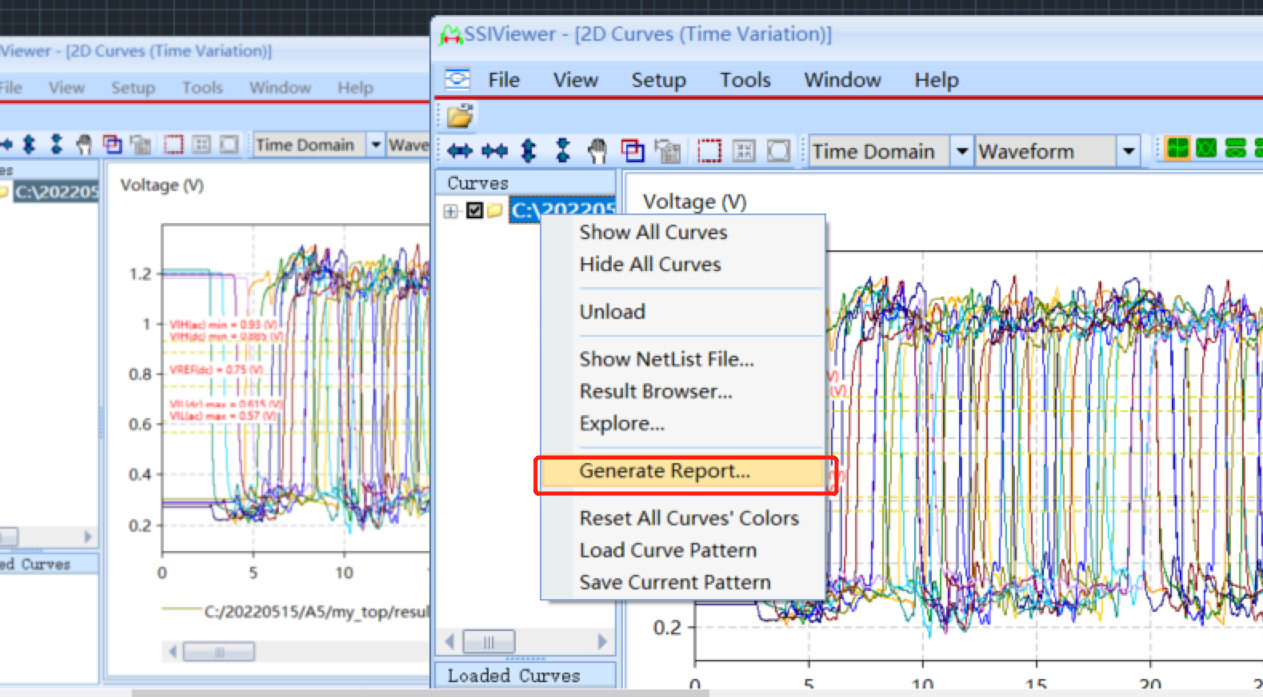

Wbench_SPB17.4_QIR4 更新之后,Sigrity SystemSI 可以支持为 GDDR6 接口增加基于 JEDEC 协议的自动化分析功能。接下来使用一个 DDR 的例子来说明 GDDR6 分析流程及内存块支持多个模型等功能。